Hardware-Tutorial

Hardware-Tutorial

Hardware-Neuigkeiten

Hardware-Neuigkeiten

Die Speicherspezifikationen DDR5 MRDIMM und LPDDR6 CAMM stehen zur Markteinführung bereit, JEDEC veröffentlicht wichtige technische Details

Die Speicherspezifikationen DDR5 MRDIMM und LPDDR6 CAMM stehen zur Markteinführung bereit, JEDEC veröffentlicht wichtige technische Details

Die Speicherspezifikationen DDR5 MRDIMM und LPDDR6 CAMM stehen zur Markteinführung bereit, JEDEC veröffentlicht wichtige technische Details

Diese Seite berichtete am 23. Juli, dass der Mikroelektronik-Standardsetzer JEDEC Solid State Technology Association am 22. Ortszeit bekannt gab, dass die technischen Spezifikationen für DDR5 MRDIMM- und LPDDR6 CAMM-Speicher bald offiziell eingeführt werden, und stellte die wichtigsten Details dieser beiden Speicher vor.

Das „MR“ in DDR5 MRDIMM steht für Multiplexed Rank, was bedeutet, dass der Speicher zwei oder mehr Ranks unterstützt und mehrere Datensignale auf einem einzigen Kanal kombinieren und übertragen kann. Die Bandbreite kann effektiv erhöht werden, ohne dass zusätzliche physische Verbindungen erforderlich sind.

JEDEC hat mehrere Generationen von DDR5-MRDIMM-Speichern geplant, mit dem Ziel, die Bandbreite schließlich auf 12,8 Gbit/s zu erhöhen und damit die aktuellen 6,4 Gbit/s des DDR5-RDIMM-Speichers zu verdoppeln.

In der Vision von JEDEC wird DDR5 MRDIMM die gleichen Pin-, SPD-, PMIC- usw. Designs wie bestehende DDR5-DIMMs verwenden, mit der RDIMM-Plattform kompatibel sein und das bestehende LRDIMM-Ökosystem für Design und Tests nutzen.

Darüber hinaus hat JEDEC auch den Tall MRDIMM-Formfaktor geplant. Wie der Name schon sagt, wird das Design über einen höheren Formfaktor verfügen, der die Anzahl der unterstützten DRAM-Pakete verdoppelt und so die Speicherkapazität weiter erhöht.

Was LPDDR6 CAMM betrifft, sagte JEDEC, dass es voraussichtlich eine maximale Geschwindigkeit von mehr als 14,4 GT/s erreichen wird, und erwähnt auch 24-Bit-breites Sub -Kanal, 48-Bit-Wide-Kanal und unterstützt „Connector-Array“ (Hinweis von dieser Site: Der Originaltext ist Connector-Array).

Das obige ist der detaillierte Inhalt vonDie Speicherspezifikationen DDR5 MRDIMM und LPDDR6 CAMM stehen zur Markteinführung bereit, JEDEC veröffentlicht wichtige technische Details. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!

Heiße KI -Werkzeuge

Undresser.AI Undress

KI-gestützte App zum Erstellen realistischer Aktfotos

AI Clothes Remover

Online-KI-Tool zum Entfernen von Kleidung aus Fotos.

Undress AI Tool

Ausziehbilder kostenlos

Clothoff.io

KI-Kleiderentferner

AI Hentai Generator

Erstellen Sie kostenlos Ai Hentai.

Heißer Artikel

Heiße Werkzeuge

Notepad++7.3.1

Einfach zu bedienender und kostenloser Code-Editor

SublimeText3 chinesische Version

Chinesische Version, sehr einfach zu bedienen

Senden Sie Studio 13.0.1

Leistungsstarke integrierte PHP-Entwicklungsumgebung

Dreamweaver CS6

Visuelle Webentwicklungstools

SublimeText3 Mac-Version

Codebearbeitungssoftware auf Gottesniveau (SublimeText3)

Heiße Themen

Der Drucker hat nicht genügend Speicher und kann die Seite nicht drucken. Excel- oder PowerPoint-Fehler

Feb 19, 2024 pm 05:45 PM

Der Drucker hat nicht genügend Speicher und kann die Seite nicht drucken. Excel- oder PowerPoint-Fehler

Feb 19, 2024 pm 05:45 PM

Der Drucker hat nicht genügend Speicher und kann die Seite nicht drucken. Excel- oder PowerPoint-Fehler

Optimierung des großen Speichers. Was soll ich tun, wenn der Computer auf 16g/32g Speichergeschwindigkeit aktualisiert wird und es keine Änderung gibt?

Jun 18, 2024 pm 06:51 PM

Optimierung des großen Speichers. Was soll ich tun, wenn der Computer auf 16g/32g Speichergeschwindigkeit aktualisiert wird und es keine Änderung gibt?

Jun 18, 2024 pm 06:51 PM

Optimierung des großen Speichers. Was soll ich tun, wenn der Computer auf 16g/32g Speichergeschwindigkeit aktualisiert wird und es keine Änderung gibt?

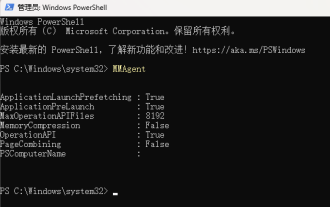

![Bei Windows-Eingaben kommt es zu Hängenbleiben oder hoher Speicherauslastung [Fix]](https://img.php.cn/upload/article/000/887/227/170835409686241.jpg?x-oss-process=image/resize,m_fill,h_207,w_330) Bei Windows-Eingaben kommt es zu Hängenbleiben oder hoher Speicherauslastung [Fix]

Feb 19, 2024 pm 10:48 PM

Bei Windows-Eingaben kommt es zu Hängenbleiben oder hoher Speicherauslastung [Fix]

Feb 19, 2024 pm 10:48 PM

Bei Windows-Eingaben kommt es zu Hängenbleiben oder hoher Speicherauslastung [Fix]

Gibt es einen großen Unterschied zwischen 8g- und 16g-Speicher in Computern? (Wählen Sie 8 g oder 16 g Computerspeicher)

Mar 13, 2024 pm 06:10 PM

Gibt es einen großen Unterschied zwischen 8g- und 16g-Speicher in Computern? (Wählen Sie 8 g oder 16 g Computerspeicher)

Mar 13, 2024 pm 06:10 PM

Gibt es einen großen Unterschied zwischen 8g- und 16g-Speicher in Computern? (Wählen Sie 8 g oder 16 g Computerspeicher)

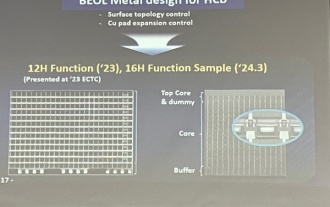

Samsung gab den Abschluss der Verifizierung der 16-Layer-Hybrid-Bonding-Stacking-Prozesstechnologie bekannt, die voraussichtlich in großem Umfang im HBM4-Speicher zum Einsatz kommen wird

Apr 07, 2024 pm 09:19 PM

Samsung gab den Abschluss der Verifizierung der 16-Layer-Hybrid-Bonding-Stacking-Prozesstechnologie bekannt, die voraussichtlich in großem Umfang im HBM4-Speicher zum Einsatz kommen wird

Apr 07, 2024 pm 09:19 PM

Samsung gab den Abschluss der Verifizierung der 16-Layer-Hybrid-Bonding-Stacking-Prozesstechnologie bekannt, die voraussichtlich in großem Umfang im HBM4-Speicher zum Einsatz kommen wird

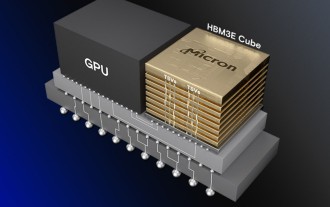

Micron: HBM-Speicher verbrauchen das Dreifache des Wafervolumens und die Produktionskapazität ist grundsätzlich für nächstes Jahr gebucht

Mar 22, 2024 pm 08:16 PM

Micron: HBM-Speicher verbrauchen das Dreifache des Wafervolumens und die Produktionskapazität ist grundsätzlich für nächstes Jahr gebucht

Mar 22, 2024 pm 08:16 PM

Micron: HBM-Speicher verbrauchen das Dreifache des Wafervolumens und die Produktionskapazität ist grundsätzlich für nächstes Jahr gebucht

Lexar bringt Ares Wings of War DDR5 7600 16 GB x2-Speicherkit auf den Markt: Hynix A-Die-Partikel, 1.299 Yuan

May 07, 2024 am 08:13 AM

Lexar bringt Ares Wings of War DDR5 7600 16 GB x2-Speicherkit auf den Markt: Hynix A-Die-Partikel, 1.299 Yuan

May 07, 2024 am 08:13 AM

Lexar bringt Ares Wings of War DDR5 7600 16 GB x2-Speicherkit auf den Markt: Hynix A-Die-Partikel, 1.299 Yuan