Java

Java

javaLernprogramm

javaLernprogramm

Detaillierte Einführung in das Implementierungsprinzip von Volatile in Java mit hoher Parallelität

Detaillierte Einführung in das Implementierungsprinzip von Volatile in Java mit hoher Parallelität

Detaillierte Einführung in das Implementierungsprinzip von Volatile in Java mit hoher Parallelität

In diesem Artikel werden hauptsächlich relevante Informationen zum Implementierungsprinzip von Volatile in Java vorgestellt. Bei der Multithread-Parallelität spielen sowohl synchronisiert als auch Volatile eine wichtige Rolle „Sichtbarkeit“ von gemeinsam genutzten Variablen in der Multiprozessorentwicklung. Freunde, die dies benötigen, können sich auf das

Implementierungsprinzip von Volatile in Java High Concurrency

Zusammenfassung: Sowohl synchronisiert als auch flüchtig spielen eine wichtige Rolle in der gleichzeitigen Multithread-Programmierung. Volatile ist ein leichtgewichtiges synchronisiertes System, das die gemeinsame Nutzung von Variablen in der Multiprozessorentwicklung gewährleistet. Sichtbarkeit bedeutet, dass ein anderer Thread den geänderten Wert lesen kann, wenn ein Thread eine gemeinsam genutzte Variable ändert. Es hat in einigen Fällen weniger Overhead als synchronisiert

Java

Programmierspracheermöglicht Threads den Zugriff auf Shares-Variablen, Um sicherzustellen, dass gemeinsam genutzte Variablen genau und konsistent aktualisiert werden können, sollten Threads sicherstellen, dass diese Variable individuell durch eine exklusive Sperre erfasst wird. Die Java-Sprache bietet flüchtige Funktionen, was in manchen Situationen praktischer ist als Sperren. Wenn ein Feld als flüchtig deklariert ist, stellt das Java-Thread-Speicher--Modell sicher, dass alle Threads den gleichen Wert dieser Variablen sehen

2. Prinzip der flüchtigen ImplementierungWie sorgt Volatile also für Sichtbarkeit? Verwenden Sie unter dem x86-Prozessor Tools, um die vom JIT-Compiler generierten Assembleranweisungen abzurufen und zu sehen, was die CPU beim Schreiben in Volatile tun wird.

Java-Code: Instanz = new Singleton();//Instanz ist eine flüchtige VariableAssembly-Code: 0x01a3de1d: movb $0x0,0x1104800(% esi );0x01a3de24: lock ad

dl $0x0,(%esp);Wenn eine gemeinsam genutzte Variable, die mit einer flüchtigen Variablen geändert wurde, geschrieben wird, wird eine zweite Zeile Assemblercode geschrieben hinzugefügt werden. Wenn wir das IA-32

Architecture-Softwareentwicklerhandbuch überprüfen, können wir sehen, dass die Sperrpräfixanweisung bei Mehrkernprozessoren zwei Dinge verursacht. Die Daten der Zeile

Cachedes aktuellen Prozessors werden in den Systemspeicher zurückgeschrieben. Dieser Rückschreibvorgang führt dazu, dass die an dieser Speicheradresse in anderen CPUs zwischengespeicherten Daten ungültig werden.

Um die Verarbeitungsgeschwindigkeit zu erhöhen, kommuniziert der Prozessor nicht direkt mit dem Speicher, sondern liest die Daten im Systemspeicher zunächst in den internen Cache (L1, L2 oder andere), bevor er den Vorgang ausführt , aber es weiß nicht, wann der Vorgang in den Speicher geschrieben wird. Wenn ein Schreibvorgang für eine deklarierte flüchtige Variable ausgeführt wird, sendet die JVM eine Lock-Präfixanweisung an den Prozessor, um die Daten in den Cache zu schreiben Zeile, in der sich die Variable befindet, zurück in den Systemspeicher. Aber selbst wenn es in den Speicher zurückgeschrieben wird und die von anderen Prozessoren zwischengespeicherten Werte noch alt sind, kommt es bei der Ausführung von Berechnungsvorgängen zu Problemen. Daher muss bei Multiprozessoren sichergestellt werden, dass die Caches jedes Prozessors vorhanden sind Sind konsistent, wird die Cache-Konsistenz erreicht. Jeder Prozessor prüft, ob sein zwischengespeicherter Wert abgelaufen ist, indem er die auf den Bus hochgeladenen Daten abhört Die Cache-Zeile des Prozessors wird auf den ungültigen

-Zustand gesetzt. Wenn der Prozessor diese Daten ändern möchte, wird er gezwungen, die Daten erneut aus dem Systemspeicher in den Prozessor-Cache zu lesen. Anweisungen zum Sperren von Präfixen bewirken, dass der Prozessor-Cache zurück in den Speicher geschrieben wird. Der Lock-Präfix-Befehl bewirkt, dass das LOCK#-Signal des Prozessors während der Ausführung des Befehls aktiviert wird. In einer Multiprozessorumgebung stellt das LOCK#-Signal sicher, dass der Prozessor exklusiven Zugriff auf den gemeinsam genutzten Speicher hat, während das Signal aktiviert ist. (Da dadurch der Bus gesperrt wird und andere CPUs nicht auf den Bus zugreifen können. Wenn kein Zugriff auf den Bus möglich ist, bedeutet dies, dass nicht auf den Systemspeicher zugegriffen werden kann.) Bei neueren Prozessoren sperrt das LOCK#-Signal den Bus jedoch im Allgemeinen nicht , sperrt aber den Cache. Immerhin ist der Bus-Overhead relativ groß. Die Auswirkungen von Sperrvorgängen auf den Prozessor-Cache werden in Kapitel 8.1.4 detailliert beschrieben. Bei Intel486- und Pentium-Prozessoren wird das LOCK#-Signal während Sperrvorgängen immer auf dem Bus aktiviert. Wenn jedoch bei P6- und neueren Prozessoren der Speicherbereich, auf den zugegriffen wird, bereits im Prozessor zwischengespeichert ist, wird das LOCK#-Signal nicht aktiviert. Stattdessen wird der Cache dieses Speicherbereichs gesperrt und in den Speicher zurückgeschrieben. Dabei wird der Cache-Konsistenzmechanismus verwendet, um die Atomizität der Änderung sicherzustellen. Dieser Vorgang wird als „Cache-Sperrung“ bezeichnet Geändert. Speicherbereichsdaten, die von mehr als zwei Prozessoren zwischengespeichert werden. Durch das Zurückschreiben des Caches eines Prozessors in den Speicher wird der Cache anderer Prozessoren ungültig. Der IA-32-Prozessor und der Intel 64-Prozessor verwenden das MESI-Steuerungsprotokoll (Modify, Exclusive, Shared, Invalidate), um die Kohärenz zwischen dem internen Cache und anderen Prozessor-Caches aufrechtzuerhalten. Beim Betrieb auf Multi-Core-Prozessorsystemen können IA-32- und Intel 64-Prozessoren den Zugriff anderer Prozessoren auf den Systemspeicher und ihre internen Caches abhören. Sie verwenden Sniffing-Techniken, um sicherzustellen, dass die Daten im internen Cache, im Systemspeicher und in anderen Prozessor-Caches auf dem Bus konsistent bleiben. Wenn beispielsweise bei Prozessoren der Pentium- und P6-Familie ein Prozessor ausgespuckt wird, um zu erkennen, dass ein anderer Prozessor beabsichtigt, an eine Speicheradresse zu schreiben, die derzeit den gemeinsam genutzten Status verarbeitet, macht der Sniffing-Prozessor seine Cache-Zeile wie folgt ungültig: Füllung der Cache-Zeile erzwingen

Das obige ist der detaillierte Inhalt vonDetaillierte Einführung in das Implementierungsprinzip von Volatile in Java mit hoher Parallelität. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!

Heiße KI -Werkzeuge

Undresser.AI Undress

KI-gestützte App zum Erstellen realistischer Aktfotos

AI Clothes Remover

Online-KI-Tool zum Entfernen von Kleidung aus Fotos.

Undress AI Tool

Ausziehbilder kostenlos

Clothoff.io

KI-Kleiderentferner

Video Face Swap

Tauschen Sie Gesichter in jedem Video mühelos mit unserem völlig kostenlosen KI-Gesichtstausch-Tool aus!

Heißer Artikel

Heiße Werkzeuge

Notepad++7.3.1

Einfach zu bedienender und kostenloser Code-Editor

SublimeText3 chinesische Version

Chinesische Version, sehr einfach zu bedienen

Senden Sie Studio 13.0.1

Leistungsstarke integrierte PHP-Entwicklungsumgebung

Dreamweaver CS6

Visuelle Webentwicklungstools

SublimeText3 Mac-Version

Codebearbeitungssoftware auf Gottesniveau (SublimeText3)

Heiße Themen

Fragen zum Java Spring-Interview

Aug 30, 2024 pm 04:29 PM

Fragen zum Java Spring-Interview

Aug 30, 2024 pm 04:29 PM

In diesem Artikel haben wir die am häufigsten gestellten Fragen zu Java Spring-Interviews mit ihren detaillierten Antworten zusammengestellt. Damit Sie das Interview knacken können.

Brechen oder aus Java 8 Stream foreach zurückkehren?

Feb 07, 2025 pm 12:09 PM

Brechen oder aus Java 8 Stream foreach zurückkehren?

Feb 07, 2025 pm 12:09 PM

Java 8 führt die Stream -API ein und bietet eine leistungsstarke und ausdrucksstarke Möglichkeit, Datensammlungen zu verarbeiten. Eine häufige Frage bei der Verwendung von Stream lautet jedoch: Wie kann man von einem Foreach -Betrieb brechen oder zurückkehren? Herkömmliche Schleifen ermöglichen eine frühzeitige Unterbrechung oder Rückkehr, aber die Stream's foreach -Methode unterstützt diese Methode nicht direkt. In diesem Artikel werden die Gründe erläutert und alternative Methoden zur Implementierung vorzeitiger Beendigung in Strahlverarbeitungssystemen erforscht. Weitere Lektüre: Java Stream API -Verbesserungen Stream foreach verstehen Die Foreach -Methode ist ein Terminalbetrieb, der einen Vorgang für jedes Element im Stream ausführt. Seine Designabsicht ist

Zeitstempel für Datum in Java

Aug 30, 2024 pm 04:28 PM

Zeitstempel für Datum in Java

Aug 30, 2024 pm 04:28 PM

Anleitung zum TimeStamp to Date in Java. Hier diskutieren wir auch die Einführung und wie man Zeitstempel in Java in ein Datum konvertiert, zusammen mit Beispielen.

Java -Programm, um das Kapselvolumen zu finden

Feb 07, 2025 am 11:37 AM

Java -Programm, um das Kapselvolumen zu finden

Feb 07, 2025 am 11:37 AM

Kapseln sind dreidimensionale geometrische Figuren, die aus einem Zylinder und einer Hemisphäre an beiden Enden bestehen. Das Volumen der Kapsel kann berechnet werden, indem das Volumen des Zylinders und das Volumen der Hemisphäre an beiden Enden hinzugefügt werden. In diesem Tutorial wird erörtert, wie das Volumen einer bestimmten Kapsel in Java mit verschiedenen Methoden berechnet wird. Kapselvolumenformel Die Formel für das Kapselvolumen lautet wie folgt: Kapselvolumen = zylindrisches Volumenvolumen Zwei Hemisphäre Volumen In, R: Der Radius der Hemisphäre. H: Die Höhe des Zylinders (ohne die Hemisphäre). Beispiel 1 eingeben Radius = 5 Einheiten Höhe = 10 Einheiten Ausgabe Volumen = 1570,8 Kubikeinheiten erklären Berechnen Sie das Volumen mithilfe der Formel: Volumen = π × R2 × H (4

PHP: Eine Schlüsselsprache für die Webentwicklung

Apr 13, 2025 am 12:08 AM

PHP: Eine Schlüsselsprache für die Webentwicklung

Apr 13, 2025 am 12:08 AM

PHP ist eine Skriptsprache, die auf der Serverseite weit verbreitet ist und insbesondere für die Webentwicklung geeignet ist. 1.PHP kann HTML einbetten, HTTP -Anforderungen und Antworten verarbeiten und eine Vielzahl von Datenbanken unterstützt. 2.PHP wird verwendet, um dynamische Webinhalte, Prozessformdaten, Zugriffsdatenbanken usw. mit starker Community -Unterstützung und Open -Source -Ressourcen zu generieren. 3. PHP ist eine interpretierte Sprache, und der Ausführungsprozess umfasst lexikalische Analyse, grammatikalische Analyse, Zusammenstellung und Ausführung. 4.PHP kann mit MySQL für erweiterte Anwendungen wie Benutzerregistrierungssysteme kombiniert werden. 5. Beim Debuggen von PHP können Sie Funktionen wie error_reporting () und var_dump () verwenden. 6. Optimieren Sie den PHP-Code, um Caching-Mechanismen zu verwenden, Datenbankabfragen zu optimieren und integrierte Funktionen zu verwenden. 7

PHP vs. Python: Verständnis der Unterschiede

Apr 11, 2025 am 12:15 AM

PHP vs. Python: Verständnis der Unterschiede

Apr 11, 2025 am 12:15 AM

PHP und Python haben jeweils ihre eigenen Vorteile, und die Wahl sollte auf Projektanforderungen beruhen. 1.PHP eignet sich für die Webentwicklung mit einfacher Syntax und hoher Ausführungseffizienz. 2. Python eignet sich für Datenwissenschaft und maschinelles Lernen mit präziser Syntax und reichhaltigen Bibliotheken.

Gestalten Sie die Zukunft: Java-Programmierung für absolute Anfänger

Oct 13, 2024 pm 01:32 PM

Gestalten Sie die Zukunft: Java-Programmierung für absolute Anfänger

Oct 13, 2024 pm 01:32 PM

Java ist eine beliebte Programmiersprache, die sowohl von Anfängern als auch von erfahrenen Entwicklern erlernt werden kann. Dieses Tutorial beginnt mit grundlegenden Konzepten und geht dann weiter zu fortgeschrittenen Themen. Nach der Installation des Java Development Kit können Sie das Programmieren üben, indem Sie ein einfaches „Hello, World!“-Programm erstellen. Nachdem Sie den Code verstanden haben, verwenden Sie die Eingabeaufforderung, um das Programm zu kompilieren und auszuführen. Auf der Konsole wird „Hello, World!“ ausgegeben. Mit dem Erlernen von Java beginnt Ihre Programmierreise, und wenn Sie Ihre Kenntnisse vertiefen, können Sie komplexere Anwendungen erstellen.

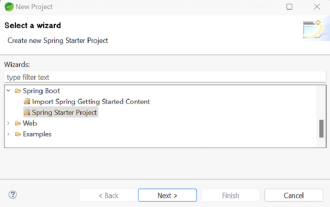

Wie führe ich Ihre erste Spring -Boot -Anwendung in der Spring Tool Suite aus?

Feb 07, 2025 pm 12:11 PM

Wie führe ich Ihre erste Spring -Boot -Anwendung in der Spring Tool Suite aus?

Feb 07, 2025 pm 12:11 PM

Spring Boot vereinfacht die Schaffung robuster, skalierbarer und produktionsbereiteter Java-Anwendungen, wodurch die Java-Entwicklung revolutioniert wird. Der Ansatz "Übereinkommen über Konfiguration", der dem Feder -Ökosystem inhärent ist, minimiert das manuelle Setup, Allo