häufiges Problem

häufiges Problem

Was kann getan werden, um das Problem der Geschwindigkeitsanpassung zwischen CPU und Hauptspeicher zu lösen?

Was kann getan werden, um das Problem der Geschwindigkeitsanpassung zwischen CPU und Hauptspeicher zu lösen?

Was kann getan werden, um das Problem der Geschwindigkeitsanpassung zwischen CPU und Hauptspeicher zu lösen?

Um das Problem der Geschwindigkeitsanpassung zwischen CPU und Hauptspeicher zu lösen, kann Cache-Speicher verwendet werden. Cache-Speicher ist ein kleiner, aber schneller Speicher, der sich zwischen der CPU und dem Hauptspeicher DRAM befindet. Er besteht normalerweise aus statischem Speicher. Statischer Speicher ist ein Speicher mit geringer Kapazität, aber hoher Geschwindigkeit, der zwischen der CPU und dem Speicher liegt.

Die Betriebsumgebung dieses Tutorials: Windows 7-System, Dell G3-Computer.

Um das Problem der Geschwindigkeitsanpassung zwischen CPU und Hauptspeicher zu lösen, kann die Implementierung den Cache zwischen CPU und Hauptspeicher verwenden.

Was ist Cache?

Cache-Speicher, ein Cache-Speicher in einem Computer, ist ein kleiner, aber schneller Speicher, der normalerweise zwischen der CPU und dem Hauptspeicher DRAM (Dynamic Random Access Memory) liegt von SRAM (Static Random Access Memory). Es handelt sich um einen Speicher mit geringer Kapazität, aber hoher Geschwindigkeit, der zwischen der CPU und dem Speicher liegt.

Die Geschwindigkeit der CPU ist viel höher als die des Speichers. Wenn die CPU direkt auf Daten aus dem Speicher zugreift, muss sie eine gewisse Zeit warten, während der Cache einen Teil der von der CPU gespeicherten Daten speichern kann gerade verwendet oder recycelt, wenn die CPU diesen Teil der Daten erneut verwenden muss. Er kann direkt aus dem Cache aufgerufen werden, wodurch wiederholter Zugriff auf Daten vermieden, die Wartezeit der CPU verkürzt und somit die Effizienz des Systems verbessert wird .

Funktion des Cache

Die Funktion des Cache besteht darin, die Rate der CPU-Dateneingabe und -ausgabe zu erhöhen. Die Cache-Kapazität ist klein, aber schnell, die Speichergeschwindigkeit ist niedrig, aber die Kapazität ist groß. Durch die Optimierung des Planungsalgorithmus wird die Leistung des Systems erheblich verbessert, als ob die Speichersystemkapazität dem Speicher entspricht und die Zugriffsgeschwindigkeit ähnlich ist der Cache.

Die Geschwindigkeit der CPU ist viel höher als die des Speichers. Wenn die CPU direkt auf Daten aus dem Speicher zugreift, muss sie eine gewisse Zeit warten, während der Cache einen Teil der von der CPU gespeicherten Daten speichern kann gerade verwendet oder recycelt, wenn die CPU diesen Teil der Daten erneut verwenden muss. Er kann direkt aus dem Cache aufgerufen werden, wodurch wiederholter Zugriff auf Daten vermieden, die Wartezeit der CPU verkürzt und somit die Effizienz des Systems verbessert wird . Der Cache ist in L1Cache (Level-1-Cache) und L2Cache (Level-2-Cache) unterteilt, der hauptsächlich in die CPU integriert ist, während L2Cache auf dem Motherboard oder der CPU integriert ist.

Grundprinzipien des Caches

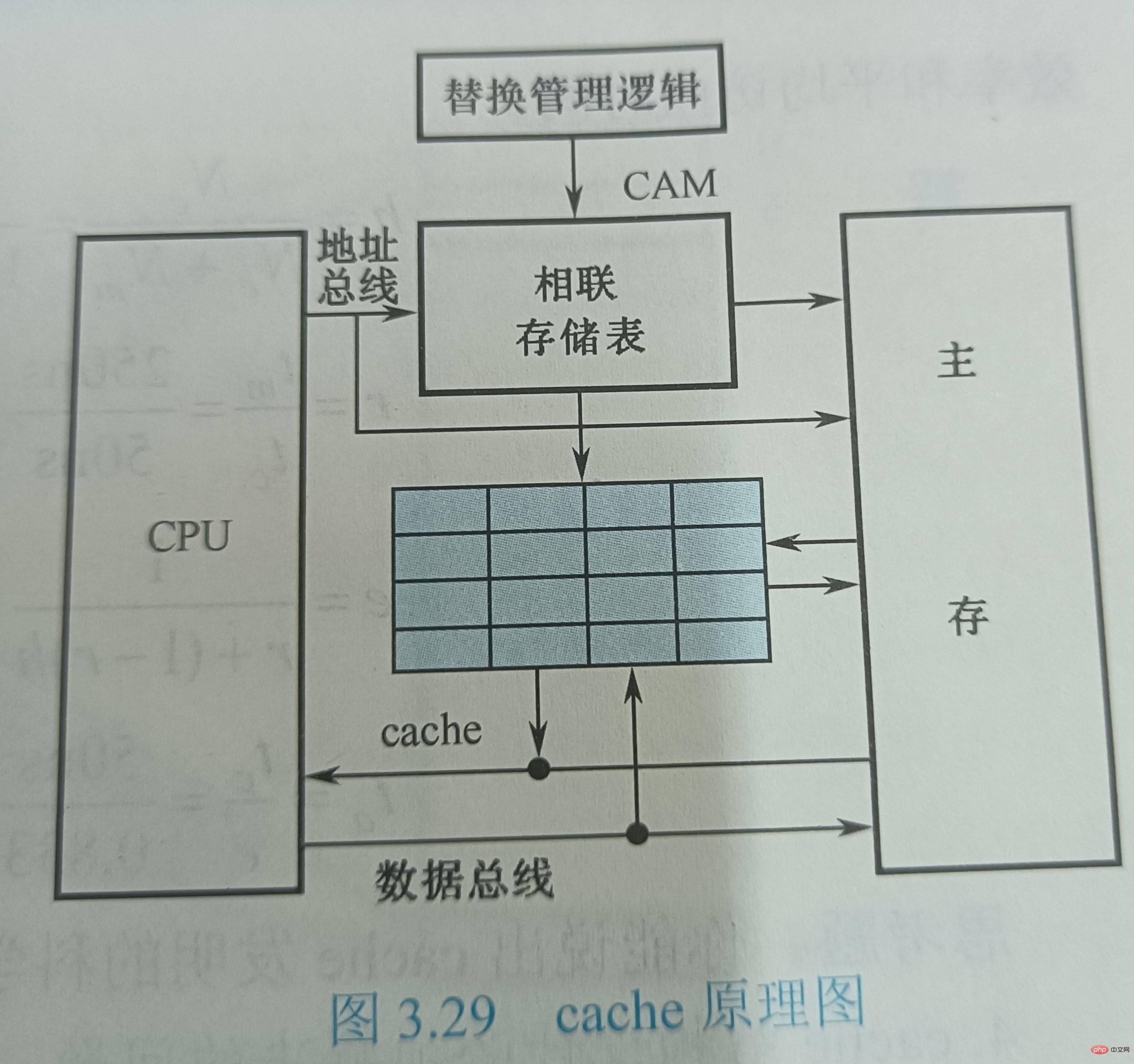

Zusätzlich zum SRAM verfügt der Cache auch über eine Steuerlogik. Befindet sich der Cache außerhalb des CPU-Chips, wird seine Steuerlogik im Allgemeinen mit der Hauptspeicher-Steuerlogik kombiniert, die als Hauptspeicher-/Cache-Controller bezeichnet wird. Wenn sich der Cache innerhalb der CPU befindet, stellt die CPU ihre Steuerlogik bereit. C Der Datenaustausch zwischen CPU und Cache basiert auf Worten, während der Datenaustausch zwischen Cache und Hauptspeicher auf Blöcken basiert. Ein Block besteht aus mehreren Wörtern und hat eine feste Länge. Wenn die CPU ein Wort im Speicher liest, sendet sie die Speicheradresse des Worts an den Cache und den Hauptspeicher. Zu diesem Zeitpunkt bestimmt die Cache-Steuerlogik anhand der Adresse, ob sich das Wort derzeit im Cache befindet: Wenn dies der Fall ist, trifft der Cache zu und das Wort wird sofort an die CPU übertragen. Wenn nicht, fehlt der Cache Der Hauptspeicher-Lesezyklus wird verwendet, um das Wort aus dem Hauptspeicher zu lesen. Der Lesevorgang wird an die CPU gesendet. Gleichzeitig wird der gesamte Datenblock, der dieses Wort enthält, aus dem Hauptspeicher gelesen und an den Cache gesendet.

Abbildung 3.29 zeigt das schematische Diagramm des Caches. Nehmen Sie an, dass die Cache-Lesezeit 50 ns und die Hauptspeicher-Lesezeit 250 ns beträgt. Das Speichersystem ist modular aufgebaut und jedem 8K-Modul im Hauptspeicher ist ein Cache mit einer Kapazität von 16 Wörtern zugeordnet. Der Cache ist in 4 Zeilen unterteilt, jede Zeile enthält 4 Wörter (W). Die dem Cache zugewiesene Adresse wird in einem assoziativen Speicher CAM gespeichert, bei dem es sich um einen inhaltsadressierbaren Speicher handelt. Wenn die CPU einen Speicherzugriffsbefehl ausführt, sendet sie die Adresse des Wortes, auf das zugegriffen werden soll, an das CAM; wenn W nicht im Cache ist, wird W vom Hauptspeicher an die CPU übertragen. Gleichzeitig wird eine Datenzeile, die aus vier aufeinanderfolgenden Wörtern mit W besteht, an den Cache gesendet und ersetzt die ursprüngliche Datenzeile im Cache. Hier wird der Ersetzungsalgorithmus durch Hardware-Logikschaltungen implementiert, die stets die Cache-Nutzung verwalten.

Abbildung 3.29 zeigt das schematische Diagramm des Caches. Nehmen Sie an, dass die Cache-Lesezeit 50 ns und die Hauptspeicher-Lesezeit 250 ns beträgt. Das Speichersystem ist modular aufgebaut und jedem 8K-Modul im Hauptspeicher ist ein Cache mit einer Kapazität von 16 Wörtern zugeordnet. Der Cache ist in 4 Zeilen unterteilt, jede Zeile enthält 4 Wörter (W). Die dem Cache zugewiesene Adresse wird in einem assoziativen Speicher CAM gespeichert, bei dem es sich um einen inhaltsadressierbaren Speicher handelt. Wenn die CPU einen Speicherzugriffsbefehl ausführt, sendet sie die Adresse des Wortes, auf das zugegriffen werden soll, an das CAM; wenn W nicht im Cache ist, wird W vom Hauptspeicher an die CPU übertragen. Gleichzeitig wird eine Datenzeile, die aus vier aufeinanderfolgenden Wörtern mit W besteht, an den Cache gesendet und ersetzt die ursprüngliche Datenzeile im Cache. Hier wird der Ersetzungsalgorithmus durch Hardware-Logikschaltungen implementiert, die stets die Cache-Nutzung verwalten.

Probleme, die beim Design der Cache-Struktur gelöst werden müssenAus dem Grundprinzip des Caches geht hervor, dass das Cache-Design zwei Prinzipien folgen muss: Erstens hoffen wir, dass die Cache-Trefferquote so hoch ist wie möglich, was eigentlich nahe bei 1 liegen sollte; Die zweite besteht darin, zu hoffen, dass der Cache für die CPU transparent ist, dh unabhängig davon, ob ein Cache vorhanden ist oder nicht, greift die CPU auf die gleiche Weise auf den Speicher zu und die Software kann darauf zugreifen den Cache, ohne irgendwelche Anweisungen hinzuzufügen. Die Probleme mit der Trefferquote und der Transparenz sind gelöst. Aus Sicht des CPU-Zugriffs auf den Speicher wird der Speicher die Kapazität des Hauptspeichers und eine Geschwindigkeit haben, die nahe am Cache liegt. Zu diesem Zweck muss eine bestimmte Hardwareschaltung hinzugefügt werden, um die Steuerfunktion zu vervollständigen, nämlich den Cache-Controller.

Beim Entwerfen der Cache-Struktur müssen mehrere Probleme gelöst werden: ① Wie werden die Inhalte des Hauptspeichers gespeichert, wenn sie in den Cache übertragen werden? ② Wie werden die Informationen im Cache gefunden, wenn auf den Speicher zugegriffen wird? die vorhandenen Informationen im Cache, wenn der Cache-Speicherplatz nicht ausreicht. ④ Wie kann der Cache-Inhalt neu geschrieben werden, wenn ein Schreibvorgang erforderlich ist?

Unter diesen hängen die ersten beiden Fragen miteinander zusammen, nämlich wie man die Hauptspeicherinformationen im Cache findet und wie man die Hauptspeicheradresse in eine Cache-Adresse umwandelt. Im Vergleich zur Hauptspeicherkapazität ist die Cache-Kapazität sehr gering. Der gespeicherte Inhalt ist nur eine Teilmenge des Hauptspeicherinhalts, und der Datenaustausch zwischen Cache und Hauptspeicher erfolgt in Blockeinheiten. Um den Hauptspeicherblock in den Cache zu legen, muss eine Methode verwendet werden, um die Hauptspeicheradresse im Cache zu lokalisieren, was als Adresszuordnung bezeichnet wird. Die physikalische Bedeutung des Wortes „Mapping“ besteht darin, die entsprechende Beziehung zwischen Standorten zu ermitteln und diese mit Hardware umzusetzen. Auf diese Weise wird beim Zugriff der CPU auf den Speicher die Speicheradresse eines von ihr angegebenen Wortes automatisch in eine Cache-Adresse umgewandelt, dh eine Cache-Adresskonvertierung.

Das Cache-Ersetzungsproblem besteht hauptsächlich darin, den Ersetzungsalgorithmus auszuwählen und auszuführen, um den Inhalt im Cache zu ersetzen, wenn der Cache fehlt. Die letzte Frage betrifft die Schreiboperationsstrategie des Caches, die sich auf die Aufrechterhaltung der Konsistenz zwischen Hauptspeicher und Cache während Aktualisierungen konzentriert.

(Teilen von Lernvideos: Programmiervideo)

Das obige ist der detaillierte Inhalt vonWas kann getan werden, um das Problem der Geschwindigkeitsanpassung zwischen CPU und Hauptspeicher zu lösen?. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!

Heiße KI -Werkzeuge

Undresser.AI Undress

KI-gestützte App zum Erstellen realistischer Aktfotos

AI Clothes Remover

Online-KI-Tool zum Entfernen von Kleidung aus Fotos.

Undress AI Tool

Ausziehbilder kostenlos

Clothoff.io

KI-Kleiderentferner

AI Hentai Generator

Erstellen Sie kostenlos Ai Hentai.

Heißer Artikel

Heiße Werkzeuge

Notepad++7.3.1

Einfach zu bedienender und kostenloser Code-Editor

SublimeText3 chinesische Version

Chinesische Version, sehr einfach zu bedienen

Senden Sie Studio 13.0.1

Leistungsstarke integrierte PHP-Entwicklungsumgebung

Dreamweaver CS6

Visuelle Webentwicklungstools

SublimeText3 Mac-Version

Codebearbeitungssoftware auf Gottesniveau (SublimeText3)

Heiße Themen

Wie hoch sollte die CPU-Auslastung beim Spielen sein?

Feb 19, 2024 am 11:21 AM

Wie hoch sollte die CPU-Auslastung beim Spielen sein?

Feb 19, 2024 am 11:21 AM

Es kommt häufig vor, dass Spiele Ihren Computer verlangsamen, weil sie viele Ressourcen verbrauchen. Es ist wichtig, die CPU-Auslastung beim Spielen zu kennen, um eine Überlastung zu vermeiden. Daher ist es wichtig, die angemessene CPU-Auslastung im Auge zu behalten, um ein reibungsloses Spielerlebnis zu gewährleisten. In diesem Artikel schauen wir uns die angemessene CPU-Auslastung an, die Sie erreichen sollten, während Ihr Spiel läuft. CPU-Auslastung beim Gaming Die CPU-Auslastung ist ein wichtiger Indikator für die Prozessorauslastung und hängt von den Leistungsspezifikationen der CPU ab. Leistungsstärkere CPUs haben im Allgemeinen eine höhere Auslastung. Eine CPU mit mehr Kernen und Threads kann die Gesamtleistung Ihres Systems verbessern. Die Multi-Threading-Unterstützung hilft dabei, das volle Potenzial Ihrer CPU auszuschöpfen. In Spielen hängt die CPU-Auslastung von der Prozessorauslastung ab, was sich auf das Spiel auswirken kann

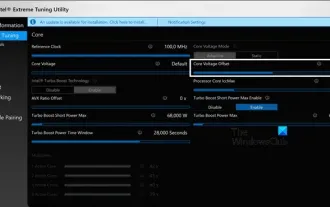

So unterlasten und übertakten Sie Ihre CPU mit Intel XTU

Feb 19, 2024 am 11:06 AM

So unterlasten und übertakten Sie Ihre CPU mit Intel XTU

Feb 19, 2024 am 11:06 AM

Intel XTU ist eine leistungsstarke Anwendung, mit der Sie die Leistung Ihres Computers einfach verwalten können. Sie können Überhitzungsprobleme beheben, indem Sie die CPU-Spannung anpassen oder die Leistung durch Übertakten steigern. In diesem Artikel schauen wir uns an, wie Sie Intel XTU nutzen können, um die Leistung Ihres Computers zu optimieren, sei es durch die Anpassung der Spannung oder durch Übertakten. Welche Auswirkungen haben Undervolting und Overclocking auf die CPU? Bevor wir weiter lernen, wie man eine CPU unter- und übertaktet, müssen wir zunächst verstehen, was das ist. Unter Unterspannung versteht man die schrittweise Reduzierung der von der CPU benötigten Spannung. Dieser Prozess trägt dazu bei, die Wärmeemissionen zu reduzieren, da Hochspannung zu höheren Temperaturen führt. Durch die Reduzierung der Spannungsversorgung der CPU kann die Temperatur effektiv gesenkt werden. Wenn Ihr Laptop langsamer wird, nachdem er heiß geworden ist, sollten Sie das Problem umgehend beheben.

So stellen Sie die CPU-Leistung in Win11 auf volle Leistung ein

Feb 19, 2024 pm 07:42 PM

So stellen Sie die CPU-Leistung in Win11 auf volle Leistung ein

Feb 19, 2024 pm 07:42 PM

Viele Benutzer stellen fest, dass der Computer bei Verwendung des Win11-Systems nicht reibungslos läuft. Sie möchten die CPU-Leistung verbessern, wissen aber nicht, wie das geht. Im Folgenden wird detailliert beschrieben, wie Sie die CPU-Leistung im Win11-System auf die höchste Stufe einstellen, um Ihren Computer effizienter zu machen. Einstellungsmethode: 1. Klicken Sie mit der rechten Maustaste auf „Dieser PC“ auf dem Desktop und wählen Sie „Eigenschaften“ in der Optionsliste. 2. Nachdem Sie die neue Benutzeroberfläche aufgerufen haben, klicken Sie unter „Verwandte Links“ auf „Erweiterte Systemeinstellungen“. 3. Klicken Sie im sich öffnenden Fenster oben auf die Registerkarte „Erweitert“ und dann unten bei „Leistung“ auf das &.

Der Betriebsprozess des WIN10-Diensthosts belegt zu viel CPU

Mar 27, 2024 pm 02:41 PM

Der Betriebsprozess des WIN10-Diensthosts belegt zu viel CPU

Mar 27, 2024 pm 02:41 PM

1. Zuerst klicken wir mit der rechten Maustaste auf die leere Stelle der Taskleiste und wählen die Option [Task-Manager] oder klicken mit der rechten Maustaste auf das Startlogo und wählen dann die Option [Task-Manager]. 2. In der geöffneten Task-Manager-Oberfläche klicken wir ganz rechts auf die Registerkarte [Dienste]. 3. Klicken Sie in der geöffneten Registerkarte [Dienst] unten auf die Option [Dienst öffnen]. 4. Klicken Sie im sich öffnenden Fenster [Dienste] mit der rechten Maustaste auf den Dienst [InternetConnectionSharing(ICS)] und wählen Sie dann die Option [Eigenschaften]. 5. Ändern Sie im sich öffnenden Eigenschaftenfenster die Option „Öffnen mit“ in „Deaktiviert“, klicken Sie auf „Übernehmen“ und dann auf „OK“. 6. Klicken Sie auf das Startlogo, dann auf die Schaltfläche zum Herunterfahren, wählen Sie [Neustart] und schließen Sie den Neustart des Computers ab.

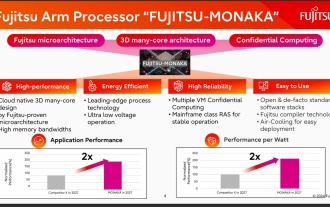

144-Kerne, 3D-gestapelter SRAM: Fujitsu stellt den Rechenzentrumsprozessor MONAKA der nächsten Generation vor

Jul 29, 2024 am 11:40 AM

144-Kerne, 3D-gestapelter SRAM: Fujitsu stellt den Rechenzentrumsprozessor MONAKA der nächsten Generation vor

Jul 29, 2024 am 11:40 AM

Laut Nachrichten dieser Website vom 28. Juli berichteten die ausländischen Medien TechRader, dass Fujitsu den FUJITSU-MONAKA-Prozessor (im Folgenden als MONAKA bezeichnet) detailliert vorgestellt habe, dessen Auslieferung im Jahr 2027 geplant sei. MONAKACPU basiert auf der „Cloud Native 3D Many-Core“-Architektur und übernimmt den Arm-Befehlssatz. Es ist auf die Bereiche Rechenzentrum, Edge und Telekommunikation ausgerichtet. Es ist für KI-Computing geeignet und kann RAS1 auf Mainframe-Ebene realisieren. Fujitsu sagte, dass MONAKA einen Sprung in puncto Energieeffizienz und Leistung machen wird: Dank Technologien wie der Ultra-Low-Voltage-Technologie (ULV) kann die CPU im Jahr 2027 die doppelte Energieeffizienz von Konkurrenzprodukten erreichen, und für die Kühlung ist keine Wasserkühlung erforderlich Darüber hinaus kann die Anwendungsleistung des Prozessors doppelt so hoch sein wie die Ihres Konkurrenten. In puncto Anleitung ist MONAKA mit Vector ausgestattet

So erhöhen Sie die Taktfrequenz der CPU Ihres Computers

Feb 20, 2024 am 09:54 AM

So erhöhen Sie die Taktfrequenz der CPU Ihres Computers

Feb 20, 2024 am 09:54 AM

So übertakten Sie Computer-CPUs Mit der kontinuierlichen Weiterentwicklung der Technologie wird auch der Bedarf der Menschen an Computerleistung immer höher. Eine wirksame Möglichkeit zur Verbesserung der Computerleistung besteht darin, die Betriebsfrequenz der CPU durch Übertakten zu erhöhen. Durch Übertakten kann die CPU Daten schneller verarbeiten und sorgt so für eine höhere Rechenleistung. Wie übertaktet man also die CPU eines Computers? Im Folgenden werden Ihnen die Grundprinzipien und spezifischen Betriebsmethoden des Übertaktens vorgestellt. Lassen Sie uns zunächst verstehen, wie Übertakten funktioniert. Die Betriebsfrequenz der CPU wird durch den Quarzoszillator auf der Hauptplatine bestimmt

Leak enthüllt wichtige Spezifikationen von Intel Arrow Lake-U, -H, -HX und -S

Jun 15, 2024 pm 09:49 PM

Leak enthüllt wichtige Spezifikationen von Intel Arrow Lake-U, -H, -HX und -S

Jun 15, 2024 pm 09:49 PM

Intel Arrow Lake wird voraussichtlich auf der gleichen Prozessorarchitektur wie Lunar Lake basieren, was bedeutet, dass Intels brandneue Lion Cove-Leistungskerne mit den wirtschaftlichen Skymont-Effizienzkernen kombiniert werden. Während Lunar Lake nur als Ava verfügbar ist

AM4 will nicht sterben, laut Nachrichten wird AMD Ryzen 9 5900XT/7 5800XT auf den Markt bringen: getaktet mit bis zu 4,8 GHz

Jun 05, 2024 pm 09:43 PM

AM4 will nicht sterben, laut Nachrichten wird AMD Ryzen 9 5900XT/7 5800XT auf den Markt bringen: getaktet mit bis zu 4,8 GHz

Jun 05, 2024 pm 09:43 PM

Laut Nachrichten dieser Website vom 1. Juni hat die Quelle @CodeCommando heute getwittert und einige Screenshots der bevorstehenden Präsentationsdokumente von AMD auf der Computex2024-Veranstaltung geteilt. Der Inhalt des Tweets war „AM4 wird niemals sterben“, und das dazugehörige Bild zeigte zwei neue Prozessoren der Ryzen5000XT-Serie. Den Screenshots zufolge sind die folgenden zwei Produkte zu sehen: Ryzen95900XTR Ryzen95900XT ist relativ hochpreisig positioniert. Dabei handelt es sich um einen neuen 16-Kern-AM4-Prozessor mit einer Taktrate, die etwas niedriger ist als die von AMDs Ryzen95950X. Ryzen75800XT Es handelt sich um eine schnellere Variante des bestehenden Ryzen75800X-Prozessors. Beide Prozessoren sind mit bis zu 4,8 G getaktet