linux vcs ist ein kompilierter Verilog-Simulator, ein Tool zum Simulieren und Anzeigen von Wellenformen; es ähnelt Tools wie Modelsim und Questasim unter Windows sowie Quartus- und Vivado-Simulationsoperationen.

Die Betriebsumgebung dieses Tutorials: Linux5.9.8-System, Dell G3-Computer.

Was ist Linux VCS?

Grundlegende Verwendung von VCS-Tools

VCS ist ein Tool zum Simulieren und Anzeigen von Wellenformen unter Linux, ähnlich wie Tools wie Modelsim und Questasim unter Windows sowie Quartus- und Vivado-Simulationsoperationen.

Gemeinsame Anweisungssuffixe für vcs#🎜🎜 #

| Bedeutung | |

|---|---|

wird verwendet, um die durch die Kompilierung generierten Informationen in die Protokolldatei einzufügen-l readme.log

|

用于将编译产生的信息放在log文件内 |

+v2k |

是使VCS兼容verilog 2001以前的标准 |

-debug_all |

用于产生debug所需的文件 |

-f verilog_file.f |

可将.f文件里的源码全部编译 |

-R |

编译后立即运行,即编译完成后立即执行 ./simv |

-Mupdate |

源文件有修改时,只重新编译有改动的**.v**文件,节约编译时间。 |

-sverilog |

打开对Systemverilog的支持,编译Systemverilog文件时使用。 |

-timescale=1ns/1ns |

设置仿真精度 |

-o simv_file |

编译默认产生的可执行文件为simv,可以使用 -o 更改可执行文件名。如果这里修改执行仿真时候就不是使用simv而是对应的o名字了。 |

simv的常见指令

| 指令 | 含义 |

|---|---|

./simv -l run.log |

执行的日志文件保存 |

./simv -gui |

-debug_all# 🎜🎜# #🎜🎜#Datei zum Generieren von Debug erforderlich#🎜🎜##🎜🎜##🎜🎜##🎜🎜#-f verilog_file.f#🎜🎜##🎜🎜# kann sein Alle Quellcodes in der .f-Datei werden kompiliert ist, nachdem die Kompilierung abgeschlossen ist. Sofort ausführen#🎜🎜#./simv#🎜🎜##🎜🎜##🎜🎜##🎜🎜##🎜🎜#-Mupdate#🎜🎜## 🎜🎜#Die Quelldatei wurde geändert. Wenn , werden nur die geänderten **.v**-Dateien neu kompiliert, um Kompilierungszeit zu sparen. #🎜🎜##🎜🎜##🎜🎜##🎜🎜#-sverilog#🎜🎜##🎜🎜#Offene Unterstützung für #🎜🎜#Systemverilog#🎜🎜#, kompilieren #🎜 🎜 #Systemverilog#🎜🎜# Datei. #🎜🎜##🎜🎜##🎜🎜##🎜🎜#-timescale=1ns/1ns#🎜🎜##🎜🎜#Simulationsgenauigkeit einstellen#🎜🎜##🎜🎜##🎜 🎜##🎜🎜#-o simv_file#🎜🎜##🎜🎜#Die standardmäßig durch Kompilierung generierte ausführbare Datei ist #🎜🎜#simv#🎜🎜#, Sie können #🎜🎜# verwenden -o #🎜🎜# Ändert den Namen der ausführbaren Datei. Wenn Sie es hier beim Ausführen der Simulation ändern, verwenden Sie nicht #🎜🎜#simv#🎜🎜#, sondern den entsprechenden o-Namen. #🎜🎜##🎜🎜##🎜🎜##🎜🎜##🎜🎜##🎜🎜# Allgemeine Befehle für simv#🎜🎜##🎜🎜##🎜🎜##🎜🎜##🎜🎜##🎜 🎜#Befehl#🎜🎜##🎜🎜#Bedeutung#🎜🎜##🎜🎜##🎜🎜##🎜🎜##🎜🎜##🎜🎜#./simv -l run.log#🎜🎜##🎜🎜#Die Ausführungsprotokolldatei wird gespeichert#🎜🎜##🎜🎜##🎜🎜##🎜🎜#./simv -gui#🎜🎜##🎜🎜 # Mit grafischer Oberfläche öffnen#🎜🎜##🎜🎜##🎜🎜##🎜🎜# basiert auf dem offiziellen Tutorial von Full Adder. Zunächst wird der Ausführungsprozess ohne Verwendung eines Skripts vorgestellt.

(1) Führen Sie zuerst vcs aus und fügen Sie die entsprechende full_adder-Datei hinzu Die aufgerufene Datei wird zuerst ausgeschrieben und diese Anweisung generiert eine SIMV-Datei (wenn -o simv_file verwendet wird, wird der entsprechende Dateiname generiert). vcs加入对应的full_adder文件

vcs -sverilog -debug_all -timescale=1ns/1ps full_adder.v full_adder_tb.v -l com.log

这里先写full_adder.v 是因为tb文件需要调用它,所以把被调用的文件先写出来,这条语句会生成simv文件(如果使用了-o simv_file会生成对应的文件名字)。

(2)可以用./simv文件执行波形的界面,也可以采用下面指令以后台方式打开一个界面。

dve &或者 ./simv -l run.log -gui

(3)如果以./simv执行会直接看到波形文件,如果使用dve & 需要自行加入simv (2) Sie können die Datei ./simv verwenden, um die Wellenformschnittstelle auszuführen, oder Sie können den folgenden Befehl verwenden, um eine Schnittstelle im Hintergrund zu öffnen. .PHONY:vcs sim dve clean

OUTPUT = adder

VCS = vcs -sverilog +v2k -timescale=1ns/1ns \

-debug_all \

-o ${OUTPUT} \

-l compile.log \SIM = ./${OUTPUT} -l run.log

vcs: ${VCS} -f verilog_file.f

sim: ${SIM}dve:

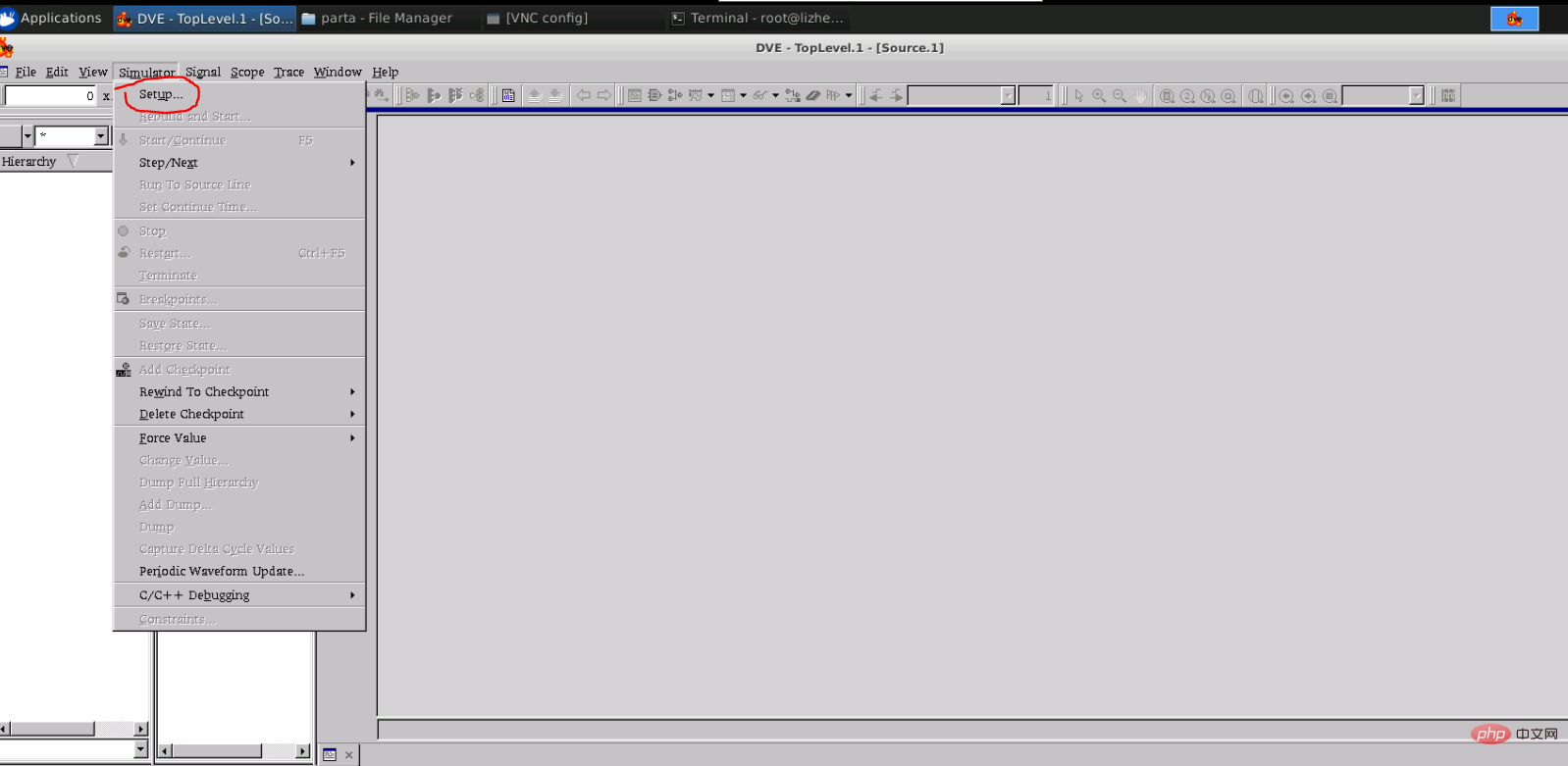

dve -vpd vcdplus.vpd & clean: rm -rf *.log csrc simv* *.key *.vpd DVEfiles coverage *.vdb./simv ausführen, wird die Wave-Datei direkt angezeigt. Wenn Sie dve & verwenden, müssen Sie den simv-Datei selbst. Sehen Sie sich die Wellenform an, wählen Sie simulator->Setup und fügen Sie die generierte

simv -Datei hinzu.

-Datei hinzu.

Wenn unter alles ausführen keine Zeitskala angegeben ist, wird hier ein Fehler gemeldet. Wenn kein Fehler vorliegt, bedeutet dies, dass unsere Funktion vollständig korrekt ist. Klicken Sie mit der rechten Maustaste, um die Wave-Datei hinzuzufügen, und drücken Sie die Taste

f

, um die Wellenform anzuzeigen. (4) Die folgenden vier Schlüsselfunktionen Die erste: Verfolgen, wer das Signal steuert

Strg+D Die zweite: Verfolgen Sie die Werttransformation des Signals

Strg+Umschalt+D

Die dritte: Verfolgen Sie das unbekannter Zustand  Viertens: Verfolgen Sie, wer früher gefahren ist

Viertens: Verfolgen Sie, wer früher gefahren ist

3. So schreiben Sie die Makefile-Datei

Unter anderem kann .PHONY angeben, welche Schlüsselwörter für Make-Vorgänge verwendet werden sollen.

find -name ".*v" > file.list

Das obige ist der detaillierte Inhalt vonWas ist Linux VCS?. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!