Technologie-Peripheriegeräte

Technologie-Peripheriegeräte

KI

KI

Ein Überblick über die drei gängigen Chiparchitekturen für autonomes Fahren in einem Artikel

Ein Überblick über die drei gängigen Chiparchitekturen für autonomes Fahren in einem Artikel

Ein Überblick über die drei gängigen Chiparchitekturen für autonomes Fahren in einem Artikel

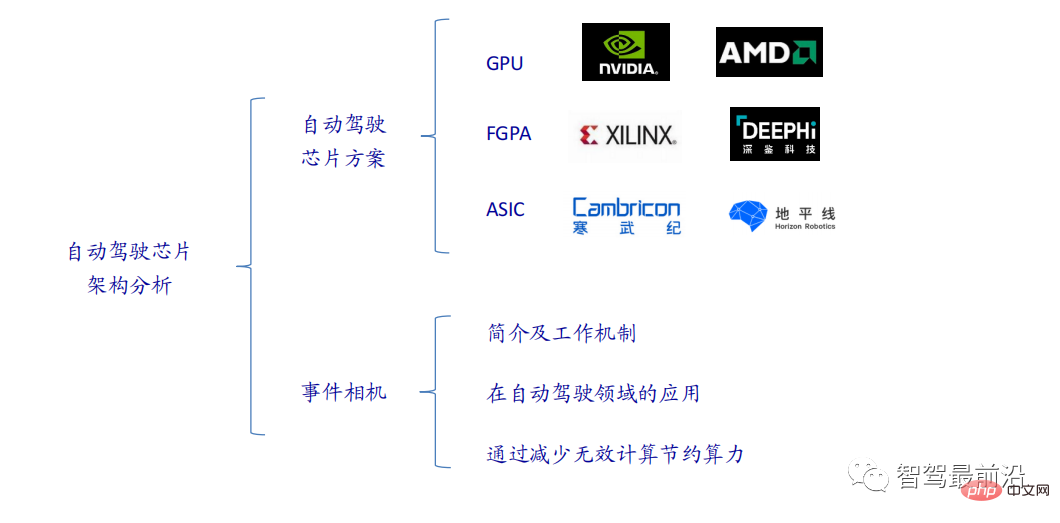

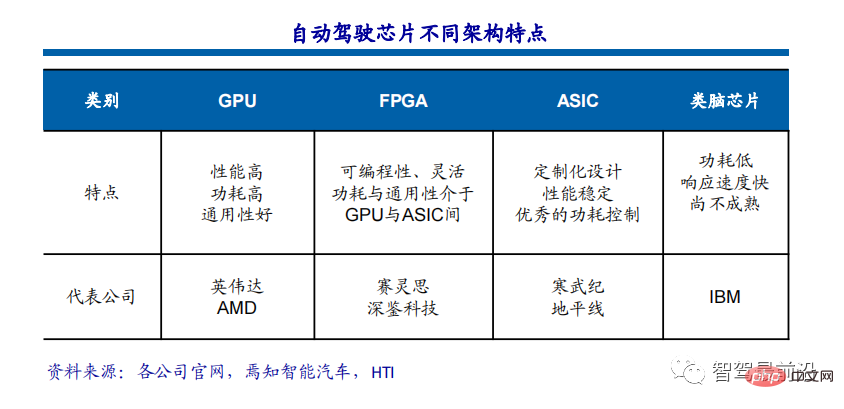

Die aktuellen Mainstream-KI-Chips sind hauptsächlich in drei Kategorien unterteilt: GPU, FPGA und ASIC. Sowohl GPU als auch FPGA sind im Frühstadium relativ ausgereifte Chiparchitekturen und Allzweckchips. ASIC ist ein Chip, der für bestimmte KI-Szenarien angepasst ist. Die Industrie hat bestätigt, dass CPUs nicht für KI-Computing geeignet sind, sie aber auch für KI-Anwendungen unerlässlich sind.

GPU-Lösung

Architekturvergleich zwischen GPU und CPU

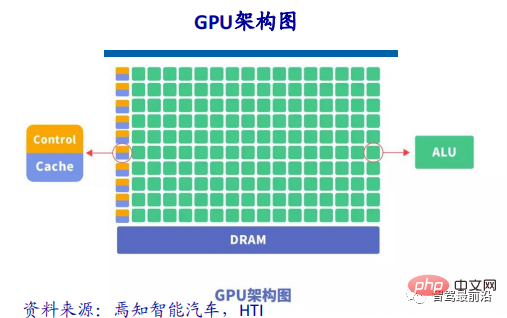

CPU folgt der von Neumann-Architektur, deren Kern gespeicherte Programme/Daten und serielle sequentielle Ausführung sind. Daher benötigt die CPU-Architektur viel Platz, um die Speichereinheit (Cache) und die Steuereinheit (Control) unterzubringen. Im Gegensatz dazu nimmt die Recheneinheit (ALU) nur einen kleinen Teil ein, sodass die CPU in großen Mengen begrenzt ist. Skalieren Sie paralleles Rechnen relativ besser mit logischen Steuerungen.

GPU (Graphics Processing Unit), also ein Grafikprozessor, ist eine groß angelegte Parallelrechnerarchitektur, die aus einer großen Anzahl von Recheneinheiten besteht. Sie wurde ursprünglich von der CPU getrennt und speziell zur Verarbeitung von Bilddaten parallel verwendet Es ist für die gleichzeitige Verarbeitung mehrerer Bilder konzipiert. Die GPU enthält auch grundlegende Recheneinheiten, Steuereinheiten und Speichereinheiten, aber die Architektur der GPU unterscheidet sich stark von der der CPU. Das Architekturdiagramm ist unten dargestellt.

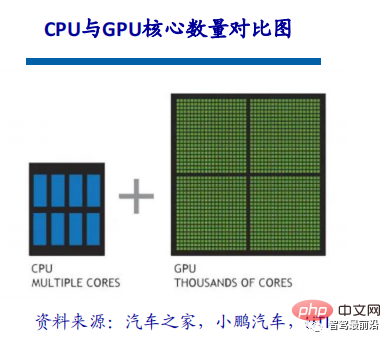

Im Vergleich zur CPU sind weniger als 20 % des CPU-Chipplatzes ALU, während mehr als 80 % des GPU-Chipplatzes ALU sind. Das heißt, die GPU verfügt über mehr ALUs für die parallele Datenverarbeitung. Unterschied zwischen GPU und CPU Diese kleineren Kerne sind für die gleichzeitige Bewältigung mehrerer Aufgaben ausgelegt.

Der Grund, warum CPU und GPU sehr unterschiedlich sind, liegt in ihren unterschiedlichen Designzielen. Sie zielen jeweils auf zwei unterschiedliche Anwendungsszenarien ab. Die CPU benötigt eine große Vielseitigkeit, um verschiedene Datentypen verarbeiten zu können. Gleichzeitig erfordert sie logisches Urteilsvermögen und führt eine große Anzahl von Verzweigungssprüngen und Interrupt-Verarbeitung ein. All dies macht die interne Struktur der CPU äußerst komplex. Die GPU steht großen Datenmengen mit stark vereinheitlichten Typen und keiner Abhängigkeit voneinander gegenüber und verfügt über eine reine Rechenumgebung, die nicht unterbrochen werden muss.

Eine kurze Beschreibung der GPU-Beschleunigungstechnologie

Für Deep Learning basiert die aktuelle Hardwarebeschleunigung hauptsächlich auf der Verwendung von Grafikprozessoreinheiten. Im Vergleich zu herkömmlichen CPUs verfügen GPUs über mehrere Größenordnungen mehr Kernrechenleistung und lassen sich einfacher parallele Berechnungen durchführen.

Die Many-Core-Architektur der GPU enthält Tausende von Stream-Prozessoren, die Vorgänge parallel ausführen und die Berechnungszeit des Modells erheblich verkürzen können. Da NVIDIA, AMD und andere Unternehmen weiterhin die umfassende Unterstützung paralleler Architekturen ihrer GPUs vorantreiben, sind GPUs für allgemeine Computeranwendungen zu einem wichtigen Mittel zur Beschleunigung paralleler Anwendungen geworden.

Derzeit hat sich die GPU zu einem relativ ausgereiften Stadium entwickelt. Durch die Verwendung einer GPU zum Trainieren tiefer neuronaler Netze können die effizienten parallelen Rechenfunktionen von Tausenden von Rechenkernen voll ausgeschöpft werden. In Szenarien, in denen umfangreiche Trainingsdaten verwendet werden, wird der Zeitaufwand erheblich verkürzt und es werden weniger Server belegt. Bei richtiger Optimierung für ein tiefes neuronales Netzwerk kann eine GPU-Karte der Rechenleistung von Dutzenden oder sogar Hunderten von CPU-Servern entsprechen. Daher ist die GPU zur bevorzugten Lösung der Branche für das Training von Deep-Learning-Modellen geworden.

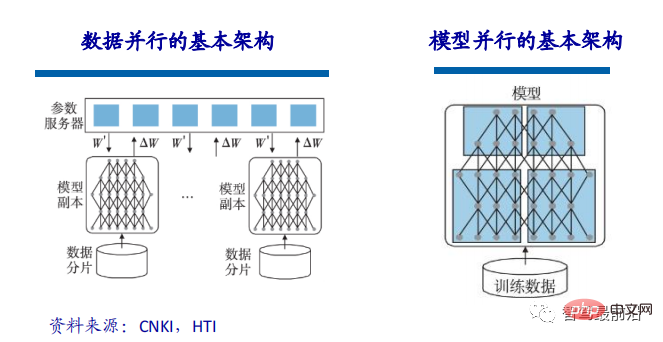

Wenn der Umfang des trainierten Modells relativ groß ist, kann das Training des Modells durch Datenparallelität beschleunigt werden. Datenparallelität kann die Trainingsdaten segmentieren und mehrere Modellinstanzen verwenden, um mehrere Datenblöcke gleichzeitig zu trainieren. Da bei der Implementierung der Datenparallelität dasselbe Modell und unterschiedliche Daten für das Training verwendet werden, liegt der Engpass, der die Modellleistung beeinträchtigt, im Parameteraustausch zwischen mehreren CPUs oder mehreren GPUs. Gemäß der Parameteraktualisierungsformel müssen die von allen Modellen berechneten Gradienten an den Parameterserver übermittelt und auf die entsprechenden Parameter aktualisiert werden. Daher kann die Aufteilung der Datenscheiben und die Bandbreite des Parameterservers zu Engpässen werden, die die Effizienz einschränken Datenparallelität. Zusätzlich zur Datenparallelität kann die Modellparallelität auch zur Beschleunigung des Modelltrainings genutzt werden. Unter Modellparallelität versteht man die Aufteilung eines großen Modells in mehrere Shards, die jeweils von mehreren Trainingseinheiten gehalten werden, um das Training des großen Modells abzuschließen.

GPU-beschleunigtes Rechnen

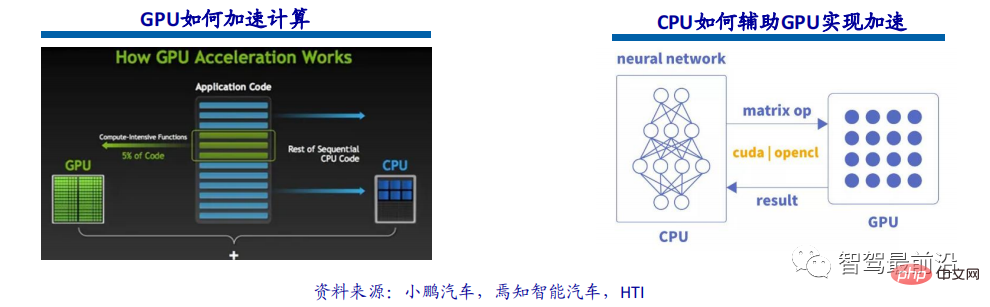

GPU-beschleunigtes Rechnen bezieht sich auf die gleichzeitige Verwendung von Grafikprozessoren (GPUs) und CPUs, um wissenschaftliche, analytische, technische, Verbraucher- und Unternehmensanwendungen zu beschleunigen. GPU-Beschleuniger wurden erstmals 2007 von NVIDIA eingeführt und werden heute weltweit zur Unterstützung energieeffizienter Rechenzentren in Regierungslaboren, Universitäten, Konzernen sowie kleinen und mittleren Unternehmen eingesetzt. GPUs beschleunigen Anwendungen auf Plattformen, die von Autos, Telefonen und Tablets bis hin zu Drohnen und Robotern reichen.

GPU-beschleunigtes Computing kann eine außergewöhnliche Anwendungsleistung bieten, indem die Arbeitslast des rechenintensiven Teils der Anwendung auf die GPU verlagert wird, während der Rest des Programmcodes weiterhin von der CPU ausgeführt wird. Aus Anwendersicht laufen Anwendungen deutlich schneller.

GPU führt derzeit nur einfache parallele Matrixmultiplikations- und Additionsoperationen durch. Der Aufbau neuronaler Netzwerkmodelle und die Übertragung von Datenströmen werden noch auf der CPU durchgeführt. Der Interaktionsprozess zwischen CPU und GPU: GPU-Informationen abrufen, GPU-ID konfigurieren, Neuronenparameter auf die GPU laden, GPU-Beschleunigung der neuronalen Netzwerkberechnung und GPU-Berechnungsergebnisse empfangen.

Warum GPU im Bereich des autonomen Fahrens so wichtig ist

Eine der wichtigsten technischen Kategorien in der autonomen Fahrtechnologie ist Deep Learning. Künstliche Intelligenz basierend auf Deep-Learning-Architektur Heute weit verbreitet In verschiedenen Bereichen der Automobilindustrie wie Computer Vision, Verarbeitung natürlicher Sprache, Sensorfusion, Zielerkennung und autonomem Fahren, von Start-ups für autonomes Fahren über Internetunternehmen bis hin zu großen OEMs, wird der Einsatz von GPUs aktiv erforscht um neuronale Netze aufzubauen, um das ultimative Ziel zu erreichen.

Nach der Geburt des GPU-beschleunigten Computings bietet es eine Multi-Core-Parallel-Computing-Architektur für Unternehmensdaten und unterstützt Datenquellen, die frühere CPU-Architekturen nicht verarbeiten konnten. Im Vergleich dazu betragen die Kosten für die Verwendung eines GPU-Computing-Clusters für die Durchführung derselben Deep-Learning-Trainingsaufgabe nur 1/200 der Kosten eines CPU-Computing-Clusters.

GPU ist der Schlüssel zum autonomen Fahren und Deep Learning

Ob es dem Auto ermöglicht, die umgebende Echtzeitumgebung in Echtzeit wahrzunehmen oder Fahrrouten und Aktionen schnell zu planen, all dies erfordert die Das Gehirn des Autos muss schnell reagieren, daher ist es für die Hardwarehersteller sehr wichtig, dass beim autonomen Fahren Algorithmen für tiefes Lernen oder künstliche Intelligenz benötigt werden, um mit unendlich vielen möglichen Situationen umzugehen , Deep Learning und fahrerloses Fahren haben ein goldenes Zeitalter der GPU-Computing-Entwicklung eingeläutet.

Ein weiterer wichtiger Parameter der GPU ist die Fähigkeit zur Gleitkommaberechnung. Beim Gleitkommazählen werden Gleitkommazahlen verwendet, um eine Zahl mithilfe von Binärzahlen unterschiedlicher Länge darzustellen, die Festkommazahlen entsprechen. Bei der Iteration des autonomen Fahralgorithmus sind die Präzisionsanforderungen hoch und es ist Unterstützung für den Gleitkommabetrieb erforderlich.

FPGA-Lösung

FPGA-Chip-Definition und -Struktur

FPGA (Field-Programmable Gate Array), ein feldprogrammierbares Gate-Array, ist ein Weiterentwicklungsprodukt, das auf programmierbaren Geräten wie PAL, GAL und CPLD basiert. Es handelt sich um eine semi-kundenspezifische Schaltung im Bereich anwendungsspezifischer integrierter Schaltkreise, die nicht nur die Mängel kundenspezifischer Schaltkreise behebt, sondern auch die Mängel der begrenzten Anzahl von Gate-Schaltkreisen der ursprünglichen programmierbaren Geräte überwindet.

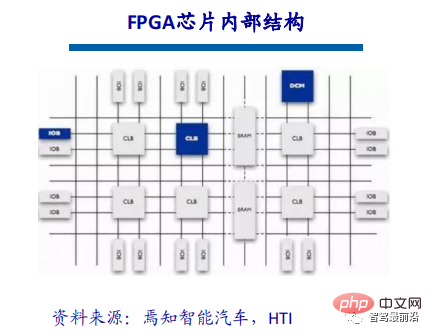

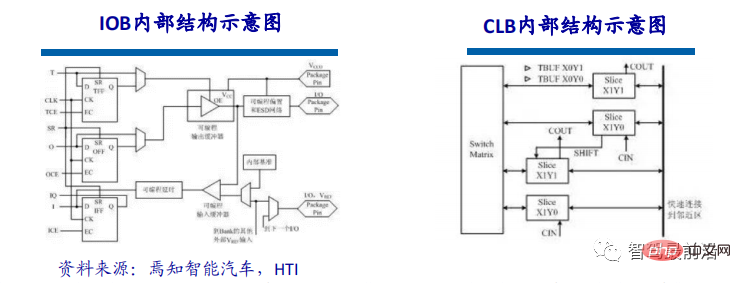

Der FPGA-Chip besteht hauptsächlich aus 6 Teilen, nämlich: programmierbare Eingabe- und Ausgabeeinheit, grundlegende programmierbare Logikeinheit, vollständiges Taktmanagement, eingebetteter Block-RAM, umfangreiche Verkabelungsressourcen, eingebettete zugrunde liegende Funktionseinheit und internes eingebettetes spezielles Hardwaremodul. Das aktuelle Mainstream-FPGA basiert immer noch auf der Look-up-Table-Technologie, die die Grundleistung früherer Versionen weit übertrifft, und integriert Hardcore-Module (ASIC-Typ) mit gemeinsamen Funktionen (wie RAM, Taktverwaltung und DSP). .

Funktionsprinzip von FPGA

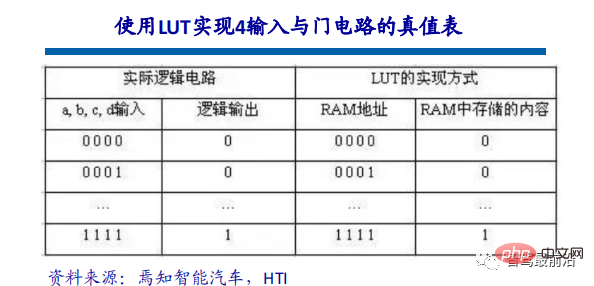

Da FPGA wiederholt programmiert werden muss, kann die Grundstruktur seiner kombinatorischen Logik nicht durch feste NAND-Gatter wie ASIC vervollständigt werden, sondern kann nur eine Struktur übernehmen Das ist immer wieder einfach zu konfigurieren. Lookup-Tabellen können diese Anforderung gut erfüllen. Derzeit verwenden gängige FPGAs Lookup-Tabellenstrukturen, die auf SRAM-Technologie basieren. Es gibt auch einige FPGAs für den Militär- und Luft- und Raumfahrtbereich, die Lookup-Tabellenstrukturen verwenden, die auf Flash- oder Fuse- und Antifuse-Technologie basieren. Die wiederholte Konfiguration des FPGA wird durch das Brennen von Dateien erreicht, um den Inhalt der Nachschlagetabelle zu ändern.

Look-Up-Table wird als LUT bezeichnet und LUT ist im Wesentlichen ein RAM. Derzeit werden LUTs mit 4 Eingängen hauptsächlich in FPGAs verwendet, sodass jede LUT als RAM mit 4-Bit-Adressleitungen betrachtet werden kann. Wenn der Benutzer eine Logikschaltung mithilfe eines Schaltplans oder der HDL-Sprache beschreibt, berechnet die PLD/FPGA-Entwicklungssoftware automatisch alle möglichen Ergebnisse der Logikschaltung und schreibt die Wahrheitstabelle (dh das Ergebnis) im Voraus in den RAM. Jedes Mal, wenn ein Signal eingegeben wird. Das Durchführen logischer Operationen entspricht der Eingabe einer Adresse, dem Nachschlagen in der Tabelle, dem Ermitteln des der Adresse entsprechenden Inhalts und der anschließenden Ausgabe.

Die programmierbare Eingabe-/Ausgabeeinheit, auch I/O-Einheit genannt, ist der Schnittstellenteil zwischen dem Chip und der externen Schaltung und erfüllt die Treiber- und Anpassungsanforderungen für Eingabe-/Ausgabesignale unter verschiedenen Bedingungen elektrische Eigenschaften. Die E/A innerhalb des FPGA ist in Gruppen eingeteilt, und jede Gruppe kann unabhängig voneinander verschiedene E/A-Standards unterstützen. Durch die flexible Konfiguration der Software kann sie sich an unterschiedliche elektrische Standards und physikalische E/A-Eigenschaften anpassen, den Antriebsstrom anpassen und die Pull-up- und Pull-down-Widerstände ändern. Derzeit wird die Frequenz der I/O-Ports immer höher und einige High-End-FPGAs können durch DDR-Registertechnologie Datenraten von bis zu 2 Gbit/s unterstützen.

CLB ist die grundlegende Logikeinheit innerhalb des FPGA. Die tatsächliche Anzahl und Eigenschaften der CLBs variieren von Gerät zu Gerät, aber jeder CLB enthält eine konfigurierbare Schaltmatrix bestehend aus 4 oder 6 Eingängen, einigen Auswahlschaltkreisen (Multiplexern usw.) und einer Flip-Flop-Zusammensetzung. Die Schaltmatrix ist äußerst flexibel und kann für die Verarbeitung von kombinatorischer Logik, Schieberegistern oder RAM konfiguriert werden. In den FPGA-Geräten von Xilinx besteht CLB aus mehreren (normalerweise 4 oder 2) identischen Slices und zusätzlicher Logik. Jedes CLB-Modul kann nicht nur zur Implementierung von kombinatorischer Logik und sequentieller Logik verwendet werden, sondern kann auch als verteiltes RAM und verteiltes ROM konfiguriert werden.

Der „Kern“-Killer des autonomen Fahrens

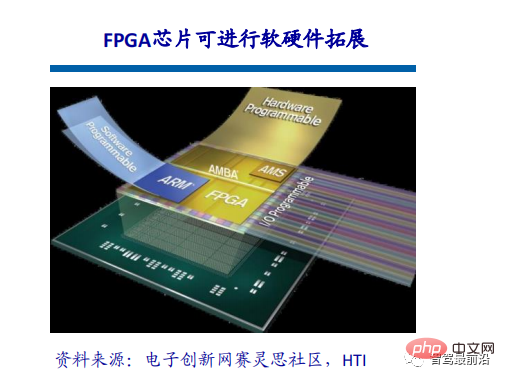

Die Marktsegmente autonomes Fahren und fortschrittliche Fahrerassistenzsysteme (ADAS) befinden sich im Wandel und stellen neue und komplexe Anforderungen an Computer und Sensoren Fähigkeiten. FPGA bietet einzigartige Vorteile, mit denen andere Chiplösungen nicht mithalten können, und ist eine ausgezeichnete Wahl, um den kontinuierlichen Entwicklungen und Veränderungen der autonomen Fahrbranche gerecht zu werden. FPGA ist eine spezielle Technologie im Chipbereich, die einerseits über Softwaretools wiederholt konfiguriert werden kann und andererseits über umfangreiche IO-Schnittstellen und Recheneinheiten verfügt. Daher kann FPGA entsprechend den spezifischen Anforderungen des Anwendungsszenarios gleichzeitig Pipeline-Parallelität und Datenparallelität verarbeiten und bietet die inhärenten Vorteile einer hohen Rechenleistung, einer geringen Latenz und eines geringen Stromverbrauchs.

FPGA bietet viele Vorteile wie hohen Durchsatz, hohe Energieeffizienz und Echtzeitverarbeitung, was sich sehr gut für die technischen Anforderungen des autonomen Fahrens eignet. Standards und Anforderungen für Advanced Assisted Driving Systems (ADAS) und In-Vehicle Experience (IVE)-Anwendungen entwickeln sich rasant weiter. Zu den Hauptanliegen der Systementwickler gehören hervorragende Flexibilität und schnellere Entwicklungszyklen bei gleichzeitiger Aufrechterhaltung eines höheren Leistungs-Leistungs-Verhältnisses. Die Kombination aus umprogrammierbaren FPGAs und einem wachsenden Portfolio an Automobilprodukten ermöglicht es Automobildesignern, Designanforderungen zu erfüllen und der sich ständig verändernden Automobilindustrie einen Schritt voraus zu sein.

Eine anpassungsfähigere Plattform

Der wahre Wert für autonome Fahrchips liegt in der Nutzung der Berechnungsmaschine, also im Unterschied zwischen theoretischer und tatsächlicher Leistung. FPGAs enthalten eine große Anzahl von Routing-Links sowie eine große Menge an kleinem Speicher. Die Kombination dieser Ressourcen ermöglicht es Designern, maßgeschneiderte Datenfeed-Netzwerke für ihre Rechenmaschinen zu erstellen und so eine höhere Auslastung zu erreichen. Programmierbare Logik bietet Kunden ein hohes Maß an Flexibilität, um sich an die sich ändernden Anforderungen neuer Anwendungsbereiche wie ADAS und autonomes Fahren anzupassen. Um die Vorteile verbesserter Schnittstellenstandards, Algorithmeninnovationen und neuer Sensortechnologien nutzen zu können, ist eine anpassungsfähige Plattform erforderlich, die nicht nur Softwareänderungen, sondern auch Hardwareänderungen unterstützen kann. Hier zeichnen sich FPGA-Chips aus.

FPGA-Chips sind skalierbar. Skalierbare Chips verändern den Umfang der programmierbaren Logik, meist in Pin-kompatiblen Gehäusen. Dies bedeutet, dass Entwickler eine einzige ECU-Plattform erstellen können, um niedrige, mittlere und hohe Versionen von ADAS-Funktionspaketen zu hosten und die Kosten je nach Bedarf zu skalieren, indem sie den erforderlichen Chip mit der minimalen Dichte auswählen.

Differenzierte Lösungen

Mit FPGA-Chips können Entwickler einzigartige differenzierte Verarbeitungslösungen erstellen, die für bestimmte Anwendungen oder Sensoren optimiert werden können. Dies ist mit ASSP-Chips nicht möglich, und selbst solche, die dedizierte Beschleuniger anbieten, sind in deren Einsatzmöglichkeiten eingeschränkt und stehen im Wesentlichen allen Wettbewerbern zur Verfügung. Langjährige Xilinx-Kunden haben beispielsweise Bibliotheken mit hochwertigem IP erstellt, auf die nur sie zugreifen können, und diese Funktionen können in den verschiedenen Produkten des Unternehmens genutzt werden. Beginnend mit dem 90-nm-Knoten erwiesen sich Xilinx-Chips als äußerst kosteneffektiv für großvolumige Automobilanwendungen, wobei mehr als 160 Millionen Xilinx-Chips in der Branche eingesetzt werden.

ASIC-Lösung

ASIC-Definition und -Eigenschaften

ASIC-Chips können entsprechend verschiedenen Terminalfunktionen in TPU-Chips, DPU-Chips und NPU-Chips unterteilt werden. Unter ihnen ist TPU ein Tensorprozessor, der sich dem maschinellen Lernen widmet. Beispielsweise hat Google im Mai 2016 einen programmierbaren KI-Beschleuniger für die Tensorflow-Plattform entwickelt. Sein interner Befehlssatz kann ausgeführt werden, wenn sich das Tensorflow-Programm ändert oder der Algorithmus aktualisiert wird. DPU ist eine Datenverarbeitungseinheit, die Engines für Rechenszenarien wie Rechenzentren bereitstellen kann. NPU ist ein neuronaler Netzwerkprozessor, der menschliche Neuronen und Synapsen auf Schaltkreisebene simuliert und Deep-Learning-Befehlssätze verwendet, um umfangreiche elektronische Neuronen- und Synapsendaten direkt zu verarbeiten.

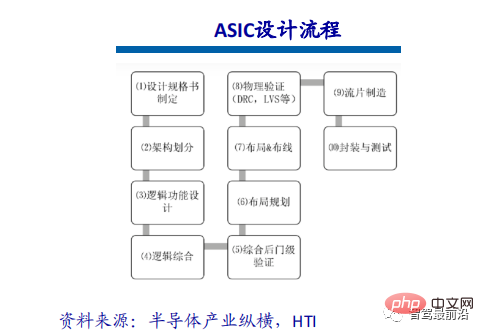

ASIC verfügt über zwei Designmethoden: vollständige Anpassung und Halbanpassung. Die vollständige Anpassung erfordert enorme Personal- und Zeitkosten, um den gesamten Entwurfsprozess für integrierte Schaltkreise vollständig unabhängig abzuschließen. Obwohl sie flexibler und besser als halbkundenspezifische ASICs sind, ist ihre Entwicklungseffizienz im Vergleich zu halbkundenspezifischen ASICs sehr gering.

Offensichtliche Leistungsverbesserung

ASIC-Chips eignen sich sehr gut für Anwendungsszenarien der künstlichen Intelligenz. Beispielsweise verfügt NVIDIAs erster Chip, Tesla P100, der von Grund auf für Deep Learning entwickelt wurde, über eine Datenverarbeitungsgeschwindigkeit, die zwölfmal so hoch ist wie die der 2014 eingeführten GPU-Serie. Googles maßgeschneiderter Chip-TPU für maschinelles Lernen verbessert die Hardwareleistung sieben Jahre nach der Entwicklung des Mooreschen Gesetzes auf ein Niveau, das dem aktueller Chips entspricht. So wie CPUs die riesigen Computer der Vergangenheit verändert haben, werden ASIC-Chips mit künstlicher Intelligenz auch das Gesicht der heutigen KI-Hardwaregeräte erheblich verändern. Das berühmte AlphaGo verwendet beispielsweise etwa 170 Grafikprozessoren (GPUs) und 1.200 Zentraleinheiten (CPUs). Diese Geräte erfordern einen Computerraum, eine leistungsstarke Klimaanlage und mehrere Experten für die Systemwartung. Und wenn alle dedizierten Chips verwendet werden, wird höchstwahrscheinlich nur Platz in der Größe einer gewöhnlichen Aufbewahrungsbox benötigt und der Stromverbrauch wird erheblich reduziert.

Der ASIC-Technologieweg ist begrenzt und offen, und Chipunternehmen müssen sich für Mainstream-Netzwerke, -Modelle und -Betreiber im Zusammenhang mit dem Fahren entwickeln. Bei gleicher Leistung ist die Chipfläche kleiner, die Kosten geringer und der Stromverbrauch geringer. Der ASIC-Technologieweg wird in Zukunft großes Potenzial haben. Die Wahl des ASIC-Weges bedeutet nicht, unterschiedliche ASICs für unterschiedliche Modelle zu entwickeln oder unterschiedliche Verifizierungen durchzuführen. Da die Funktionen, die verschiedene Modelle implementieren müssen, ungefähr gleich sind und der Chip nur begrenzten Zugriff auf Modelle und Operatoren hat, hat eine schnelle Iteration des Algorithmus keinen Einfluss auf die Unterstützung des Chips für Funktionen der oberen Schicht. Automobilhersteller arbeiten mit Chipdesign-Unternehmen zusammen, um eine differenzierte Anpassung oder eine bessere Auswahl zu ermöglichen. Denn selbst bei differenzierter Individualisierung sind 50 % der internen Teile des Chips universell. Chipdesign-Unternehmen können differenzierte Designs basierend auf der Originalversion durchführen, um einige differenzierte Funktionen zu erreichen.

Vergleich gängiger Architekturlösungen: drei gängige Architekturen

FPGA ist ein Produkt, das auf Basis programmierbarer Geräte wie PAL und GAL weiterentwickelt wird. Es handelt sich um eine semi-kundenspezifische Schaltung im Bereich anwendungsspezifischer integrierter Schaltkreise, die nicht nur die Mängel kundenspezifischer Schaltkreise behebt, sondern auch die Mängel der begrenzten Anzahl von Gate-Schaltkreisen der ursprünglichen programmierbaren Geräte überwindet. Vorteile: unbegrenzte Programmierung, geringe Latenz, Pipeline-Parallelität und Datenparallelität, stärkste Echtzeitleistung und höchste Flexibilität. Nachteile: Es ist schwierig zu entwickeln, nur für Festkommaoperationen geeignet und relativ teuer.

Graphics Processing Unit (GPU), auch bekannt als Display Core, Visual Processor, Display Chip, ist eine Art Grafikprozessor, der auf die Bild- und Verarbeitung auf PCs, Workstations, Spielekonsolen und einigen mobilen Geräten (z. B (z. B. Tablets, Mobiltelefone usw.) Ein Mikroprozessor, der grafikbezogene Vorgänge ausführt. Vorteile: Es bietet die Grundstruktur des parallelen Mehrkern-Computings und verfügt über eine sehr große Anzahl von Kernen, die das parallele Computing großer Datenmengen unterstützen können und über höhere Gleitkomma-Computing-Fähigkeiten verfügen. Nachteile: Managementkontrollfähigkeit (am schwächsten), Stromverbrauch (am höchsten).

ASIC oder anwendungsspezifischer integrierter Schaltkreis bezieht sich auf einen integrierten Schaltkreis, der als Reaktion auf spezifische Benutzeranforderungen und die Anforderungen spezifischer elektronischer Systeme entwickelt und hergestellt wird. Derzeit ist CPLD (Complex Programmable Logic Device) und FPGA (Field Programmable Logic Array) eine der beliebtesten Möglichkeiten, ASICs zu entwerfen. Vorteile: Als Produkt der integrierten Schaltkreistechnologie und der vollständigen Maschinen- oder Systemtechnologie eines bestimmten Benutzers weist es im Vergleich zu allgemeinen integrierten Schaltkreisen eine geringere Größe, ein geringeres Gewicht, einen geringeren Stromverbrauch, eine verbesserte Zuverlässigkeit, eine verbesserte Leistung und eine höhere Vertraulichkeit auf. Kostenreduzierung und andere Vorteile. Nachteile: Unzureichende Flexibilität und teurer als FPGA.

Einschränkungen der Rechenleistungstheorie: Die Rechenleistung von TOPS entspricht nicht vollständig der tatsächlichen Leistung

Mit dem Aufkommen von ADAS, autonomer Fahrtechnologie und der allmählichen Vertiefung softwaredefinierter Autos , intelligente Autos Der Bedarf an Rechenleistung und enormen Datenverarbeitungskapazitäten ist sprunghaft angestiegen, und die Chip-„Stacking“-Lösung herkömmlicher Automobile kann den Rechenleistungsbedarf des autonomen Fahrens nicht mehr decken. Der Chip dient letztendlich der fahrzeuginternen Computerplattform des Automobilherstellers. Bei „softwaredefinierten Autos“ kann das Unterstützungsproblem der Computerplattform für intelligente Fahrsysteme nicht nur durch Stapeln der Chip-Rechenleistung gelöst werden.

Der Chip ist die Bühne für Software. Der Maßstab für die Messung der Qualität des Chips hängt davon ab, ob die Software auf dem Chip seine Funktion maximieren kann. Es muss eine effektive Übereinstimmung zwischen Rechenleistung und Software bestehen. Wenn man zwei Chips mit der gleichen Rechenleistung vergleicht, ist der Chip, der die Software effizienter laufen lässt, der „gute Chip“. Die wichtigsten Faktoren, die den wahren Wert der Rechenleistung bestimmen, sind die Speicherbandbreite (SRAM und DRAM) sowie die tatsächliche Betriebsfrequenz (d. h. Versorgungsspannung oder Temperatur) und die Stapelgröße des Algorithmus.

Die Rechenleistung TOPS eines einzelnen Chips ist ein wichtiger Indikator, aber nicht der einzige. Autonomes Fahren ist ein komplexes System, das eine Zusammenarbeit zwischen Fahrzeug, Straße und Cloud-Edge erfordert. Daher umfasst der Wettbewerb neben dem Kern auch Software- und Hardware-Synergien, Plattformen, Toolketten usw. Der grenzenlose Ausbau der Chip-Rechenleistung und der eingebetteten Hardware wird nicht der zukünftige Trend sein, und auch die Hardware muss der tatsächlichen Situation entsprechen. Dahinter verbirgt sich das Problem eines hohen Stromverbrauchs und einer geringen Auslastung.

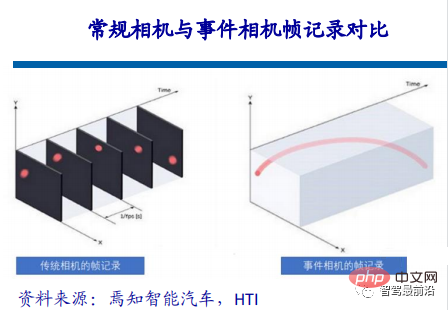

... Das biologische Sehen reagiert nur auf Bereiche mit Veränderungen, und Ereigniskameras erfassen das Auftreten von Ereignissen oder Veränderungen. ,

Der Funktionsmechanismus der Ereigniskamera besteht darin, dass die Kamera ein Ereignis im oben genannten Format zurückgibt, wenn sich die Helligkeit eines bestimmten Pixels auf einen bestimmten Schwellenwert ändert. Die ersten beiden Elemente sind die Pixelkoordinaten des Ereignisses. und das dritte Element ist der Zeitstempel des Ereignisses, und das letzte Element ist die Polarität (Polarität) 0, 1 (oder -1, 1), die angibt, ob die Helligkeit von niedrig nach hoch oder von hoch nach niedrig reicht.

Solange sich der Pixelwert im gesamten Sichtfeld der Kamera ändert, wird ein Ereignis zurückgegeben. Alle diese Ereignisse treten asynchron auf (egal wie klein das Zeitintervall ist, sie können nicht auftreten). Da die Zeitstempel der Ereignisse vollständig gleichzeitig sind, sind sie unterschiedlich. Aufgrund der einfachen Rückgabe ist die Latenz im Vergleich zu herkömmlichen Kameras gering und die Latenz beträgt Mikrosekunden.

Anwendung im Bereich des autonomen Fahrens

Die heute im Bereich des autonomen Fahrens verwendeten visuellen Erkennungsalgorithmen basieren im Wesentlichen auf Faltungs-Neuronalen Netzen, und die Funktionsweise des visuellen Algorithmus ist im Wesentlichen wiederholte Faltungsoperation. Diese Art der Berechnung ist im Wesentlichen nicht kompliziert, sie umfasst nur Addition, Subtraktion, Multiplikation und Division, also eine Art Multiplikations-, Akkumulations- und Akkumulationsoperation. Allerdings gibt es solche einfachen Operationen in großen Mengen in Faltungs-Neuronalen Netzen, was hohe Anforderungen an die Leistung des Prozessors stellt.

Nehmen Sie ResNet-152 als Beispiel. Dies ist ein 152-schichtiges Faltungsnetzwerk. Der Rechenaufwand beträgt etwa 22,6 Milliarden Mal, wenn dieses Netzwerk ein 1080P-Bild verarbeiten möchte Für eine 30-Bild-Kamera beträgt die erforderliche Rechenleistung bis zu 33 Billionen Mal pro Sekunde, was sehr enorm ist.

Rechenleistung sparen durch Reduzierung ungültiger Berechnungen

99 % der visuellen Daten im Bereich des autonomen Fahrens sind nutzloser Hintergrund in der KI-Verarbeitung. Bei der Erkennung von Geistersonden ist der geänderte Bereich beispielsweise nur ein sehr kleiner Teil, aber die herkömmliche visuelle Verarbeitung muss immer noch 99 % der Hintergrundbereiche verarbeiten, die sich nicht ändern, was nicht nur viel Rechenleistung, sondern auch Zeit verschwendet . Oder wenn sich ein Diamant im Kies befindet, müssen der KI-Chip und herkömmliche Kameras jedes Sandkorn identifizieren und die Diamanten aussortieren, aber Menschen können Diamanten mit nur einem Blick erkennen. Der KI-Chip und herkömmliche Kameras erfassen dies 100-mal oder 1000-mal länger als der Mensch.

Neben den Vorteilen reduzierter redundanter Informationen und nahezu keiner Verzögerung liegen die Vorteile von Eventkameras auch in der geringen Latenz. Bei der Aufnahme von Hochgeschwindigkeitsobjekten kommt es bei herkömmlichen Kameras aufgrund der Belichtungszeit zu Unschärfen Eventkameras haben nahezu keine Unschärfe. Darüber hinaus verfügt die Event-Kamera über einen wirklich hohen Dynamikbereich. Aufgrund der Eigenschaften der Event-Kamera sind herkömmliche Kameras in Umgebungen mit starker oder schwacher Lichtintensität „blind“, die Pixeländerungen sind jedoch weiterhin vorhanden, sodass die Event-Kamera dies kann sehe immer noch etwas klar.

Das obige ist der detaillierte Inhalt vonEin Überblick über die drei gängigen Chiparchitekturen für autonomes Fahren in einem Artikel. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!

Heiße KI -Werkzeuge

Undresser.AI Undress

KI-gestützte App zum Erstellen realistischer Aktfotos

AI Clothes Remover

Online-KI-Tool zum Entfernen von Kleidung aus Fotos.

Undress AI Tool

Ausziehbilder kostenlos

Clothoff.io

KI-Kleiderentferner

AI Hentai Generator

Erstellen Sie kostenlos Ai Hentai.

Heißer Artikel

Heiße Werkzeuge

Notepad++7.3.1

Einfach zu bedienender und kostenloser Code-Editor

SublimeText3 chinesische Version

Chinesische Version, sehr einfach zu bedienen

Senden Sie Studio 13.0.1

Leistungsstarke integrierte PHP-Entwicklungsumgebung

Dreamweaver CS6

Visuelle Webentwicklungstools

SublimeText3 Mac-Version

Codebearbeitungssoftware auf Gottesniveau (SublimeText3)

Heiße Themen

1376

1376

52

52

Warum ist Gaussian Splatting beim autonomen Fahren so beliebt, dass NeRF allmählich aufgegeben wird?

Jan 17, 2024 pm 02:57 PM

Warum ist Gaussian Splatting beim autonomen Fahren so beliebt, dass NeRF allmählich aufgegeben wird?

Jan 17, 2024 pm 02:57 PM

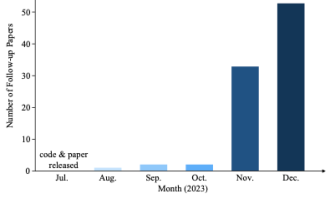

Oben geschrieben und persönliches Verständnis des Autors. Dreidimensionales Gaussplatting (3DGS) ist eine transformative Technologie, die in den letzten Jahren in den Bereichen explizite Strahlungsfelder und Computergrafik entstanden ist. Diese innovative Methode zeichnet sich durch die Verwendung von Millionen von 3D-Gaußkurven aus, was sich stark von der Neural Radiation Field (NeRF)-Methode unterscheidet, die hauptsächlich ein implizites koordinatenbasiertes Modell verwendet, um räumliche Koordinaten auf Pixelwerte abzubilden. Mit seiner expliziten Szenendarstellung und differenzierbaren Rendering-Algorithmen garantiert 3DGS nicht nur Echtzeit-Rendering-Fähigkeiten, sondern führt auch ein beispielloses Maß an Kontrolle und Szenenbearbeitung ein. Dies positioniert 3DGS als potenziellen Game-Changer für die 3D-Rekonstruktion und -Darstellung der nächsten Generation. Zu diesem Zweck geben wir erstmals einen systematischen Überblick über die neuesten Entwicklungen und Anliegen im Bereich 3DGS.

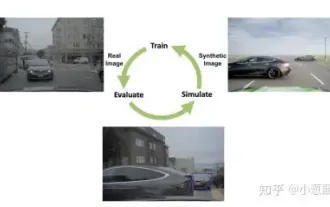

Wie lässt sich das Long-Tail-Problem in autonomen Fahrszenarien lösen?

Jun 02, 2024 pm 02:44 PM

Wie lässt sich das Long-Tail-Problem in autonomen Fahrszenarien lösen?

Jun 02, 2024 pm 02:44 PM

Gestern wurde ich während des Interviews gefragt, ob ich irgendwelche Long-Tail-Fragen gestellt hätte, also dachte ich, ich würde eine kurze Zusammenfassung geben. Das Long-Tail-Problem des autonomen Fahrens bezieht sich auf Randfälle bei autonomen Fahrzeugen, also mögliche Szenarien mit geringer Eintrittswahrscheinlichkeit. Das wahrgenommene Long-Tail-Problem ist einer der Hauptgründe, die derzeit den betrieblichen Designbereich intelligenter autonomer Einzelfahrzeugfahrzeuge einschränken. Die zugrunde liegende Architektur und die meisten technischen Probleme des autonomen Fahrens wurden gelöst, und die verbleibenden 5 % der Long-Tail-Probleme wurden nach und nach zum Schlüssel zur Einschränkung der Entwicklung des autonomen Fahrens. Zu diesen Problemen gehören eine Vielzahl fragmentierter Szenarien, Extremsituationen und unvorhersehbares menschliches Verhalten. Der „Long Tail“ von Randszenarien beim autonomen Fahren bezieht sich auf Randfälle in autonomen Fahrzeugen (AVs). Randfälle sind mögliche Szenarien mit geringer Eintrittswahrscheinlichkeit. diese seltenen Ereignisse

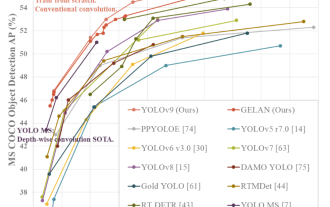

YOLO ist unsterblich! YOLOv9 wird veröffentlicht: Leistung und Geschwindigkeit SOTA~

Feb 26, 2024 am 11:31 AM

YOLO ist unsterblich! YOLOv9 wird veröffentlicht: Leistung und Geschwindigkeit SOTA~

Feb 26, 2024 am 11:31 AM

Heutige Deep-Learning-Methoden konzentrieren sich darauf, die am besten geeignete Zielfunktion zu entwerfen, damit die Vorhersageergebnisse des Modells der tatsächlichen Situation am nächsten kommen. Gleichzeitig muss eine geeignete Architektur entworfen werden, um ausreichend Informationen für die Vorhersage zu erhalten. Bestehende Methoden ignorieren die Tatsache, dass bei der schichtweisen Merkmalsextraktion und räumlichen Transformation der Eingabedaten eine große Menge an Informationen verloren geht. Dieser Artikel befasst sich mit wichtigen Themen bei der Datenübertragung über tiefe Netzwerke, nämlich Informationsengpässen und umkehrbaren Funktionen. Darauf aufbauend wird das Konzept der programmierbaren Gradienteninformation (PGI) vorgeschlagen, um die verschiedenen Änderungen zu bewältigen, die tiefe Netzwerke zur Erreichung mehrerer Ziele erfordern. PGI kann vollständige Eingabeinformationen für die Zielaufgabe zur Berechnung der Zielfunktion bereitstellen und so zuverlässige Gradienteninformationen zur Aktualisierung der Netzwerkgewichte erhalten. Darüber hinaus wird ein neues, leichtgewichtiges Netzwerk-Framework entworfen

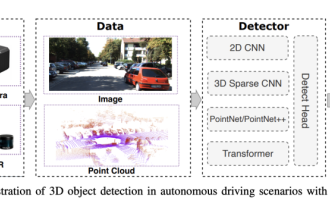

Kamera oder Lidar wählen? Eine aktuelle Übersicht über die Erzielung einer robusten 3D-Objekterkennung

Jan 26, 2024 am 11:18 AM

Kamera oder Lidar wählen? Eine aktuelle Übersicht über die Erzielung einer robusten 3D-Objekterkennung

Jan 26, 2024 am 11:18 AM

0. Vorab geschrieben&& Persönliches Verständnis, dass autonome Fahrsysteme auf fortschrittlichen Wahrnehmungs-, Entscheidungs- und Steuerungstechnologien beruhen, indem sie verschiedene Sensoren (wie Kameras, Lidar, Radar usw.) verwenden, um die Umgebung wahrzunehmen, und Algorithmen und Modelle verwenden für Echtzeitanalysen und Entscheidungsfindung. Dies ermöglicht es Fahrzeugen, Verkehrszeichen zu erkennen, andere Fahrzeuge zu erkennen und zu verfolgen, das Verhalten von Fußgängern vorherzusagen usw. und sich so sicher an komplexe Verkehrsumgebungen anzupassen. Diese Technologie erregt derzeit große Aufmerksamkeit und gilt als wichtiger Entwicklungsbereich für die Zukunft des Transportwesens . eins. Aber was autonomes Fahren schwierig macht, ist herauszufinden, wie man dem Auto klarmachen kann, was um es herum passiert. Dies erfordert, dass der dreidimensionale Objekterkennungsalgorithmus im autonomen Fahrsystem Objekte in der Umgebung, einschließlich ihrer Standorte, genau wahrnehmen und beschreiben kann.

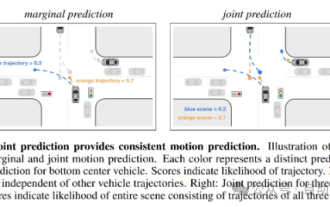

Dieser Artikel reicht aus, um etwas über autonomes Fahren und Flugbahnvorhersage zu lesen!

Feb 28, 2024 pm 07:20 PM

Dieser Artikel reicht aus, um etwas über autonomes Fahren und Flugbahnvorhersage zu lesen!

Feb 28, 2024 pm 07:20 PM

Die Trajektorienvorhersage spielt eine wichtige Rolle beim autonomen Fahren. Unter autonomer Fahrtrajektorienvorhersage versteht man die Vorhersage der zukünftigen Fahrtrajektorie des Fahrzeugs durch die Analyse verschiedener Daten während des Fahrvorgangs. Als Kernmodul des autonomen Fahrens ist die Qualität der Trajektorienvorhersage von entscheidender Bedeutung für die nachgelagerte Planungssteuerung. Die Trajektorienvorhersageaufgabe verfügt über einen umfangreichen Technologie-Stack und erfordert Vertrautheit mit der dynamischen/statischen Wahrnehmung des autonomen Fahrens, hochpräzisen Karten, Fahrspurlinien, Fähigkeiten in der neuronalen Netzwerkarchitektur (CNN&GNN&Transformer) usw. Der Einstieg ist sehr schwierig! Viele Fans hoffen, so schnell wie möglich mit der Flugbahnvorhersage beginnen zu können und Fallstricke zu vermeiden. Heute werde ich eine Bestandsaufnahme einiger häufiger Probleme und einführender Lernmethoden für die Flugbahnvorhersage machen! Einführungsbezogenes Wissen 1. Sind die Vorschaupapiere in Ordnung? A: Schauen Sie sich zuerst die Umfrage an, S

SIMPL: Ein einfacher und effizienter Multi-Agent-Benchmark zur Bewegungsvorhersage für autonomes Fahren

Feb 20, 2024 am 11:48 AM

SIMPL: Ein einfacher und effizienter Multi-Agent-Benchmark zur Bewegungsvorhersage für autonomes Fahren

Feb 20, 2024 am 11:48 AM

Originaltitel: SIMPL: ASimpleandEfficientMulti-agentMotionPredictionBaselineforAutonomousDriving Paper-Link: https://arxiv.org/pdf/2402.02519.pdf Code-Link: https://github.com/HKUST-Aerial-Robotics/SIMPL Autor: Hong Kong University of Science und Technologie DJI-Papieridee: Dieses Papier schlägt eine einfache und effiziente Bewegungsvorhersagebasislinie (SIMPL) für autonome Fahrzeuge vor. Im Vergleich zum herkömmlichen Agent-Cent

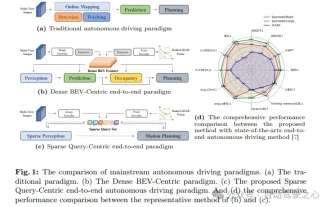

nuScenes' neuestes SOTA |. SparseAD: Sparse-Abfrage hilft effizientes durchgängiges autonomes Fahren!

Apr 17, 2024 pm 06:22 PM

nuScenes' neuestes SOTA |. SparseAD: Sparse-Abfrage hilft effizientes durchgängiges autonomes Fahren!

Apr 17, 2024 pm 06:22 PM

Vorab geschrieben und Ausgangspunkt Das End-to-End-Paradigma verwendet ein einheitliches Framework, um Multitasking in autonomen Fahrsystemen zu erreichen. Trotz der Einfachheit und Klarheit dieses Paradigmas bleibt die Leistung von End-to-End-Methoden für das autonome Fahren bei Teilaufgaben immer noch weit hinter Methoden für einzelne Aufgaben zurück. Gleichzeitig erschweren die in früheren End-to-End-Methoden weit verbreiteten Funktionen der dichten Vogelperspektive (BEV) die Skalierung auf mehr Modalitäten oder Aufgaben. Hier wird ein Sparse-Search-zentriertes End-to-End-Paradigma für autonomes Fahren (SparseAD) vorgeschlagen, bei dem die Sparse-Suche das gesamte Fahrszenario, einschließlich Raum, Zeit und Aufgaben, ohne dichte BEV-Darstellung vollständig abbildet. Insbesondere ist eine einheitliche, spärliche Architektur für die Aufgabenerkennung einschließlich Erkennung, Verfolgung und Online-Zuordnung konzipiert. Zudem schwer

Sprechen wir über End-to-End- und autonome Fahrsysteme der nächsten Generation sowie über einige Missverständnisse über End-to-End-Autonomes Fahren?

Apr 15, 2024 pm 04:13 PM

Sprechen wir über End-to-End- und autonome Fahrsysteme der nächsten Generation sowie über einige Missverständnisse über End-to-End-Autonomes Fahren?

Apr 15, 2024 pm 04:13 PM

Im vergangenen Monat hatte ich aus bekannten Gründen einen sehr intensiven Austausch mit verschiedenen Lehrern und Mitschülern der Branche. Ein unvermeidliches Thema im Austausch ist natürlich End-to-End und der beliebte Tesla FSDV12. Ich möchte diese Gelegenheit nutzen, einige meiner aktuellen Gedanken und Meinungen als Referenz und Diskussion darzulegen. Wie definiert man ein durchgängiges autonomes Fahrsystem und welche Probleme sollten voraussichtlich durchgängig gelöst werden? Gemäß der traditionellsten Definition bezieht sich ein End-to-End-System auf ein System, das Rohinformationen von Sensoren eingibt und für die Aufgabe relevante Variablen direkt ausgibt. Bei der Bilderkennung kann CNN beispielsweise als End-to-End bezeichnet werden, verglichen mit der herkömmlichen Methode zum Extrahieren von Merkmalen + Klassifizieren. Bei autonomen Fahraufgaben werden Eingabedaten verschiedener Sensoren (Kamera/LiDAR) benötigt