Kann der Tesla-Supercomputing-Chip GPGPU übertreffen?

Autor: Chen Wei, Ph.D., Experte für Speicher und Computer/GPU-Architektur und KI, leitende Berufsbezeichnung. Zhongguancun Cloud Computing Industry Alliance, Experte der China Optical Engineering Society, Mitglied der International Computer Federation (ACM), professionelles Mitglied der China Computer Federation (CCF). Er war früher leitender Wissenschaftler eines KI-Unternehmens und Leiter des 3D-NAND-Designs eines großen Speicherchipherstellers. Zu seinen wichtigsten Errungenschaften gehört die erste inländische rekonfigurierbare Hochleistungsspeicher- und Computerprozessorproduktarchitektur (hat interne Prototypentests abgeschlossen). großer Internethersteller), der erste medizinische domänenspezifische KI-Prozessor (bereits implementiert), der erste RISC-V/x86/ARM-Plattform-kompatible KI-Beschleunigungscompiler (bereits implementiert in Zusammenarbeit mit Alibaba Pingtouge/Xinlai), Chinas erster 3D-NAND-Chip Architektur und Design Das Team wurde gegründet (Benchmark mit Samsung) und der erste eingebettete Flash-Speicher-Compiler in China (Benchmark mit TSMC und wurde auf Plattformebene angewendet).

Am letzten Tag im September 2022, Teslas Tag der künstlichen Intelligenz, debütierte Teslas „Optimus Prime“-Roboter offiziell. Laut Tesla-Ingenieuren ist der Artificial Intelligence Day 2022 das erste Mal, dass Tesla-Roboter ohne externe Unterstützung „freigegeben“ werden. „Er ging würdevoll und begrüßte das Publikum in eine allgemeine Richtung.“ Bis auf die leichte Trägheit der Bewegungen ist alles andere sehr natürlich.

1 Die Kraft des Tesla-Roboters liegt in seinem „inneren Kern“?

Tesla zeigt ein Video von Robotern, die im Büro „arbeiten“. Ein Roboter namens Optimus Prime trug Gegenstände, bewässerte Pflanzen und arbeitete eine Zeit lang sogar autonom in einer Fabrik. „Unser Ziel ist es, so schnell wie möglich nützliche humanoide Roboter zu bauen“, sagte Tesla und fügte hinzu, dass ihr Ziel darin bestehe, die Roboter für weniger als 20.000 US-Dollar oder billiger als die Elektroautos von Tesla herzustellen.

Der Grund, warum Tesla-Roboter so leistungsstark sind, liegt nicht nur an Teslas eigener Anhäufung von KI-Technologie, sondern vor allem auch an Teslas starken selbst entwickelten KI-Chips. Dieser KI-Chip ist keine herkömmliche CPU, geschweige denn eine GPU. Er eignet sich besser für komplexe KI-Berechnungen.

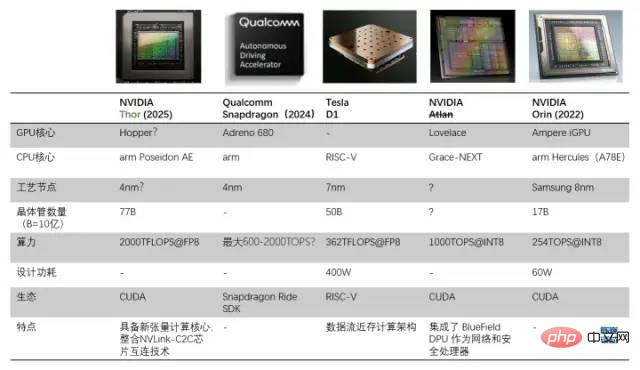

Vergleich zwischen D1-Prozessor und anderen Prozessoren für autonomes Fahren/Roboter

1.1 Basierend auf Datenfluss-Near-Memory-Architektur zur Erstellung eines Allzweck-KI-Chips, der GPU übertrifft

Tesla baut seinen eigenen Der Grund für den Chip liegt darin, dass die GPU nicht speziell für Deep-Learning-Training ausgelegt ist, wodurch die GPU bei Rechenaufgaben relativ ineffizient ist. Das Ziel von Tesla und Dojo (Dojo ist sowohl der Name des Trainingsmoduls als auch der Name der Kernel-Architektur) besteht darin, „die beste KI-Trainingsleistung zu erzielen. Größere und komplexere neuronale Netzwerkmodelle zu ermöglichen, um eine hohe Energieeffizienz und Kosten zu erreichen.“ Effektivität. „Computing.“ Teslas Standard besteht darin, einen Computer zu bauen, der sich besser mit künstlicher Intelligenz auskennt als jeder andere Computer, sodass in Zukunft keine GPU mehr benötigt wird.

Ein wichtiger Punkt beim Bau von Supercomputern ist die Skalierung der Rechenleistung unter Beibehaltung einer hohen Bandbreite (schwierig) und einer geringen Latenz (sehr schwierig). Die von Tesla bereitgestellte Lösung ist eine verteilte 2D-Architektur (planar), die aus leistungsstarken Chips und einer einzigartigen Gitterstruktur besteht, oder eine Datenfluss-Near-Memory-Computing-Architektur.

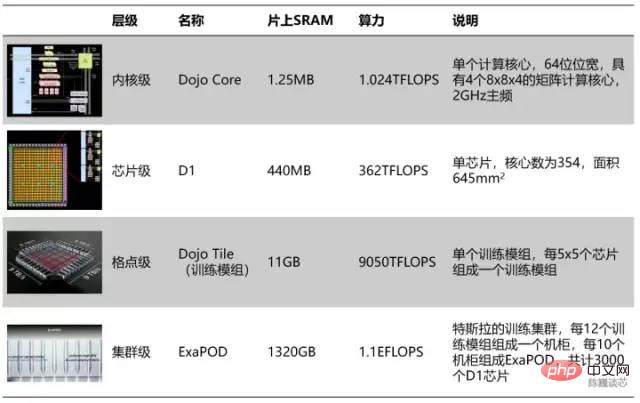

Hierarchische Aufteilung der Tesla-Recheneinheiten

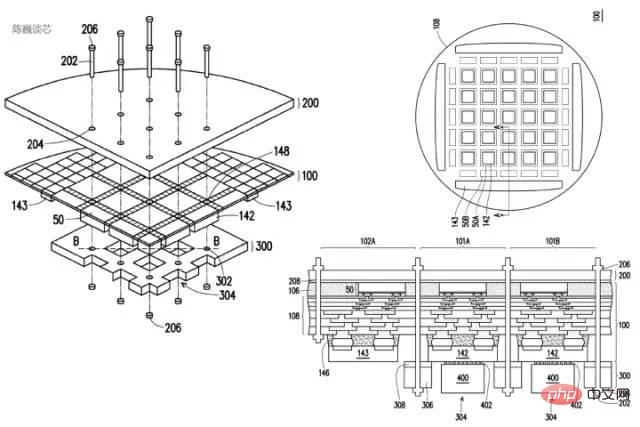

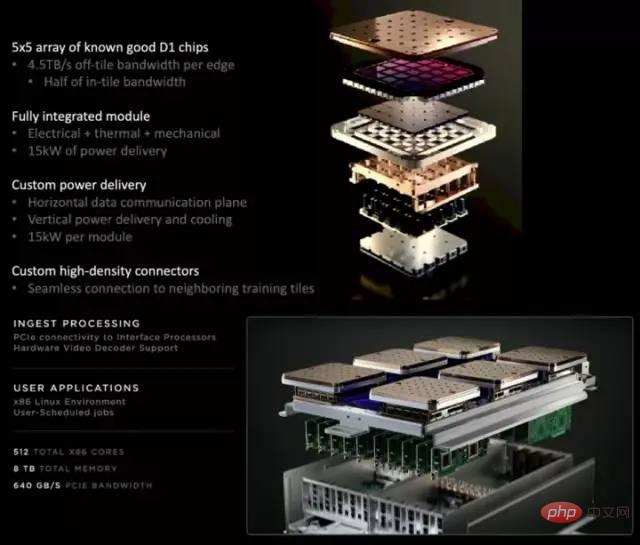

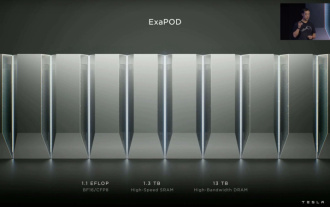

Gemäß der hierarchischen Aufteilung bilden alle 354 Dojo-Kerne einen D1-Chip und alle 25 Chips ein Trainingsmodul. Die letzten 120 Trainingsmodule bilden eine Reihe von ExaPOD-Rechnerclustern mit insgesamt 3.000 D1-Chips.

Ein Tesla Dojo-Chip-Trainingsmodul kann die Leistung von 6 Gruppen von GPU-Servern erreichen, aber die Kosten sind geringer als bei einer einzelnen Gruppe von GPU-Servern. Die Rechenleistung eines einzelnen Dojo-Servers erreichte sogar 54PFLOPS. Nur 4 Dojo-Schränke können 72 GPU-Racks mit 4.000 GPUs ersetzen. Dojo reduziert den KI-Rechenaufwand (Schulung), der normalerweise Monate dauert, auf eine Woche. Diese Art von „großer Rechenleistung kann Wunder bewirken“ steht im Einklang mit Teslas autonomem Fahrstil. Offensichtlich wird der Chip auch den Fortschritt der KI-Technologie von Tesla erheblich beschleunigen.

Natürlich hat dieses Chipmodul noch nicht das „perfekte“ Niveau erreicht. Obwohl es die Idee des Datenfluss-Near-Memory-Computing übernimmt, übertrifft es das Verhältnis von Rechenleistung und Energieeffizienz nicht GPU. Ein einzelner Server verbraucht enorm viel Strom, der Strom kann 2000 A erreichen, und erfordert eine speziell angepasste Stromversorgung. Der Tesla D1-Chip ist bereits die strukturelle Grenze der Near-Memory-Computing-Architektur. Wenn Tesla die Architektur „In-Memory Computing“ oder „In-Memory Logic“ einführt, werden möglicherweise die Chipleistung oder das Energieeffizienzverhältnis erheblich verbessert.

Der Tesla Dojo-Chipserver besteht aus 12 Dojo-Schulungsmodulen (2 Schichten, 6 pro Schicht) Way-Matrix-Recheneinheit (8x8) und 1,25 MB lokaler SRAM. Die Größe des Dojo-Kerns ist jedoch nicht groß. Im Vergleich dazu belegt der A64FX von Fujitsu mehr als doppelt so viel Fläche auf demselben Prozessknoten.

Flächenreduzierung: Tesla integriert eine große Anzahl von Rechenkernen in den Chip, um den Durchsatz der KI zu maximieren Beim Computing ist es notwendig, die Fläche eines einzelnen Kerns so klein wie möglich zu machen und gleichzeitig die Rechenleistung sicherzustellen und den Widerspruch zwischen der Stapelung der Rechenleistung und der Verzögerung in Supercomputing-Systemen besser zu kompensieren.

Caching und Latenzoptimierung: Um die Effizienz der Flächenberechnung zu maximieren, läuft der Dojo-Kernel mit relativ konservativen 2 GHz (konservative Taktschaltungen nehmen tendenziell weniger Fläche ein) und verwendet nur einen einfachen Zweigprädiktor und kleines Befehls-Caching. in einer so schlanken Architektur, die nur die notwendigen Komponenten enthält. Der verbleibende Bereich wird weitestgehend den Vektorberechnungs- und Matrizenberechnungseinheiten überlassen. Wenn das Kernelprogramm über einen großen Code-Footprint oder viele Zweige verfügt, kann diese Strategie natürlich zu Leistungseinbußen führen.

Funktionsoptimierung: Reduzieren Sie den Stromverbrauch und den Flächenverbrauch weiter, indem Sie Prozessorfunktionen eliminieren, die für die Ausführung interner Berechnungen nicht erforderlich sind. Dojo Core führt kein datenseitiges Caching durch, unterstützt keinen virtuellen Speicher und unterstützt keine präzisen Ausnahmen.

- Für Tesla und Musk hat Dojo nicht nur die Form und Anordnung eines Dojos, sondern seine Designphilosophie ist auch eng mit dem Geist des Dojos verbunden und verkörpert vollständig die Ästhetik des Prozessordesigns „Weniger ist mehr“.

- 2 Ist der D1-Kern eine RISC-V-Architektur? Werfen wir zunächst einen Blick auf die Struktur und Eigenschaften jedes Dojos.

- Jeder Dojo-Kern ist ein Prozessor mit Vektorberechnungs-/Matrixberechnungsfunktionen und verfügt über vollständige Befehlsabruf-, Dekodierungs- und Ausführungskomponenten. Der Dojo-Kern hat einen CPU-ähnlichen Stil, der sich offenbar besser an verschiedene Algorithmen und Verzweigungscodes anpassen lässt als die GPU. Der Befehlssatz von D1 ähnelt dem von RISC-V. Der Prozessor läuft mit 2 GHz und verfügt über vier Sätze von 8x8-Matrixmultiplikationsberechnungseinheiten. Es verfügt außerdem über eine Reihe benutzerdefinierter Vektoranweisungen, die sich auf die Beschleunigung von KI-Berechnungen konzentrieren.

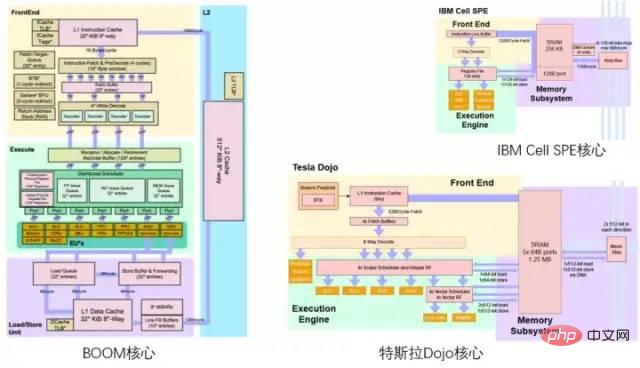

Wer sich mit dem RISC-V-Bereich auskennt, kann wahrscheinlich erkennen, dass das Farbschema von Teslas Dojo-Architekturdiagramm eine Hommage an Berkeleys BOOM-Prozessorarchitekturdiagramm zu sein scheint, mit Gelb oben, Grün unten und Lila unten der Boden. Vergleich zwischen Tesla Dojo Core und Berkeley Boom/IBM Cell Core

2.1 D1 -Kern -Gesamtarchitektur

d1 -Kernstruktur (der blaue Teil wird hinzugefügt/modifiziert) Details )

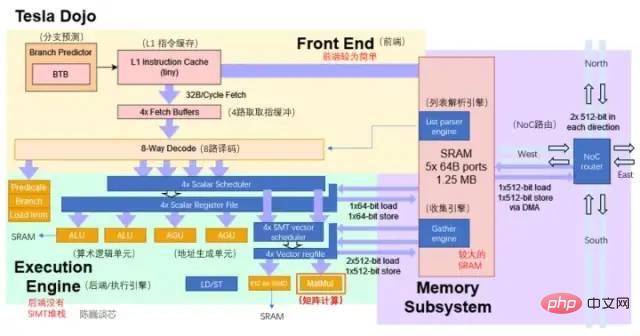

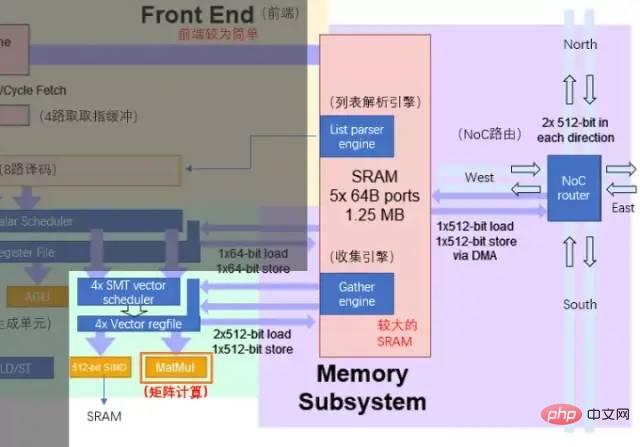

Dem aktuellen Architekturdiagramm nach zu urteilen, besteht der Dojo-Kern aus 4 Teilen: Front-End, Ausführungseinheit, SRAM und NoC-Routing. Er verfügt über weniger Steuerungskomponenten als CPU und GPU. Er verfügt über eine CPU-ähnliche AGU und eine GPU-ähnliche Idee. Die Matrix-Recheneinheit des Tensor-Kerns.

Hauptparameter des Dojo-Kerns

- Zweigvorhersage: Im Vergleich zu SIMT-Architekturen wie GPUs verfügt der Dojo-Kern nicht über einen SIMT-Stack-Kern zur Zuweisung von Multithread-Zweigaufgaben. Der Dojo-Kern verfügt jedoch über BTB (Branch Target Buffer), sodass D1 die Leistung durch einfache Verzweigungsvorhersage verbessern kann.

BTB speichert die Adresse des erfolgreichen Verzweigungsbefehls und seine Verzweigungszieladresse in einem Puffer. Der Puffer wird durch die Adresse des Verzweigungsbefehls identifiziert. Die Leistungseinbußen von Verzweigungen in Pipeline-Prozessoren können reduziert werden, indem der Pfad der Verzweigung vorhergesagt und die von der Verzweigung verwendeten Informationen zwischengespeichert werden. - Befehlscache: Der kleinere L1-Befehlscache ist direkt mit dem SRAM im Kern verbunden, um Rechenanweisungen zu erhalten.

- Anweisungsabruf: Jeder Dojo-Kernel verfügt über ein 32-B-Befehlsabruffenster, das bis zu 8 Anweisungen aufnehmen kann.

- Dekodierung: Ein 8-Wege-Decoder kann zwei Threads pro Zyklus verarbeiten. Die Dekodierungsphase ruft Anweisungen aus dem Abrufpuffer ab, dekodiert sie und weist die erforderlichen Ausführungsressourcen entsprechend den Anforderungen jeder Anweisung zu.

- Thread-Scheduling: Nach der breiteren 8-Wege-Dekodierung gibt es den Vektor-Scheduler (Scheduler) und die Registerdatei (Register File). Es scheint, dass es hier keine Maskenbeurteilung für die Zweigaggregation gibt und die tatsächliche Effizienz der Zweigausführung möglicherweise etwas geringer ist als die der GPU. Hoffentlich hat Tesla einen leistungsstarken Compiler.

- Ausführungseinheit: Mit 2-Wege-ALU und 2-Wege-AGU sowie 512-Bit-SIMD- und Matrixberechnungseinheiten für Vektor-/Matrixberechnungen (durchführen von 512-Bit-Vektorberechnungen bzw. 4-Wege-8x8-Matrixmultiplikation) . Die Matrix-Recheneinheit ist die Hauptrechenleistung des D1-Chips. (Im nächsten Abschnitt ausführlich vorgestellt)

- ALU und AGU sind hauptsächlich für eine kleine Menge logischer Berechnungen außer Matrixberechnungen verantwortlich. Die AGU ist die Adressgenerierungseinheit, die hauptsächlich dazu dient, die für den Betrieb des SRAM erforderlichen Adressen zu generieren und auf die Adressen anderer Kerne zuzugreifen. Indem die Adressberechnung parallel zum Rest der CPU ausgeführt wird.

Wenn eine gewöhnliche CPU verschiedene Vorgänge ausführt, muss sie die Speicheradresse berechnen, die zum Abrufen von Daten aus dem Speicher (oder SRAM) erforderlich ist. Beispielsweise muss der Speicherort eines Array-Elements berechnet werden, bevor der CPU-Kern die Daten vom tatsächlichen Speicherort abrufen kann. Diese Berechnungen zur Adressgenerierung umfassen verschiedene ganzzahlige arithmetische Operationen wie Addition, Subtraktion, Modulo-Arithmetik oder Bitverschiebung. Die Berechnung der Speicheradresse kann mehrere allgemeine Maschinenanweisungen kompilieren oder direkt über die AGU-Hardwareschaltung wie Tesla Dojo ausgeführt werden. Auf diese Weise können verschiedene Berechnungen zur Adressgenerierung von der ALU ausgelagert werden, wodurch die Anzahl der für die Durchführung von KI-Berechnungen erforderlichen CPU-Zyklen reduziert und dadurch die Rechenleistung verbessert wird. - SIMD ist hauptsächlich für die Berechnung spezieller Funktionen wie Aktivierung und Akkumulation von Daten verantwortlich.

- Die Matrixberechnungseinheit ist die Hauptrechenkomponente von Dojo. Sie ist für zweidimensionale Matrixberechnungen verantwortlich und führt dann Faltung, Transformator und andere Berechnungen durch.

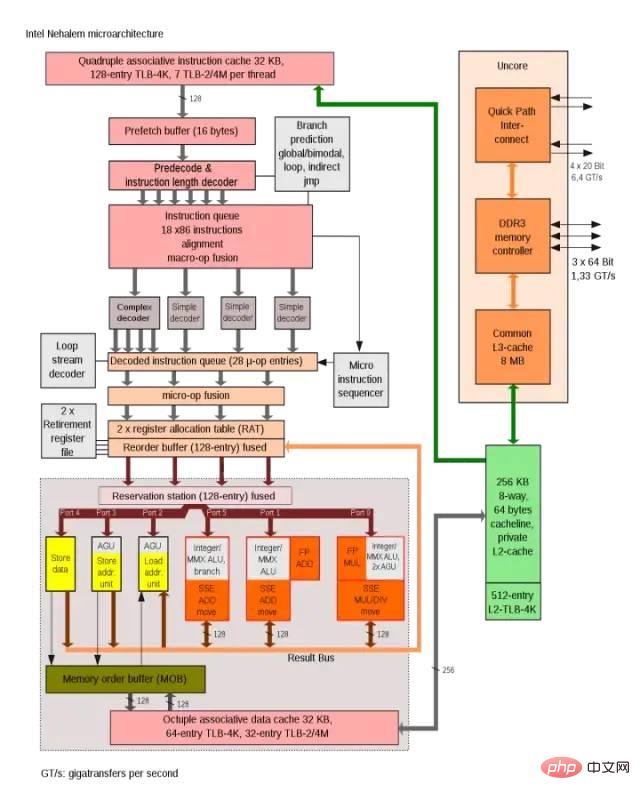

Intel Nehalem-Architektur verwendet AGU, um die Effizienz des Adresszugriffs in einem Zyklus zu verbessern

Die Verbindungsmethode des Dojo-Kerns ähnelt eher der SPE-Kernverbindungsmethode im Cell-Prozessor von IBM. Zu den wichtigsten Gemeinsamkeiten gehören:

- Weder auf D1 oder SPE ausgeführter Code hat direkten Zugriff auf den Systemspeicher, Anwendungen arbeiten hauptsächlich im lokalen SRAM.

- Wenn Daten aus dem Hauptspeicher (DDR oder HBM) erforderlich sind, müssen DMA-Operationen durchgeführt werden zum Einlesen verwendet werden. Weder D1 noch Cells SPE unterstützen virtuellen Speicher.

- Im Folgenden wird die Speicherung von Berechnungs- und Matrixmultiplikationsmodulen und -kernen vorgestellt.

2.2 Rechenkern-Matrix-Recheneinheit und On-Chip-Speicher

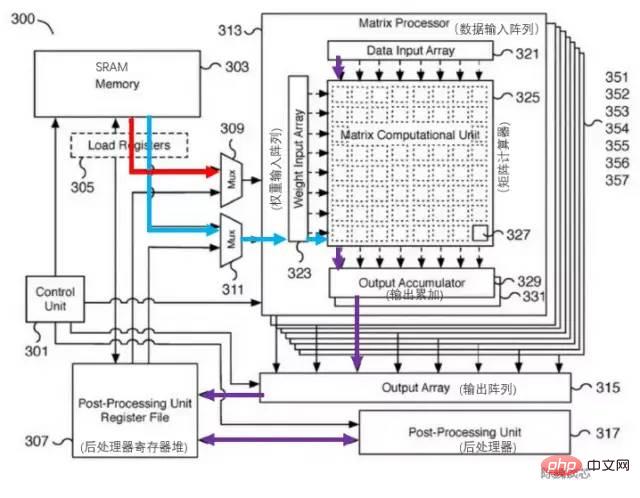

Der Kern der Rechenleistungssteigerung der Dojo-Architektur ist die Matrix-Recheneinheit. Die Dateninteraktion zwischen der Matrix-Recheneinheit und dem Kern-SRAM stellt den Hauptstromverbrauch für die Kerndatenübertragung dar.Das entsprechende Patent der Tesla-Matrix-Recheneinheit ist unten dargestellt. Die Schlüsselkomponente dieses Moduls ist eine 8x8-Matrix-Matrix-Multiplikationseinheit (in der Abbildung Matrixrechner genannt). Die Eingabe ist das Dateneingabearray und das Gewichtseingabearray. Nach der Berechnung der Matrixmultiplikation wird die Ausgabe direkt akkumuliert. Jeder Dojo-Kern enthält 4-Wege-8x8-Matrixmultiplikationseinheiten.

Tesla Matrix Computing Unit Patent

Tesla Matrix Computing Unit Patent

Da es im Architekturdiagramm nur einen L1-Cache und SRAM gibt, ist es eine gewagte Vermutung, dass Tesla die RISC-V-Cache-Struktur optimiert hat, um Cache-Bereich zu sparen und die Latenz zu reduzieren. Der 1,25-MB-SRAM-Block pro Kern kann 2x512-Bit-Lesen (entsprechend der Gewichtung und Daten von AI-Berechnungen) und 512-Bit-Schreibbandbreite für SIMD- und Matrix-Recheneinheiten sowie 64-Bit-Lese- und Schreibfunktionen für die Ganzzahl bereitstellen Registerdatei. Der Hauptdatenfluss der Berechnung erfolgt vom SRAM zum SIMD und zu den Matrixmultiplikationseinheiten.

Der Hauptverarbeitungsablauf der Matrixberechnungseinheit ist:

Laden von Gewichten vom SRAM in das Gewichtungseingabearray (Gewichtseingabearray) über einen Multiplexer (Mux) und Laden von Daten vom SRAM in das Dateneingabearray (Dateneingabe). Array).

Die Eingabedaten und Gewichte werden im Matrixrechner (Matrixberechnungseinheit) multipliziert (inneres Produkt oder äußeres Produkt?).

Die Ergebnisse der Multiplikationsberechnung werden zur Akkumulation an den Ausgabeakkumulator (Ausgabeakkumulator) ausgegeben. Bei der Berechnung hier können Matrixberechnungen über 8x8 durch Matrixteilung und -spleißen durchgeführt werden.

Die akkumulierte Ausgabe wird zur Zwischenspeicherung an die Registerdatei des Postprozessors übergeben und anschließend nachverarbeitet (Vorgänge wie Aktivierung, Pooling, Auffüllen usw. können ausgeführt werden).

Der gesamte Berechnungsprozess wird ohne CPU-Eingriff direkt von der Steuereinheit (Steuereinheit) gesteuert.

Dateninteraktion zwischen Ausführungseinheit und SRAM/NoC

Der SRAM im Dojo-Kern verfügt über eine sehr große Lese- und Schreibbandbreite und kann mit 400 GB/Sek. und 270 GB/Sek. laden Schreibgeschwindigkeit. Der Dojo-Kernbefehlssatz verfügt über dedizierte Netzwerkübertragungsanweisungen, die über den NoC geleitet werden und Daten direkt in den SRAM-Speicher anderer Kerne im D1-Chip oder sogar im Dojo-Trainingsmodul oder aus diesem heraus verschieben können.

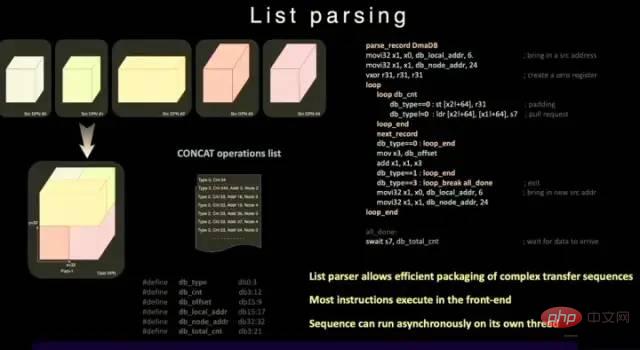

Anders als gewöhnliches SRAM enthält Dojos SRAM eine Listen-Parser-Engine und eine Gather-Engine. Die Listenparsing-Funktion ist eine der Hauptfunktionen des D1-Chips. Die Listenparsing-Engine kann komplexe Übertragungssequenzen verschiedener Datentypen packen, um die Übertragungseffizienz zu verbessern.

Listenanalysefunktion

Um die Betriebsverzögerung, den Bereich und die Komplexität weiter zu reduzieren, unterstützt D1 keinen virtuellen Speicher. In einem normalen Prozessor greift die vom Programm verwendete Speicheradresse nicht direkt auf die physische Speicheradresse zu, sondern wird von der CPU mithilfe der vom Betriebssystem festgelegten Paging-Struktur in eine physische Adresse umgewandelt.

Im D1-Kern ermöglicht die 4-Wege-SMT-Funktion explizite Parallelität bei Berechnungen, wodurch die AGU- und Adressberechnungsmethoden vereinfacht werden, damit Tesla mit ausreichend geringer Latenz auf SRAM zugreifen kann. Sein Vorteil besteht darin, dass ein Zwischenspeichern von L1-Daten vermieden werden kann Latenz.

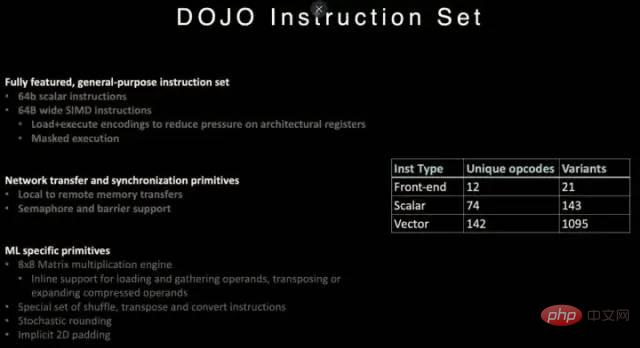

2.3 Dojo-Befehlssatz

D1-Prozessor-Befehlssatz

D1 bezieht sich auf die Anweisungen der RISC-V-Architektur und passt einige Anweisungen an, insbesondere solche im Zusammenhang mit Vektorberechnungen.

Der D1-Befehlssatz unterstützt 64-Bit-Skalaranweisungen und 64-Byte-SIMD-Anweisungen, Netzwerkübertragung mit Synchronisierungsprimitiven und speziellen Primitiven im Zusammenhang mit maschinellem Lernen/Deep Learning (z. B. 8x8-Matrixberechnungen).

In Bezug auf Netzwerkdatenübertragungs- und Synchronisationsprimitive unterstützt es Befehlsprimitive (Primitive) zum Übertragen von Daten vom lokalen Speicher (SRAM) zum Remotespeicher sowie Semaphore (Semaphore) und Barrierebeschränkungen (Barrierebeschränkungen). Dadurch kann D1 Multithreading unterstützen und seine Speicherbetriebsanweisungen können auf mehreren D1-Kernen ausgeführt werden.

Für maschinelles Lernen und Deep Learning hat Tesla Anweisungen definiert, darunter mathematische Operationen wie Mischen, Transponieren und Konvertieren sowie stochastische Rundungs- und Auffüllanweisungen.

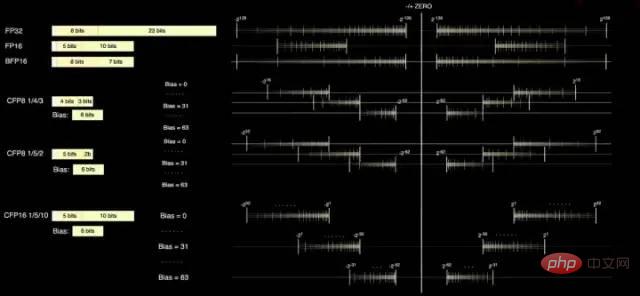

2.4 Datenformat

Der D1-Kern verfügt über zwei Standardberechnungsformate, FP32 und FP16, sowie über das BFP16-Format, das besser für Inferenz geeignet ist. Um die Leistungsverbesserungen des Mixed-Precision-Computings zu erreichen, verwendet der D1 auch das 8-Bit-CFP8-Format für geringere Präzision und höheren Durchsatz.

Der Vorteil der Verwendung von CFP8 besteht darin, dass mehr Multiplikatorraum eingespart werden kann, um nahezu die gleiche Rechenleistung zu erzielen, was sehr hilfreich ist, um die Rechenleistungsdichte von D1 zu erhöhen.

Der Dojo-Compiler kann um die Mantissengenauigkeit gleiten, um einen größeren Bereich und eine größere Genauigkeit abzudecken. Bis zu 16 verschiedene Vektorformate können gleichzeitig verwendet werden, was Ihnen die Flexibilität gibt, die Rechenleistung zu erhöhen.

D1-Prozessordatenformat

Nach Angaben von Tesla kann CFP8 für Berechnungen innerhalb der Matrixmultiplikationseinheit verwendet werden (gespeichert im CFP16-Format).

3 Kann der Prozessor der Dojo-Architektur die GPU übertreffen?

Der D1-Prozessor wird von TSMC hergestellt und verwendet einen 7-Nanometer-Fertigungsprozess. Er verfügt über 50 Milliarden Transistoren und eine Chipfläche von 645 mm², was kleiner ist als NVIDIAs A100 (826 mm²) und AMD Arcturus (750 mm²). .

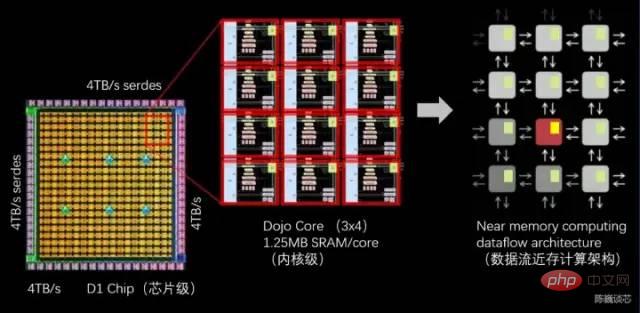

3.1 Dojo-Datenfluss-Near-Memory-Computing-Architektur

D1-Prozessorstruktur

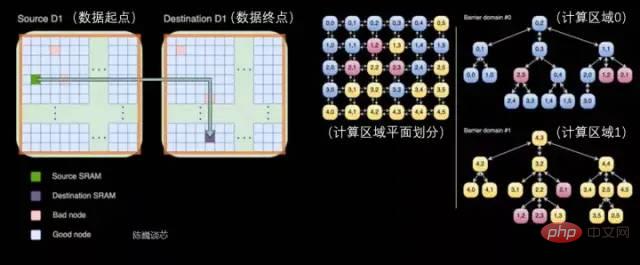

Jeder D1-Prozessor besteht aus 18 x 20 Dojo-Kernspleißen. In jedem D1-Prozessor stehen 354 Dojo-Kerne zur Verfügung. (Der Grund, warum nur 354 der 360 Kerne verwendet werden, liegt in Überlegungen zur Ausbeute und zur Kernstabilität pro Prozessor.) Es wird von TSMC in einem 7-nm-Herstellungsprozess mit 50 Milliarden Transistoren und einer Chipfläche von 645 mm² hergestellt.

Jeder Dojo-Kern verfügt über einen 1,25 MB großen SRAM als Hauptgewicht und Datenspeicher. Verschiedene Dojo-Kerne sind über On-Chip-Netzwerkrouting (NoC-Routing) verbunden, und verschiedene Dojo-Kerne führen die Datensynchronisierung über komplexe NoC-Netzwerke durch, anstatt Datencaches gemeinsam zu nutzen. Der NoC kann 8 Pakete in 4 Richtungen (Südosten, Nordwesten) über Knotengrenzen hinweg mit 64 B/pro Taktzyklus in jede Richtung verarbeiten, d. h. ein Paket rein und ein Paket raus in das Netz in alle vier Richtungen für jeden angrenzenden Dojo-Kern. Der NoC-Router kann auch einmal pro Zyklus einen bidirektionalen 64-B-Lese- und Schreibvorgang im SRAM im Kern durchführen.

Prozessorübergreifende Übertragung und Aufgabenteilung innerhalb des D1-Prozessors

Jeder Dojo-Kern ist eine relativ vollständige CPU-ähnliche Klasse mit Matrix-Rechenfunktionen (da jeder Kern über eine separate Matrix-Recheneinheit verfügt). , und das Frontend ist relativ klein, daher wird es hier als CPU-ähnlich bezeichnet. Seine Datenflussarchitektur ähnelt in gewisser Weise der zweidimensionalen Datenflussgitterstruktur von SambaNova.

Der D1-Chip läuft mit 2 GHz und verfügt über riesige 440 MB SRAM. Tesla konzentriert sein Design auf verteiltes SRAM im Rechengitter und reduziert die Häufigkeit des Speicherzugriffs durch eine große Anzahl schnellerer und engerer On-Chip-Speicher sowie die Übertragung zwischen On-Chip-Speichern, wodurch die Leistung des gesamten Systems verbessert wird Es verfügt über offensichtliche Merkmale der integrierten Datenflussspeicher- und Computing-Architektur (Data Flow Near-Memory Computing).

Jeder D1-Chip verfügt über 576 bidirektionale SerDes-Kanäle, die um ihn herum verteilt sind, und kann mit einer einseitigen Bandbreite von 4 TB/s mit anderen D1-Chips verbunden werden. Hauptparameter des D1-Prozessorchips dimensionale Mesh-Struktur. Der On-Chip-Cross-Core-SRAM erreicht erstaunliche 11 GB, und natürlich erreicht auch der Stromverbrauch erstaunliche 15 kW. Das Energieeffizienzverhältnis beträgt 0,6TFLOPS/W@BF16/CFP8. (Ich hoffe, ich habe es falsch berechnet, sonst ist dieses Energieeffizienzverhältnis tatsächlich nicht ideal). Externer 32 GB gemeinsam genutzter HBM-Speicher. (HBM2e oder HBM3)

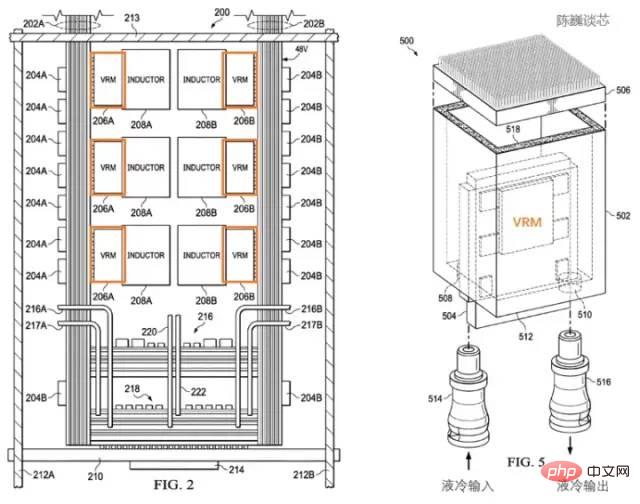

Patentierte Wärmeableitungsstruktur des Tesla D1-Prozessors

Tesla verwendet ein spezielles Leistungsregulierungsmodul (VRM) und eine Wärmeableitungsstruktur, um den Stromverbrauch zu verwalten. Hier gibt es zwei Hauptziele des Stromverbrauchsmanagements:

Unnötigen Leistungsverlust reduzieren und das Energieeffizienzverhältnis verbessern.

Reduzieren Sie Prozessormodulausfälle aufgrund thermischer Verformung.

Laut Teslas Patent können wir sehen, dass das Leistungsregulierungsmodul senkrecht zum Chip selbst steht, was die von der Prozessorebene eingenommene Fläche erheblich reduziert und die Temperatur des Prozessors durch Flüssigkeitskühlung schnell ausgleichen kann.

Patentierte Wärmeableitung und Verpackungsstruktur des Tesla D1-Prozessors

Das Schulungsmodul verwendet InFO_SoW (Silicon on Wafer)-Verpackung, um die Verbindungsdichte zwischen Chips zu erhöhen. Zusätzlich zur INFO_SoW-Technologie von TSMC nutzt dieses Paket auch Teslas eigene mechanische Verpackungsstruktur, um den Ausfall des Prozessormoduls zu reduzieren.

40 I/O-Chips am äußeren Rand jedes Trainingsmoduls erreichen eine Gesamtbandbreite von 36 TB/s oder eine Spannenbandbreite von 10 TB/s. Jede Ebene der Schulungsmodule ist mit einem Ultrahochgeschwindigkeits-Speichersystem verbunden: 640 GB laufender Speicher können mehr als 18 TB/s Bandbreite sowie mehr als 1 TB/s Netzwerk-Switching-Bandbreite bereitstellen.

Die Datenübertragungsrichtung verläuft parallel zur Chipebene und die Stromversorgungs- und Flüssigkeitskühlungsrichtungen verlaufen senkrecht zur Chipebene. Dies ist ein sehr schönes strukturelles Design, und verschiedene Trainingsmodule können miteinander verbunden werden. Durch die dreidimensionale Struktur wird die Stromversorgungsfläche des Chipmoduls eingespart und der Abstand zwischen den Rechenchips so weit wie möglich reduziert.

Ein Dojo POD-Schrank besteht aus zwei Schichten von Computerfächern und Aufbewahrungssystemen. Jede Palettenebene verfügt über 6 D1-Schulungsmodule. Ein aus 12 Schulungsmodulen auf zwei Etagen bestehender Schrank kann 108PFLOPS Deep-Learning-Rechenleistung bereitstellen.

Dojo-Modul und Dojo-POD-Schrank

3.3 Energiemanagement und Wärmeableitungskontrolle

Die Wärmeableitung von Supercomputing-Plattformen war schon immer eine wichtige Dimension zur Messung des Niveaus von Supercomputing-Systemen.

Thermische Designleistung des D1-Chips

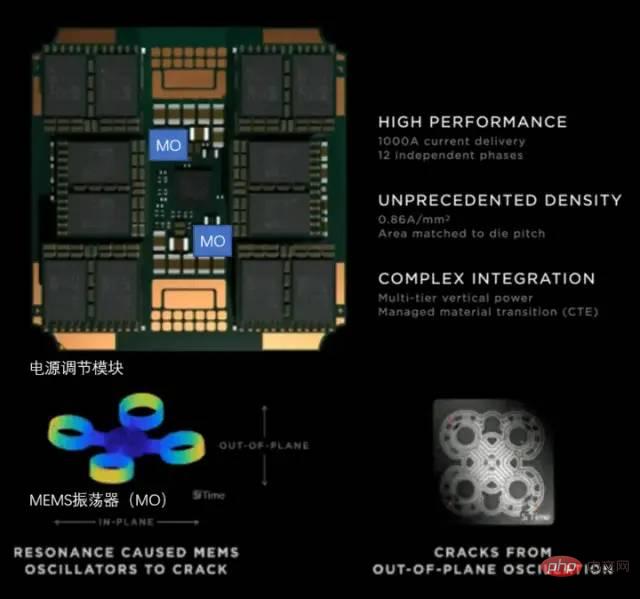

Tesla verwendet ein vollständig selbst entwickeltes VRM (Voltage Regulation Module) auf dem Dojo POD. Ein einzelnes VRM kann eine Spannung von 52 V und einen enormen Strom von über 1000 A liefern, das aktuelle Ziel liegt bei 0,86 A pro Quadratmillimeter, mit insgesamt 12 unabhängigen Stromversorgungsphasen.

Teslas Leistungskonditionierungsmodul

Bei der Wärmeableitung von Chips mit hoher Dichte liegt der Schwerpunkt auf der Steuerung des Wärmeausdehnungskoeffizienten (CTE). Die Chipdichte des Dojo-Systems ist extrem hoch. Wenn der CTE leicht außer Kontrolle gerät, kann es zu strukturellen Verformungen/Versagen kommen, was zu Verbindungsfehlern führt.

Teslas selbst entwickeltes VRM hat in den letzten 2 Jahren 14 Versionen durchlaufen. Es verwendet einen MEMS-Oszillator (MO), um die thermische Verformung des Leistungsregulierungsmoduls zu erfassen, und erfüllt schließlich vollständig die internen Anforderungen für CTE-Indikatoren. Diese Methode zur aktiven Anpassung der Stromversorgung durch MEMS-Technologie ähnelt der aktiven Anpassungsmethode zur Steuerung der Vibration des Raketenkörpers.

3.4 Kompilierungsökologie des Dojo-Architekturprozessors

D1-Prozessor-Softwarestapel

Für KI-Chips wie D1 ist die Kompilierungsökologie nicht weniger wichtig als der Chip selbst.

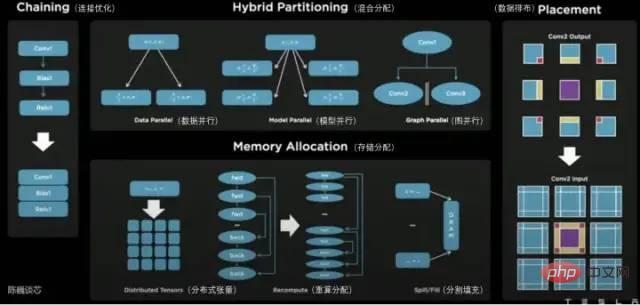

Auf der D1-Prozessorebene ist D1 in Matrix-Recheneinheiten unterteilt. Die Kompilierungstoolkette ist für die Aufteilung von Aufgaben und die Konfiguration der Datenspeicherung verantwortlich und führt auf verschiedene Weise feinkörniges paralleles Rechnen durch und reduziert die Speichernutzung.

Zu den vom Dojo-Compiler unterstützten parallelen Methoden gehören Datenparallelität, Modellparallelität und Graphparallelität. Zu den unterstützten Speicherzuweisungsmethoden gehören verteilte Tensoren, neu berechnete Zuweisung und Split-Fill.

Der Compiler selbst kann den dynamischen Kontrollfluss verarbeiten, der häufig in verschiedenen CPUs verwendet wird, einschließlich Schleifen und Diagrammoptimierungsalgorithmen. Mit dem Dojo-Compiler können Benutzer große verteilte Dojo-Systeme als Beschleuniger für das Gesamtdesign und die Schulung nutzen.

Die oberste Schicht des gesamten Software-Ökosystems basiert auf PyTorch, die untere Schicht basiert auf dem Dojo-Treiber und in der Mitte werden der Dojo-Compiler und LLVM verwendet bilden die Kompilierungsschicht. Nachdem hier LLVM hinzugefügt wurde, kann Tesla die verschiedenen Kompilierungsökosysteme, die bereits auf LLVM vorhanden sind, für die Kompilierungsoptimierung besser nutzen.

TeslaDojo Compiler

#🎜 🎜# 4 FazitDurch den Tesla AI Day haben wir den wahren Körper des Tesla-Roboters gesehen und mehr über seinen leistungsstarken „inneren Kern“ erfahren.

Teslas Dojo-Kern unterscheidet sich von früheren CPU- und GPU-Architekturfunktionen. Man kann sagen, dass es sich um eine optimierte GPU handelt, die die Eigenschaften der CPU vereint besser in der Kompilierung. Es wird auch große Unterschiede zwischen CPU und GPU geben. Um die Rechendichte zu erhöhen, hat Tesla äußerst schlanke Optimierungen vorgenommen und einen aktiv angepassten Energieverwaltungsmechanismus bereitgestellt.

Die Architektur des Tesla Dojo wird nicht nur als Dojo bezeichnet, sondern ihr Design basiert tatsächlich auf Einfachheit als Weg und weniger als mehr. Wird diese Architektur nach CPU und GPU eine weitere typische Form der Computerchip-Architektur werden? Warten wir ab.

Das obige ist der detaillierte Inhalt vonKann der Tesla-Supercomputing-Chip GPGPU übertreffen?. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!

Heiße KI -Werkzeuge

Undresser.AI Undress

KI-gestützte App zum Erstellen realistischer Aktfotos

AI Clothes Remover

Online-KI-Tool zum Entfernen von Kleidung aus Fotos.

Undress AI Tool

Ausziehbilder kostenlos

Clothoff.io

KI-Kleiderentferner

AI Hentai Generator

Erstellen Sie kostenlos Ai Hentai.

Heißer Artikel

Heiße Werkzeuge

Notepad++7.3.1

Einfach zu bedienender und kostenloser Code-Editor

SublimeText3 chinesische Version

Chinesische Version, sehr einfach zu bedienen

Senden Sie Studio 13.0.1

Leistungsstarke integrierte PHP-Entwicklungsumgebung

Dreamweaver CS6

Visuelle Webentwicklungstools

SublimeText3 Mac-Version

Codebearbeitungssoftware auf Gottesniveau (SublimeText3)

Heiße Themen

1381

1381

52

52

Tesla ergreift endlich Maßnahmen! Werden bald selbstfahrende Taxis vorgestellt? !

Apr 08, 2024 pm 05:49 PM

Tesla ergreift endlich Maßnahmen! Werden bald selbstfahrende Taxis vorgestellt? !

Apr 08, 2024 pm 05:49 PM

Laut Nachrichten vom 8. April gab Tesla-CEO Elon Musk kürzlich bekannt, dass Tesla sich der vollständigen Entwicklung selbstfahrender Autotechnologie verschrieben hat. Das mit Spannung erwartete unbemannte selbstfahrende Taxi Robotaxi wird am 8. August auf den Markt kommen. Offizielles Debüt. Der Datenredakteur erfuhr, dass Musks Aussage auf Zuvor berichtete Reuters, dass Teslas Plan, Autos anzutreiben, sich auf die Produktion von Robotaxi konzentrieren würde. Musk wies dies jedoch zurück und warf Reuters vor, Pläne zur Entwicklung von Billigautos abgesagt und erneut Falschmeldungen veröffentlicht zu haben, während er gleichzeitig klarstellte, dass es sich um Billigautos wie Model 2 und Robotax handelte

Tesla Dojo-Supercomputing-Debüt, Musk: Die Rechenleistung der Trainings-KI wird bis Ende des Jahres etwa 8.000 NVIDIA H100-GPUs entsprechen

Jul 24, 2024 am 10:38 AM

Tesla Dojo-Supercomputing-Debüt, Musk: Die Rechenleistung der Trainings-KI wird bis Ende des Jahres etwa 8.000 NVIDIA H100-GPUs entsprechen

Jul 24, 2024 am 10:38 AM

Laut Nachrichten dieser Website vom 24. Juli erklärte Tesla-CEO Elon Musk (Elon Musk) in der heutigen Telefonkonferenz zu den Ergebnissen, dass das Unternehmen kurz vor der Fertigstellung des bisher größten Schulungsclusters für künstliche Intelligenz stehe, das mit 2.000 NVIDIA H100 ausgestattet sein werde GPUs. Musk teilte den Anlegern bei der Gewinnmitteilung des Unternehmens auch mit, dass Tesla an der Entwicklung seines Dojo-Supercomputers arbeiten werde, da GPUs von Nvidia teuer seien. Diese Seite übersetzte einen Teil von Musks Rede wie folgt: Der Weg, über Dojo mit NVIDIA zu konkurrieren, ist schwierig, aber ich denke, wir haben keine andere Wahl. Wir sind jetzt zu sehr auf NVIDIA angewiesen. Aus der Sicht von NVIDIA werden sie den Preis für GPUs unweigerlich auf ein Niveau erhöhen, das der Markt ertragen kann, aber

Der Tesla Cybertruck springt von einer Klippe, um herauszufordern – eine Powershow jenseits aller Grenzen!

Mar 07, 2024 pm 09:28 PM

Der Tesla Cybertruck springt von einer Klippe, um herauszufordern – eine Powershow jenseits aller Grenzen!

Mar 07, 2024 pm 09:28 PM

Laut Nachrichten vom 7. März wurde kürzlich im Internet ein Video veröffentlicht, in dem ein Tesla Cybertruck in der Kleinstadt Utah in den USA den „Road to Hell's Revenge“ herausfordert. Cliff liegt in Salt Lake City, Utah, USA und ist ein beliebter Ort für Outdoor-Enthusiasten. Hier gibt es mehr als 30 Offroad-Straßen und die schroffen und steilen Felswände locken viele extreme Offroad-Enthusiasten zu Herausforderungen. Das Video zeigt, dass der Tesla Cybertruck, als er eine V-förmige Schlucht mit einer Neigung von fast 45 Grad herausforderte, sich auf die starke Kraft seiner drei Motoren verließ, um den Hang stetig hinaufzusteigen und schließlich erfolgreich den Gipfel erreichte. Während des Aufstiegs verhielt sich der Cybertruck trotz der rutschigen Felsoberfläche gut und verrutschte nicht. Nach dem Verständnis des Herausgebers sind die Tesla Cybertruck-Modelle in einmotorige Heckmodelle unterteilt

Die neue Hochleistungsversion des Modells 3 von Tesla hat die koreanische Zertifizierung bestanden, und die Leistungsparameter wurden offengelegt und erregten Aufmerksamkeit

Mar 06, 2024 pm 08:49 PM

Die neue Hochleistungsversion des Modells 3 von Tesla hat die koreanische Zertifizierung bestanden, und die Leistungsparameter wurden offengelegt und erregten Aufmerksamkeit

Mar 06, 2024 pm 08:49 PM

Laut Nachrichten vom 6. März enthüllten die Medien kürzlich, dass Teslas neue Hochleistungsversion Model 3 die relevanten koreanischen Zertifizierungen bestanden und eine Reihe auffälliger Leistungsparameter offengelegt hat. Es wird berichtet, dass dieses neue Auto mit einem fortschrittlichen Doppelmotorsystem ausgestattet sein wird, einschließlich eines vorne montierten 3D3-Induktions-Asynchronmotors und eines hinten montierten 4D2-Permanentmagnet-Synchronmotors. Die beiden arbeiten zusammen, um eine erstaunliche Leistung zu erzielen. Konkret leistet der vordere Motor 215 PS, während der hintere Motor bis zu 412 PS leistet, was die Gesamtleistung des Fahrzeugs auf erstaunliche 461 kW bringt. Allein der hintere 4D2-Motor hat eine Leistung von ca. 303 kW. Das Motordesign dieses neuen Autos kann die Spitzenleistung erreichen, wenn die Geschwindigkeit 110 km/h erreicht, wodurch das neue Modell 3 bei hohen Geschwindigkeiten eine bessere Leistung erbringt.

Die FSD-Technologie von Tesla überrascht Deutschland und autonomes Fahren ist vielversprechend für die Zukunft

Apr 29, 2024 pm 01:20 PM

Die FSD-Technologie von Tesla überrascht Deutschland und autonomes Fahren ist vielversprechend für die Zukunft

Apr 29, 2024 pm 01:20 PM

Laut Nachrichten vom 29. April hat Tesla kürzlich seine mit Spannung erwartete FSD-Technologie für vollständig autonomes Fahren zum ersten Mal in Deutschland öffentlich demonstriert und damit den offiziellen Eintritt der FSD-Technologie in den europäischen Markt markiert. Während der Demonstrationsveranstaltung hatte Rikard Fredriksson, leitender Berater des schwedischen Verkehrsministeriums, Gelegenheit, es selbst zu erleben. Er nahm ein Tesla Model Y und erlebte persönlich den Komfort von FSD (vollständig autonomes Fahren). Leistung auf deutschen Straßen. Fredriksson hatte produktsicherheitsrelevante Positionen in den Automobilprojekten von Apple inne und verfügt über ein tiefgreifendes Verständnis der autonomen Fahrtechnologie. Nach dem Erleben des Fahrassistenzsystems von Fredriksson ist das Fahren des FSD+12 sanft und natürlich. Er erwähnte dies auch ausdrücklich bei der Fahrt von der Münchner Innenstadt zum Flughafen

Teslas Q1-Finanzbericht 2024 angekündigt: Umsatzrückgänge, preisgünstige Modellproduktion auf der Agenda

Apr 24, 2024 pm 06:16 PM

Teslas Q1-Finanzbericht 2024 angekündigt: Umsatzrückgänge, preisgünstige Modellproduktion auf der Agenda

Apr 24, 2024 pm 06:16 PM

Laut Nachrichten vom 24. April hat Tesla heute seinen Finanzbericht für das erste Quartal 2024 veröffentlicht. Berichten zufolge erzielte Tesla im Quartal einen Umsatz von 21,301 Milliarden US-Dollar, ein Rückgang von 9 % im Vergleich zum Vorjahreszeitraum. Der Wert lag leicht unter den von Marktanalysten prognostizierten 22,3 Milliarden US-Dollar. Gleichzeitig betrug der Nettogewinn des Unternehmens 1,129 Milliarden US-Dollar, was einem starken Rückgang von 55 % im Vergleich zum Vorjahr entspricht. Tesla hat große Erfolge beim Fahrzeugverkauf erzielt. Im ersten Quartal wurden weltweit 386.800 Fahrzeuge ausgeliefert, deutlich weniger als die bisherigen Markterwartungen von rund 430.000 Fahrzeugen. Im Vergleich zum Vorjahreszeitraum sank die Liefermenge um 8,3 %, im Vergleich zum Vorquartal sank sie deutlich um 20,1 %. Dies ist Teslas erster Rückgang der Auslieferungen im Vergleich zum Vorjahr seit 2020. um langsamer zu werden

Die Shanghai Energy Storage Gigafactory von Tesla wird noch in diesem Jahr den Probebetrieb aufnehmen und einen geschätzten Energiespeicherumfang von fast 40 GWh haben

Mar 22, 2024 pm 12:32 PM

Die Shanghai Energy Storage Gigafactory von Tesla wird noch in diesem Jahr den Probebetrieb aufnehmen und einen geschätzten Energiespeicherumfang von fast 40 GWh haben

Mar 22, 2024 pm 12:32 PM

Der Bau von Shanghais Future Industry Pilot Zone feiert seinen „ersten Jahrestag“. Bei einer Pressekonferenz, die von Lu Yu, Direktor der High-Tech-Abteilung des Lingang New Area Management Committee, moderiert wurde, gab es wichtige Informationen über den mit Spannung erwarteten Tesla-Energiespeicher Projekt wurde enthüllt. Lu Yu sagte, dass das Projekt plant, die Testproduktion noch in diesem Jahr abzuschließen und der Produktionsumfang voraussichtlich bei etwa 40 GWh liegen wird. Diese Nachricht hat große Aufmerksamkeit erregt. Das Energiespeicherprojekt von Tesla ist von großer Bedeutung für die lokale Industrieentwicklung und die Nutzung erneuerbarer Energien. Als weltbekannter Hersteller von Elektrofahrzeugen hat Teslas Beteiligung im Bereich der Energiespeicherung große Aufmerksamkeit erregt. Durch die Zusammenarbeit mit Shanghai wird Teslas Bau von Energiespeicherprojekten in der Lingang New Area dazu beitragen, das lokale Industrieniveau und die technologischen Innovationsfähigkeiten zu verbessern. Lu Yu stellte außerdem Lingangs weitere Fortschritte im Bereich der neuen Energien vor. er erwähnte

Die Massenproduktion des Tesla Cybertruck zeigt positive Anzeichen, Luftaufnahmen der Fabrik in Texas zeigen eine großartige Produktionssituation

Mar 15, 2024 pm 12:04 PM

Die Massenproduktion des Tesla Cybertruck zeigt positive Anzeichen, Luftaufnahmen der Fabrik in Texas zeigen eine großartige Produktionssituation

Mar 15, 2024 pm 12:04 PM

Der Produktionsfortschritt von Teslas neuestem rein elektrischen Pickup-Truck, Cybertruck, hat viel Aufmerksamkeit erregt. Obwohl Tesla sich zurückgehalten hat, scheint ein kürzlich von einem Tesla-Beobachter namens Jeff Roberts aufgenommenes Luftbild der Texas Gigafactory positive Anzeichen für die Produktion von Cybertrucks für die Außenwelt zu offenbaren. Dem Video zufolge stehen in der Tesla Gigafactory in Texas bereits mehr als 300 Cybertrucks, verteilt auf verschiedene Gebiete. Diesmal handelt es sich um die größte Zahl an Cybertrucks, die jemals in der Fabrik gefunden wurde, was darauf hindeutet, dass sich die Massenproduktion des Modells schnell entwickelt. Dies zeigt, dass Tesla bei der Produktion des Cybertrucks erhebliche Fortschritte gemacht hat. Obwohl Tesla zuvor Bedenken hinsichtlich Cybertr geäußert hat