Technologie-Peripheriegeräte

Technologie-Peripheriegeräte

KI

KI

Die intelligente EDA-Welle steht vor der Tür. Wie hilft ChatGPT beim Design von Chips?

Die intelligente EDA-Welle steht vor der Tür. Wie hilft ChatGPT beim Design von Chips?

Die intelligente EDA-Welle steht vor der Tür. Wie hilft ChatGPT beim Design von Chips?

Woran denken Sie, wenn Sie ChatGPT erwähnen? Woran denken Sie, wenn Sie an Chips denken? Sie können das erste Wort aufschreiben, das Ihnen in den Sinn kommt. Nachdem Sie diesen Artikel gelesen haben, wird es Ihre Meinung definitiv ändern. Wenn Sie ein Technologie-Enthusiast sind, ist Ihr erster Eindruck, dass ChatGPT ein hochintelligentes Konversationsmodell ist, das mit Menschen sprechen kann. Die Chipindustrie ist ein komplexes Ganzes, das nicht nur Architekturdesigner auf höherer Ebene, sondern auch Prozesse auf niedrigerer Ebene umfasst Ingenieur. Möglicherweise kombinieren Sie die beiden nicht, weil sie scheinbar nichts miteinander zu tun haben.

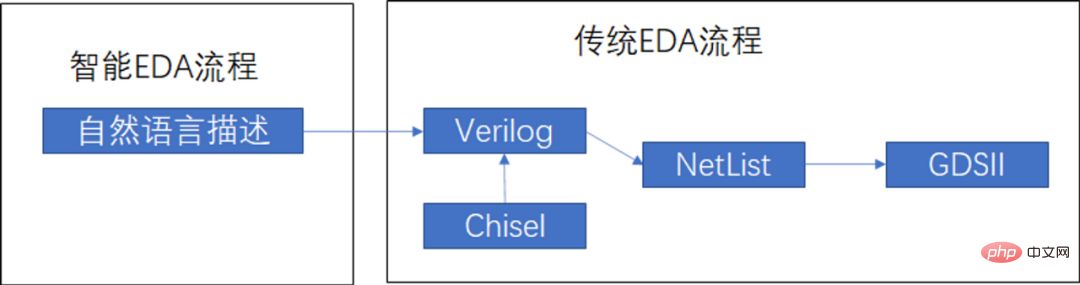

Aber tatsächlich beschleunigt die einzigartige Codegenerierungsfähigkeit des ChatGPT-Modells die Geschwindigkeit des Chipdesigns erheblich. Die Transformationswelle vom traditionellen EDA (Electronic Design Automation) zum intelligenten EDA steht kurz vor dem Beginn. Im heutigen Artikel werfen wir einen Blick darauf, wie sich das traditionelle EDA durch ChatGPT zu einem intelligenten EDA entwickelt und wie ChatGPT Innovationen in der Chip-Design-Branche vorantreibt Kette. .

Schauen wir uns zunächst eine Anwendung von ChatGPT an der Spitze der Chipindustrie an: Der Quantenkontrollprozessor ist der zentrale Kontrollteil des Quantencomputers. Der Code eines mit ChatGPT synthetisierten Quantenkontrollprozessors lautet wie folgt.

module QuantumControlProcessor ( input clk, input reset, input [7:0] instruction, input [7:0] control, output reg [7:0] qubit_pulse, output reg [7:0] timing_pulse ); // 此处因为篇幅原因省略实现 endmodule

Tatsächlich weist dieser Code möglicherweise einige kleinere Probleme auf. Beispielsweise kann ChatGPT keine gute Zeitsteuerung erreichen und Taktzyklen verschwenden. Vielleicht werden Sie überrascht sein, wie geht das? Wie sind die Aussichten dafür? Der Rest dieses Artikels wird Ihnen die Antwort geben.

Die Änderungen, die ChatGPT möglicherweise für den Chipdesignprozess mit sich bringt

ChatGPT wird genügend wiederverwendbaren Code für die Chipindustrie bereitstellen

Die enorme Menge an Designcode, die die Chipindustrie benötigt, erfordert dringend eine effiziente Entwicklungstools . Chip-Design ist eine Branche, die viel Code erfordert. Beispielsweise beträgt der Kern-Open-Source-Code von Alibabas Xuantie OpenC910 etwa 351 KLOC. Wie in Abbildung 1 dargestellt, beginnt die Branche im Allgemeinen mit dem Design beim Top-Verilog und verwendet die Front-End- und Back-End-Tools von EDA, um Layouts zu generieren. Das Schreiben von Verilog erfordert ein Design-Timing, das normalerweise komplex ist, sodass ChatGPT durch die Generierung dieses Codestücks viele Arbeitskosten senken kann. Die Timing-Anforderungen des Chips sind relativ streng, daher gibt es auch eine große Anzahl zeitbezogener Module mit relativ festen Funktionen, wie AXI-Schnittstelle, FIFO usw. Diese Module können alle ChatGPT nutzen, um die Arbeitskosten zu senken. Obwohl es derzeit neue Hardware-Designsprachen wie Chisel, Spatial und MyHDL gibt, unterliegen diese Sprachen weitgehend den Einschränkungen der Hostsprache und können Schaltkreise nicht auf eine Weise beschreiben, die der natürlichen Sprache nahe kommt.

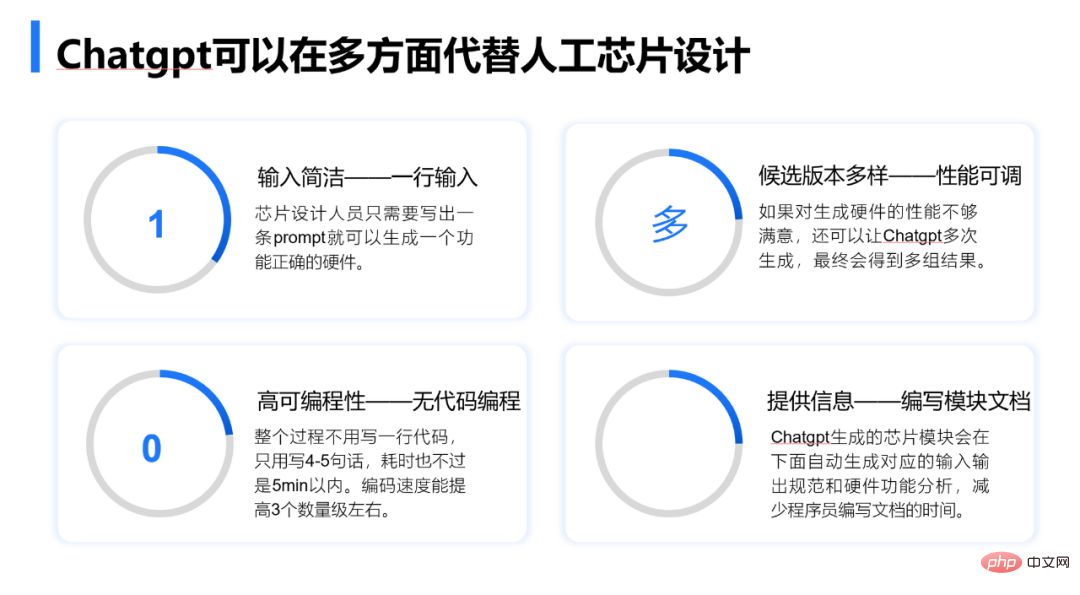

ChatGPT zeigt hervorragende Ausdrucksfähigkeiten bei der Codegenerierung. Geben Sie einfach eine Aufgabenaufforderung ein und der entsprechende Code wird automatisch generiert. Im Vergleich zur Synthese von Software und Algorithmen gibt es feste Muster, denen man folgen muss, da Hardware-Designcode nicht über die Vielfalt an Szenarien wie Software-Geschäftscode verfügt und seine Parametrisierung und Zeitsteuerung im Vergleich zu den kognitiven Fähigkeiten des Menschen komplex sind. Daher bietet ChatGPT mehr offensichtliche Vorteile bei der automatischen Generierung von Hardware-Designcode. Es verfügt über gute Induktionsfähigkeiten für vorhandene Hardware und kann parametrierbare Konfigurationspunkte in der Designvorlage genau extrahieren.

Der Dozent des Autors, Dr. Wang Ying, assoziierter Forscher am Institut für Computertechnologie der Chinesischen Akademie der Wissenschaften, glaubt, dass selbst ein vollständig industrialisiertes ChatGPT kurzfristig nicht in der Lage sein wird, die idealen vollautomatischen Designfunktionen bereitzustellen Im Einklang mit dem Trend von Cloud EDA wird jedoch erwartet, dass es als Designassistent die Effizienz der Designverifizierung erheblich verbessert und die Entwicklungsschwelle senkt. Darüber hinaus wird es wichtige Änderungen mit sich bringen. Der von ChatGPT in verschiedenen Prozessen gezeigte Automatisierungsgrad ist nicht ohne bessere SOTA-Technologie im EDA-Bereich, aber ChatGPT hat natürliche Vorteile in Bezug auf Vollständigkeit und natürliche Interaktion. Schließlich hat ChatGPT das Potenzial großer Modelle im Bereich des automatisierten Chipdesigns überprüft und kann Entwickler dazu anregen, das Prompt-Paradigma darauf weiter zu entwerfen, wodurch Raum für eine weitere Verbesserung der Funktionsgenauigkeit des Designs und der Leistung bleibt erzeugte Chips.

Das intellektuelle Niveau von ChatGPT im Bereich Chip-Design übertrifft frühere ähnliche Arbeiten bei weitem

ChatGPT 真的有替代人工的准确性吗?

ChatGPT 和之前最好的代码自动生成的方法比起来好了多少呢?

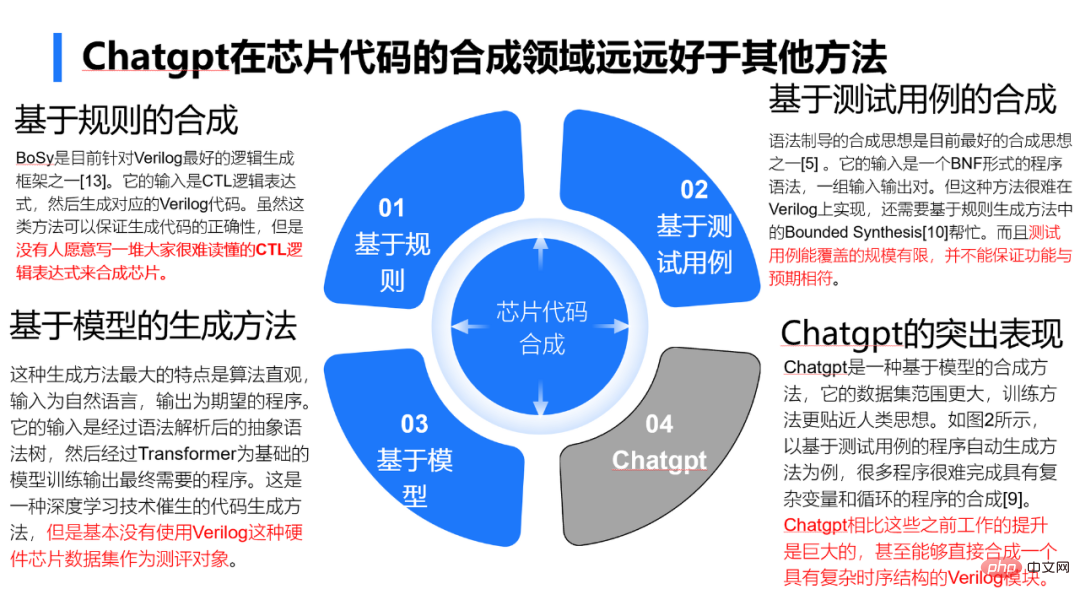

可以把之前的代码生成方法分为三类,一类是以编程语言社区为代表的基于规则 [11,12,13] 的方法,第二类是基于测试用例的生成方法 [5, 6, 7, 8, 9, 10],第三类是以自然语言处理社区为代表的基于文本和模型的生成方法 [1, 2, 3, 4]。

表:比较 OpenAI 两种最新模型用于代码生成

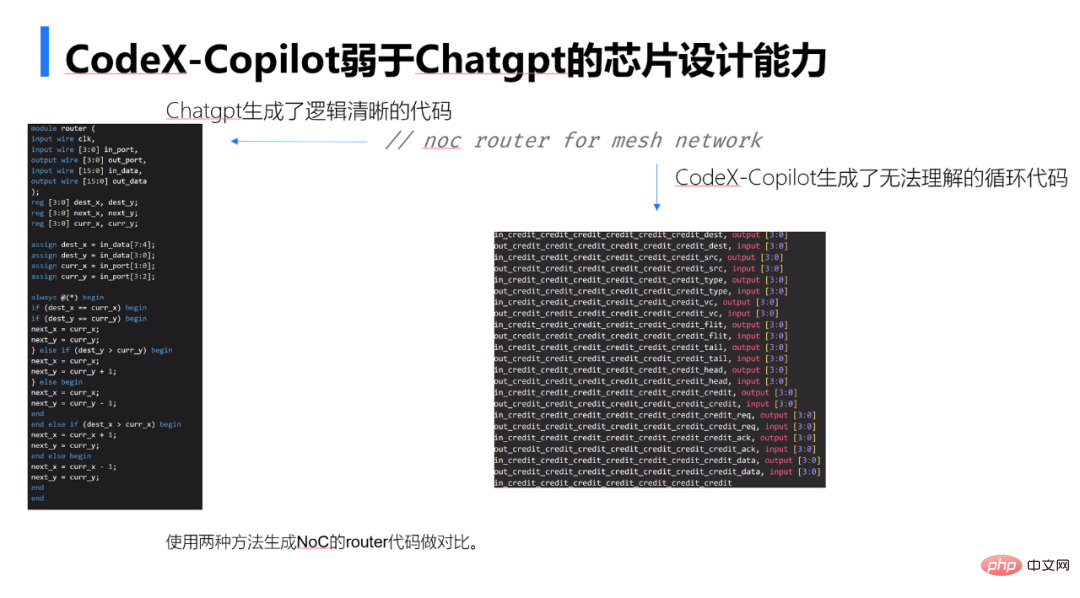

ChatGPT 和 CodeX 都是 OpenAI 公司基于 GPT-3 研发的模型,从上面的分析中可以看出,ChatGPT 的范围更广,并且 Copilot 的用途单一,仅仅为代码补全。这就为基于 ChatGPT 开发智能代码相关工具提供了更广阔的空间。

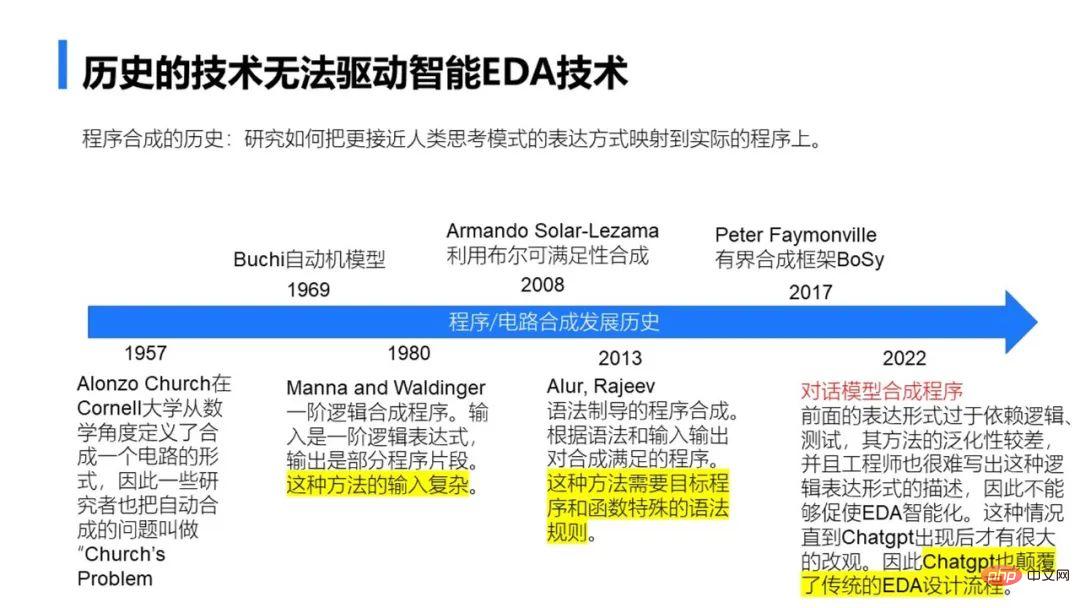

ChatGPT 极大地驱动了智能 EDA 技术的发展

在 ChatGPT 出现之前,就有许多自动化代码生成方式,他们为什么不能够驱动智能 EDA 技术呢?

ChatGPT 在芯片设计代码上有一系列潜在的应用

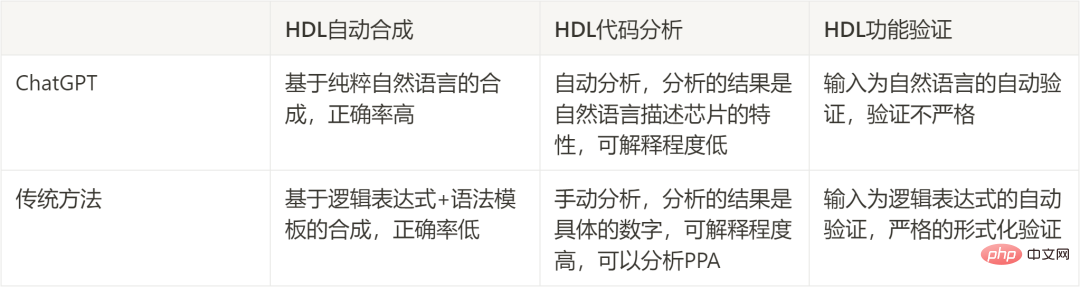

ChatGPT 能够远远地超越传统方法,并且它可以做到零样本学习(Zero-shot learning),相比传统的程序合成并不需要专门的训练(因为 OpenAI 已经完成了),并且配合细致的功能描述,他庞大的知识储备也可以使能高正确率的代码生成。如表 1 所示,ChatGPT 将会逐渐演变为芯片前端的自动化流程中极为关键的一步,在未来很有可能演变成为继 HLS 开创 C 语言设计芯片后的又一种新的范式。在后文,我们将会介绍如何使用 ChatGPT 做 Verilog 的代码生成。

表 1:ChatGPT 在芯片自动生成各个领域的开创性创新(以 Hardware Design Language 为例,软件语言可以参照分析)

如何使用 ChatGPT 生成芯片代码

与芯片设计相关的程序合成方法包含两类,高层次程序生成和时序相关硬件描述代码生成。高层次程序生成可以生成 HLS 等不具有显式时序控制的 C/C++ 代码等,而低层次程序生成可以生成具有显式时序控制的 Verilog 代码。由于 HLS 在实际工业界设计芯片时较少采用,因此我们采用 Verilog 作为主要的目标语言。对于 ChatGPT 而言,我们以自然语言描述作为输入,就可以获得符合要求的芯片描述代码。具体来说,应该如何做呢?我们以 Verilog 为例介绍如何用 ChatGPT 生成代码。

基于 ChatGPT 的通用生成步骤

act as a professional verilog programmer

因为 ChatGPT 是个通用的代码生成工具,而 Verilog 是个专用领域,我们需要先 “催眠” ChatGPT,使得它能够生成 Verilog 程序。向 ChatGPT 中输入下面的 prompt,之后的生成都会是以 Verilog 代码为基础的。

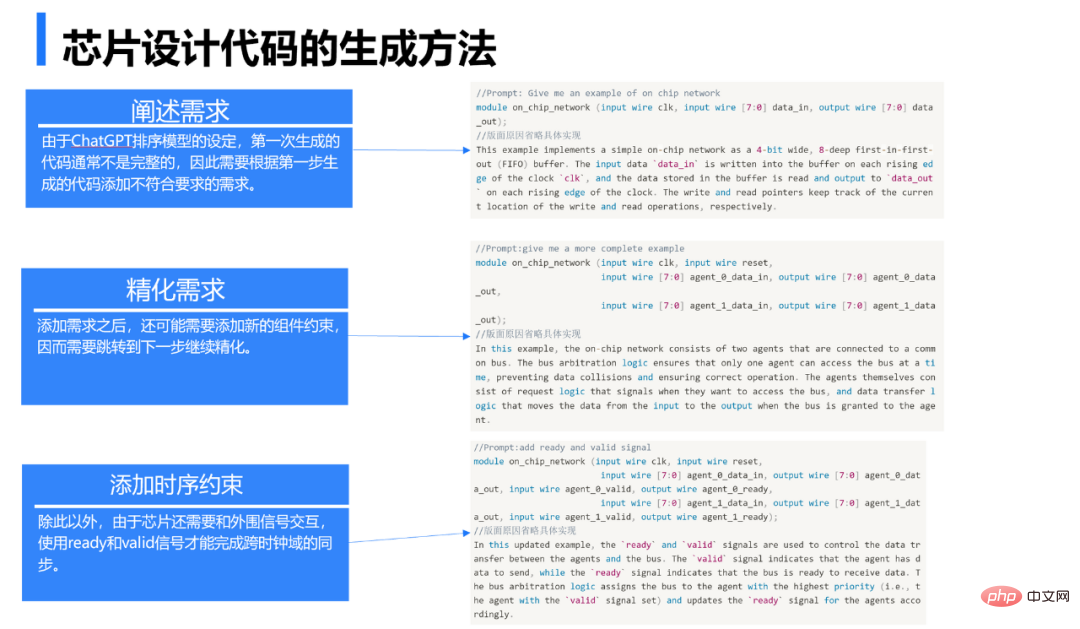

我们接下来的部分都是以片上网络 NoC 模块为例阐述代码生成方法的通用步骤。

Aus Platzgründen wird der vollständige von ChatGPT generierte Code hier nicht aufgeführt. Wir können jedoch sehen, dass es viele verschiedene Möglichkeiten gibt, das Schlüsselwort „On-Chip-Netzwerk“ zu verstehen, und ChatGPT hat sich für eine busbasierte Verständnismethode entschieden. Wenn wir andere Wege des semantischen Verständnisses wünschen, sollten wir verschiedene Möglichkeiten der Eingabe von Fragen erkunden.

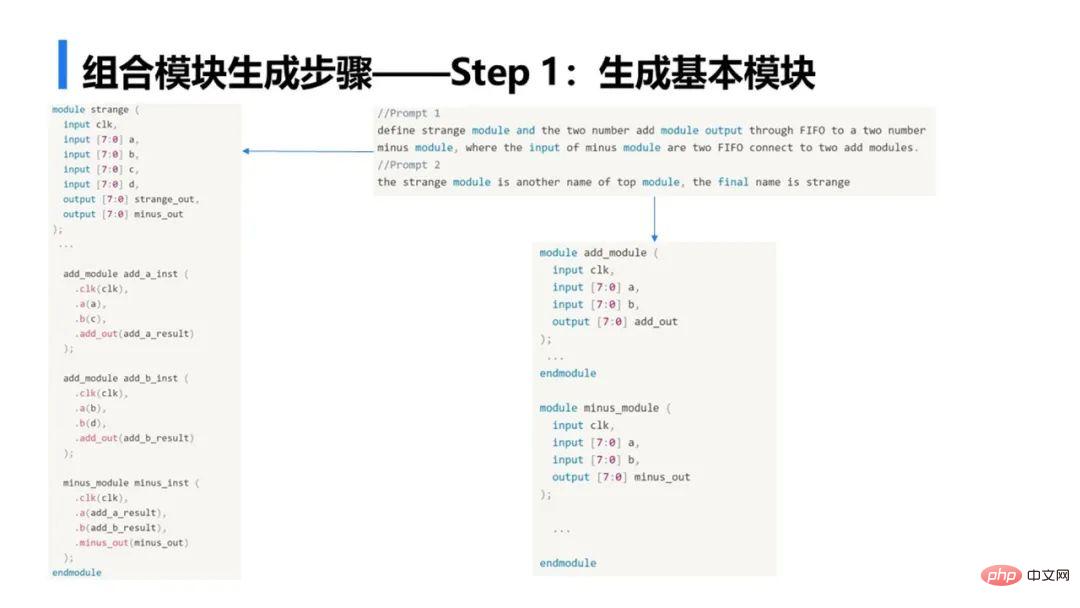

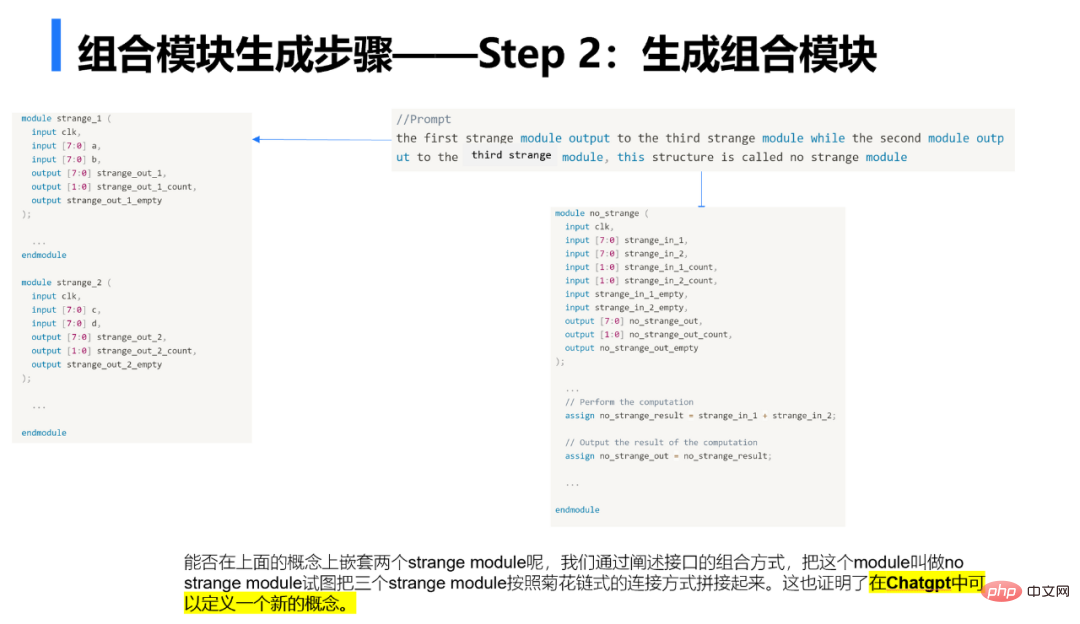

Schritte zum Kombinieren und Generieren von Modulen

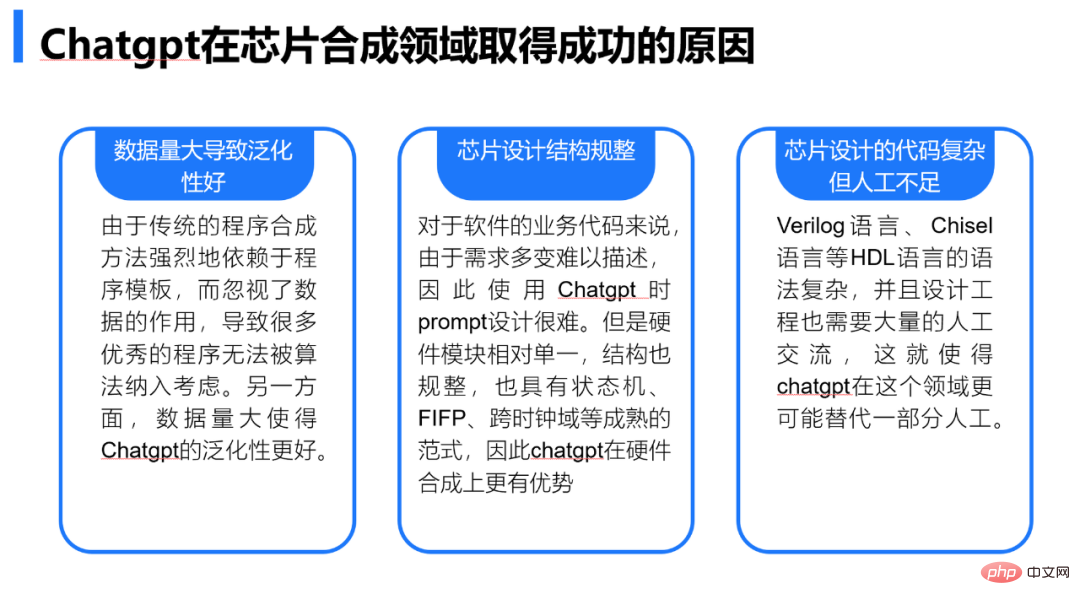

Zuvor wurden nur begrenzte Module generiert, aber können die Module kombiniert werden? Unser Ziel ist es, zwei seltsame Module, die ursprünglich nicht existierten, zu einem nicht seltsamen Modul zu kombinieren. Unten wird ein Modul der obersten Ebene generiert. Auf der unteren Ebene befinden sich zwei Addierer, deren Ausgänge mit einem Subtrahierer verbunden sind. Warum ChatGPT im Bereich der Chip-Generierung erfolgreich sein kann?

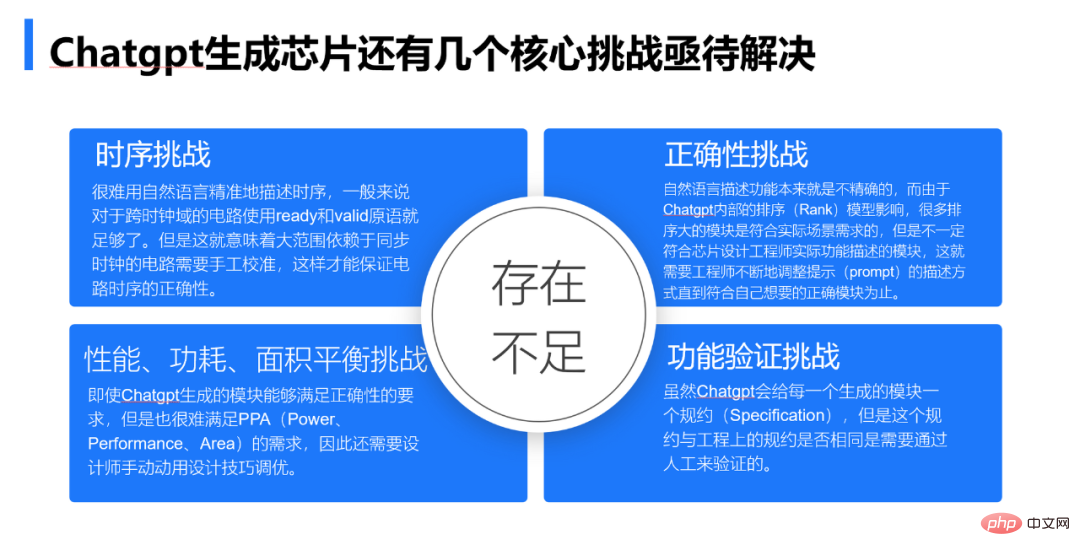

Obwohl das ChatGPT-Modell einen Teil der Front-End-Arbeit des Chipdesigns abschließen kann, gibt es immer noch die folgenden Herausforderungen: die manuelle Arbeit und die EDA-Werkzeugkette erfordern. Durch Gelenkabstimmung kann ein Chip erzeugt werden, der den Spezifikationen entspricht.

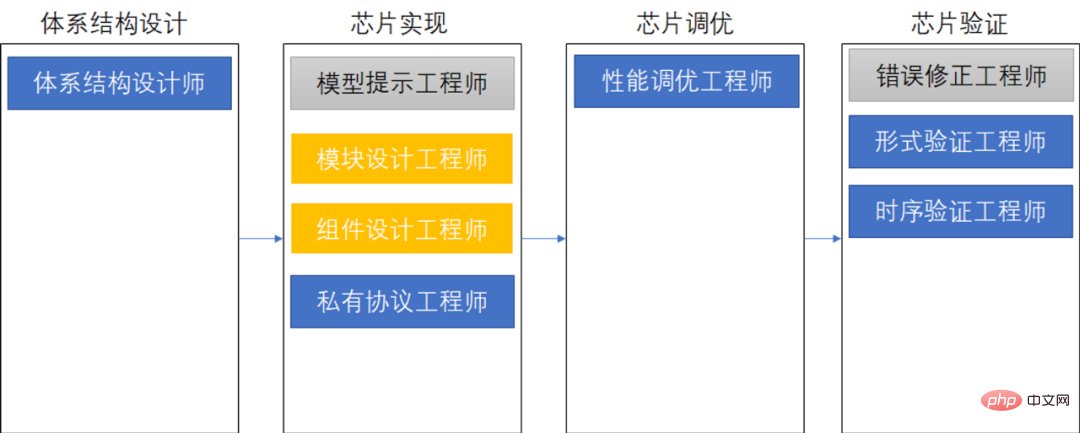

ChatGPT Als intelligenter EDA-Prozess ist es sowohl eine Krise als auch eine Chance. Es kann einen Teil der EDA-Front-End-Arbeit ersetzen. Da das EDA-Back-End jedoch stark auf Determinismus und Detailanalyse angewiesen ist, um eine bessere Optimierungsstruktur zu erhalten, ist es schwierig, die EDA-Back-End-Optimierungsarbeit zu unterstützen. Es werden aber auch neue Positionen geschaffen, beispielsweise mögliche Modell-Prompt-Ingenieure und Fehlerkorrektur-Ingenieure. Abbildung 5: Substituierbarkeit nach Ingenieurpositionen ist in vier Phasen unterteilt, nämlich Architekturentwurfsphase – Chipcode-Implementierungsphase – Chip-PPA-Tuning-Phase – Chip-Verifizierungsphase, wie in Abbildung 5 dargestellt. Beachten Sie, dass sich das Chip-Tuning hier auf das Tuning bezieht, das durch die Änderung einiger Hardwarestrukturen und Algorithmen am Front-End erreicht wird, sodass es vor der Chip-Verifizierung aufgeführt wird. Blaue Kästchen stellen Positionen dar, die schwer zu ersetzen sind, gelbe Kästchen stellen Positionen dar, die leicht ersetzt werden können, und graue Kästchen stellen neu hinzugefügte Positionen dar. Die folgende Analyse der Ersetzbarkeit nach spezifischen Prozessen zeigt, warum Ingenieure in manchen Positionen leicht durch ChatGPT ersetzt werden können, während Ingenieure in manchen Positionen schwer durch ChatGPT zu ersetzen sind.

Der Forscher Han Yinhe, Direktor des Intelligent Computing Center des Instituts für Computertechnologie der Chinesischen Akademie der Wissenschaften, glaubt, dass ChatGPT nicht nur dazu beitragen kann, den Chip-Designprozess zu beschleunigen, sondern auch eine Reihe von Herausforderungen für den Chip mit sich bringt selbst, was die aktuell heißen Themen wie Speicher- und Berechnungsintegration, Chip-Integration und große Chips-Architektur und andere Technologien sein können, die mit Spannung erwartete Killeranwendungen hervorbringen.

Prozesse, die schwer zu ersetzen sind

Neu hinzugefügte Prozesse

- Bug Fix Engineer. Da das von ChatGPT generierte Programm möglicherweise detaillierte Probleme aufweist und einige Stellen nicht den Timing- oder Verbindungsstandards zwischen Modulen entsprechen, müssen Fehlerkorrekturingenieure diese beheben.

- Model Prompt Engineer. Die Qualität des von ChatGPT generierten Codes hängt eng mit der Eingabeaufforderung zusammen. Daher ist es für einige Personen, die mit dem „Temperament“ von ChatGPT vertraut sind, erforderlich, die Eingabeaufforderung speziell zu entwerfen, um Code zu generieren, der den Spezifikationen entspricht.

Zukünftiger Entwicklungstrend

Im Zuge der intelligenten EDA werden einige Positionen zwangsläufig ersetzt. In welcher Reihenfolge werden sie also in Zukunft ersetzt? Aus Sicht der Front-End- und Back-End-Verteilung ist das Back-End aufgrund seiner Detailaufgaben wie der Layoutgestaltung höchst unersetzlich. Für das Front-End ist der erste Ersatz der Modulingenieur bei der Chip-Implementierung, da aus der oben beschriebenen Praxis der Chip-Generierung hervorgeht, dass der grundlegende Teil der Modulcode-Generierung am intuitivsten ist. Die Ersatzpositionen, die danach angezeigt werden, sind Komponentendesigningenieure. Dieses Teil wird ersetzt, sobald Ingenieure mit der Verwendung von ChatGPT zum Zusammenbau von Modulen vertraut sind. Für andere Ingenieure ist ChatGPT eher ein Zusatznutzen als ein vollständiger Ersatz.

Daher können wir sehen, dass je höher die Ebene, desto unwahrscheinlicher ist es, die Teile zu ersetzen, die architektonische Abstraktion betreffen. Je niedriger die Ebene, desto unwahrscheinlicher ist es, die Teile zu ersetzen, die Korrektheit betreffen. Die Ersetzungsreihenfolge des Mittelteils erfolgt von unten nach oben, vom Basismodul zu den Komponenten der oberen Ebene. Die Politik besteht darin, die Chance intelligenter EDA zu nutzen. Es gibt komplexe Gründe, warum traditionelle EDA- und große Modelle bei OpenAI erstmals vorgestellt wurden, andere Unternehmen jedoch noch nicht aufgeholt haben. Allerdings muss die Politik immer noch Hand anlegen, um etwas überhitztes Kapital von Projekten abzulenken, die traditionelle EDA- und große Modellprobleme lösen, und Unternehmen dazu ermutigen, das frühe Stadium der intelligenten EDA-Entwicklung zu ergreifen, wenn die Branchenbarrieren gering sind, mutig in die Branche einzusteigen und zu bauen neue Produkte. Nur so können wir das Problem lösen, ständig durch neue Technologien ersetzt zu werden. Andernfalls führt der Zufluss von überhitztem Kapital in reife Industrien zu einem Rückgang der Kapitalrendite. Gleichzeitig können innovative Technologien keine höhere finanzielle Unterstützung erhalten, was dazu führt, dass innovative Unternehmen es nicht wagen, Fehler zu machen Die Trial-and-Error-Kosten innovativer Unternehmen steigen praktisch, sodass innovative Unternehmen markterprobte Technologien bevorzugen. Daher sollten Richtlinien Unternehmen angemessen dazu ermutigen, abgeleitete Technologien zu entwickeln, die auf großen Modellen wie ChatGPT basieren. Insbesondere da große Modelle starke Fähigkeiten zur Codegenerierung gezeigt haben, sollten Unternehmen, die auf intelligenter EDA-Technologie basieren, die Chance nutzen.

Der Investitionsschwerpunkt des Kapitalmarktes sollte sich vom großen Modell selbst auf seine abgeleiteten Technologien verlagern

Im Bereich der Informationstechnologie bewegen sich fortschrittliche Technologien weiterhin von allgemein zu spezialisiert und bewegen sich allmählich in diese Richtung Abgeleitete Technologien, die auf früheren Technologien basieren, müssen verarbeitet werden. Dies ist am offensichtlichsten im Bereich des Gerätedesigns. Im letzten Jahrhundert waren CPUs sehr beliebt und schufen Hochleistungscomputer. Zu Beginn dieses Jahrhunderts wurden GPUs allmählich populär und trieben die Entwicklung von Spielen voran. In den letzten zehn Jahren haben NPUs begonnen, die Bühne zu betreten Energieeffizientes neuronales Netzwerktraining und Denken. Daraus lässt sich schließen, dass mit der Reife des großen Modells in den nächsten Jahren auch seine abgeleiteten Technologien auf die Bühne kommen werden. Die intelligente EDA-Technologie ist eine Ableitung der Großmodelltechnologie. Auch wenn Investitionen in abgeleitete Technologien zu Beginn nicht vorteilhaft zu sein scheinen, wird die Kapitalrendite aus wirtschaftlicher Sicht höher sein, bis diese Technologie auf den Markt kommt und eine technische Barriere bildet. Mit zunehmender Reife großer Modelltechnologien wie ChatGPT werden Investitionen in Unternehmen abnehmende marginale Auswirkungen haben. Privatanleger und institutionelle Anleger sollten die Investitionsregeln der Informationstechnologie erkennen und ihre Aufmerksamkeit schrittweise auf die abgeleiteten Bereiche großer Modelle richten, insbesondere auf die Anwendung von Algorithmen, die auf großen Modellen im Chipbereich basieren. Industriepraktiker sollten die Vorteile der in meinem Land eingerichteten großen Fonds für die Bereiche künstliche Intelligenz und integrierte Schaltkreise voll ausschöpfen und sich aktiv um Fonds bewerben, die künstliche Intelligenz und EDA überschneiden. Daher ist der Bereich der intelligenten EDA sowohl aus industriepolitischer als auch aus investitionsrechtlicher Sicht äußerst notwendig und sollte ein Investitionsziel für chinesische Investoren werden. Verwandte Literatur

Codegenerierung basierend auf Textmodell

[1] Zhangyin Feng, Daya Guo, Duyu Tang, Nan Duan, Xiaocheng Feng, Ming Gong, Linjun Shou, Bing Qin, Ting Liu, Daxin Jiang und Ming Zhou. 2020. [CodeBERT: Ein vorab trainiertes Modell für Programmierung und natürliche Sprachen]. In Findings of the Association for Computational Linguistics: EMNLP 2020, Seiten 1536–1547, Online. Association for Computational Linguistics.

[2] [GRAPHCODEBERT: PRE-TRAINING CODE REPRÄSENTATIONEN MIT DATA FLOW]

[3] [CodeT5: Identifier-aware Unified Pre-trained Encoder-Decoder Models for Code Understanding and Generation ]

[4] [UniXcoder: Unified Cross-Modal Pre-training for Code Representation]

基于测试用例的代码生成

[5] Rajeev Alur, Rastislav Bodík, Garvit Juniwal , Milo M. K. Martin, Mukund Raghothaman, Sanjit A. Seshia, Rishabh Singh, Armando Solar-Lezama, Emina Torlak, Abhishek Udupa, [Syntax-gesteuerte Synthese], 2013

[6] Peter-Michael Osera, Steve Zdancewic, [Typ- und beispielgesteuerte Programmsynthese], 2015

[7] John K. Feser, Swarat Chaudhuri, Isil Dillig, [Synthesizing Data Structure Transformations from Input-output Examples], 2015

[8 ] Armando Solar-Lezama, [Program Synthesis by Sketching], 2008

[9] [Kensen Shi], [Jacob Steinhardt], [Percy Liang], FrAngel: Component-Based Synthesis with Control Structures, POPL, 2019

[10] Yu Feng, Ruben Martins, Yuepeng Wang, Isil Dillig, Thomas W. Reps, Komponentenbasierte Synthese für komplexe APIs, [ACM SIGPLAN Notices], 2017

基于逻辑规则的代码生成

[11] Z. Manna und R. Waldinger, „Synthesis: Dreams → Programs“, in IEEE Transactions on Software Engineering, vol. SE-5, nein. 4, S. 294-328, Juli 1979, doi: 10.1109/TSE.1979.234198.

[12] Bernd Finkbeiner und Sven Schewe, Bounded synthesize, in Int J Softw Tools Technol Transfer, (2013), 15:519 –539, DOI: 10.1007/s10009-012-0228-z

[13] Peter Faymonville, Bernd Finkbeiner und Leander Tentrup, BoSy: An Experimentation Framework for Bounded Synthesis, CAV 2017

Das obige ist der detaillierte Inhalt vonDie intelligente EDA-Welle steht vor der Tür. Wie hilft ChatGPT beim Design von Chips?. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!

Heiße KI -Werkzeuge

Undresser.AI Undress

KI-gestützte App zum Erstellen realistischer Aktfotos

AI Clothes Remover

Online-KI-Tool zum Entfernen von Kleidung aus Fotos.

Undress AI Tool

Ausziehbilder kostenlos

Clothoff.io

KI-Kleiderentferner

AI Hentai Generator

Erstellen Sie kostenlos Ai Hentai.

Heißer Artikel

Heiße Werkzeuge

Notepad++7.3.1

Einfach zu bedienender und kostenloser Code-Editor

SublimeText3 chinesische Version

Chinesische Version, sehr einfach zu bedienen

Senden Sie Studio 13.0.1

Leistungsstarke integrierte PHP-Entwicklungsumgebung

Dreamweaver CS6

Visuelle Webentwicklungstools

SublimeText3 Mac-Version

Codebearbeitungssoftware auf Gottesniveau (SublimeText3)

Heiße Themen

1377

1377

52

52

Mit ChatGPT können kostenlose Benutzer jetzt Bilder mithilfe von DALL-E 3 mit einem Tageslimit generieren

Aug 09, 2024 pm 09:37 PM

Mit ChatGPT können kostenlose Benutzer jetzt Bilder mithilfe von DALL-E 3 mit einem Tageslimit generieren

Aug 09, 2024 pm 09:37 PM

DALL-E 3 wurde im September 2023 offiziell als deutlich verbessertes Modell gegenüber seinem Vorgänger eingeführt. Er gilt als einer der bisher besten KI-Bildgeneratoren und ist in der Lage, Bilder mit komplexen Details zu erstellen. Zum Start war es jedoch exklusiv

So lösen Sie Win7-Treibercode 28

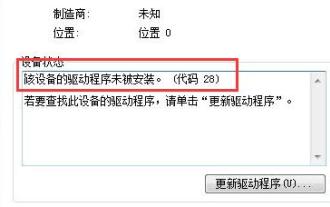

Dec 30, 2023 pm 11:55 PM

So lösen Sie Win7-Treibercode 28

Dec 30, 2023 pm 11:55 PM

Bei einigen Benutzern sind bei der Installation des Geräts Fehler aufgetreten, die den Fehlercode 28 angezeigt haben. Tatsächlich ist dies hauptsächlich auf den Treiber zurückzuführen. Wir müssen nur das Problem mit dem Win7-Treibercode 28 lösen. Schauen wir uns an, was zu tun ist . Was tun mit dem Win7-Treibercode 28? Zuerst müssen wir auf das Startmenü in der unteren linken Ecke des Bildschirms klicken. Suchen Sie dann im Popup-Menü nach der Option „Systemsteuerung“ und klicken Sie darauf. Diese Option befindet sich normalerweise am oder nahe dem unteren Rand des Menüs. Nach dem Klicken öffnet das System automatisch die Benutzeroberfläche des Bedienfelds. Im Bedienfeld können wir verschiedene Systemeinstellungen und Verwaltungsvorgänge durchführen. Dies ist der erste Schritt in der Nostalgie-Reinigungsstufe. Ich hoffe, er hilft. Dann müssen wir fortfahren und das System betreten und

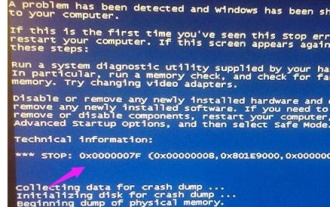

Was tun, wenn der Bluescreen-Code 0x0000001 auftritt?

Feb 23, 2024 am 08:09 AM

Was tun, wenn der Bluescreen-Code 0x0000001 auftritt?

Feb 23, 2024 am 08:09 AM

Was tun mit dem Bluescreen-Code 0x0000001? Der Bluescreen-Fehler ist ein Warnmechanismus, wenn ein Problem mit dem Computersystem oder der Hardware vorliegt. Der Code 0x0000001 weist normalerweise auf einen Hardware- oder Treiberfehler hin. Wenn Benutzer bei der Verwendung ihres Computers plötzlich auf einen Bluescreen-Fehler stoßen, geraten sie möglicherweise in Panik und sind ratlos. Glücklicherweise können die meisten Bluescreen-Fehler mit ein paar einfachen Schritten behoben werden. In diesem Artikel werden den Lesern einige Methoden zur Behebung des Bluescreen-Fehlercodes 0x0000001 vorgestellt. Wenn ein Bluescreen-Fehler auftritt, können wir zunächst versuchen, neu zu starten

Der Computer zeigt häufig einen Bluescreen an und der Code ist jedes Mal anders

Jan 06, 2024 pm 10:53 PM

Der Computer zeigt häufig einen Bluescreen an und der Code ist jedes Mal anders

Jan 06, 2024 pm 10:53 PM

Das Win10-System ist ein sehr hervorragendes, hochintelligentes System, das den Benutzern das beste Benutzererlebnis bieten kann. Unter normalen Umständen werden die Computer des Win10-Systems keine Probleme haben. Es ist jedoch unvermeidlich, dass bei hervorragenden Computern verschiedene Fehler auftreten. In letzter Zeit haben Freunde berichtet, dass ihre Win10-Systeme häufig auf Bluescreens stoßen! Heute stellt Ihnen der Editor Lösungen für verschiedene Codes vor, die häufige Bluescreens auf Windows 10-Computern verursachen. Lösungen für häufige Computer-Bluescreens mit jeweils unterschiedlichen Codes: Ursachen verschiedener Fehlercodes und Lösungsvorschläge 1. Ursache des Fehlers 0×000000116: Es sollte sein, dass der Grafikkartentreiber nicht kompatibel ist. Lösung: Es wird empfohlen, den Treiber des Originalherstellers zu ersetzen. 2,

Beheben Sie den Fehlercode 0xc000007b

Feb 18, 2024 pm 07:34 PM

Beheben Sie den Fehlercode 0xc000007b

Feb 18, 2024 pm 07:34 PM

Beendigungscode 0xc000007b Bei der Verwendung Ihres Computers treten manchmal verschiedene Probleme und Fehlercodes auf. Unter ihnen ist der Beendigungscode am störendsten, insbesondere der Beendigungscode 0xc000007b. Dieser Code weist darauf hin, dass eine Anwendung nicht ordnungsgemäß gestartet werden kann, was zu Unannehmlichkeiten für den Benutzer führt. Lassen Sie uns zunächst die Bedeutung des Beendigungscodes 0xc000007b verstehen. Bei diesem Code handelt es sich um einen Fehlercode des Windows-Betriebssystems, der normalerweise auftritt, wenn eine 32-Bit-Anwendung versucht, auf einem 64-Bit-Betriebssystem ausgeführt zu werden. Es bedeutet, dass es so sein sollte

Universal-Fernbedienungscode-Programm von GE auf jedem Gerät

Mar 02, 2024 pm 01:58 PM

Universal-Fernbedienungscode-Programm von GE auf jedem Gerät

Mar 02, 2024 pm 01:58 PM

Wenn Sie ein Gerät aus der Ferne programmieren müssen, hilft Ihnen dieser Artikel. Wir teilen Ihnen die besten Universal-Fernbedienungscodes von GE für die Programmierung aller Geräte mit. Was ist eine GE-Fernbedienung? GEUniversalRemote ist eine Fernbedienung, mit der mehrere Geräte wie Smart-TVs, LG, Vizio, Sony, Blu-ray, DVD, DVR, Roku, AppleTV, Streaming-Media-Player und mehr gesteuert werden können. GEUniversal-Fernbedienungen gibt es in verschiedenen Modellen mit unterschiedlichen Merkmalen und Funktionen. GEUniversalRemote kann bis zu vier Geräte steuern. Top-Universalfernbedienungscodes zum Programmieren auf jedem Gerät GE-Fernbedienungen werden mit einer Reihe von Codes geliefert, die es ihnen ermöglichen, mit verschiedenen Geräten zu arbeiten. Sie können

So installieren Sie ChatGPT auf einem Mobiltelefon

Mar 05, 2024 pm 02:31 PM

So installieren Sie ChatGPT auf einem Mobiltelefon

Mar 05, 2024 pm 02:31 PM

Installationsschritte: 1. Laden Sie die ChatGTP-Software von der offiziellen ChatGTP-Website oder dem mobilen Store herunter. 2. Wählen Sie nach dem Öffnen in der Einstellungsoberfläche die Sprache aus. 3. Wählen Sie in der Spieloberfläche das Mensch-Maschine-Spiel aus 4. Geben Sie nach dem Start Befehle in das Chatfenster ein, um mit der Software zu interagieren.

Ausführliche Erläuterung der Ursachen und Lösungen des Bluescreen-Codes 0x0000007f

Dec 25, 2023 pm 02:19 PM

Ausführliche Erläuterung der Ursachen und Lösungen des Bluescreen-Codes 0x0000007f

Dec 25, 2023 pm 02:19 PM

Bluescreen ist ein Problem, das bei der Nutzung des Systems häufig auftritt. Je nach Fehlercode gibt es viele verschiedene Gründe und Lösungen. Wenn wir beispielsweise auf das Problem „stop: 0x0000007f“ stoßen, kann es sich um einen Hardware- oder Softwarefehler handeln. Folgen wir dem Editor, um die Lösung herauszufinden. 0x000000c5 Bluescreen-Code-Grund: Antwort: Der Speicher, die CPU und die Grafikkarte sind plötzlich übertaktet oder die Software läuft falsch. Lösung 1: 1. Drücken Sie beim Booten weiterhin F8 zum Aufrufen, wählen Sie den abgesicherten Modus und drücken Sie zum Aufrufen die Eingabetaste. 2. Drücken Sie nach dem Aufrufen des abgesicherten Modus win+r, um das Ausführungsfenster zu öffnen, geben Sie cmd ein und drücken Sie die Eingabetaste. 3. Geben Sie im Eingabeaufforderungsfenster „chkdsk /f /r“ ein, drücken Sie die Eingabetaste und drücken Sie dann die Y-Taste. 4.