Technologie-Peripheriegeräte

Technologie-Peripheriegeräte

KI

KI

Das MIT fasst die letzten drei Jahre zusammen und veröffentlicht einen Übersichtsartikel zu KI-Beschleunigern

Das MIT fasst die letzten drei Jahre zusammen und veröffentlicht einen Übersichtsartikel zu KI-Beschleunigern

Das MIT fasst die letzten drei Jahre zusammen und veröffentlicht einen Übersichtsartikel zu KI-Beschleunigern

Im vergangenen Jahr haben sowohl Startups als auch etablierte Unternehmen nur langsam Beschleuniger für künstliche Intelligenz (KI) und maschinelles Lernen (ML) angekündigt, eingeführt und eingesetzt. Aber es ist nicht unangemessen, und viele Unternehmen, die Beschleunigerberichte veröffentlichen, verbringen drei bis vier Jahre damit, das Design des Beschleunigers zu erforschen, zu analysieren, zu entwerfen, zu validieren und abzuwägen und den Technologie-Stack zur Programmierung des Beschleunigers aufzubauen. Bei den Unternehmen, die aktualisierte Versionen ihrer Beschleuniger herausgebracht haben, betragen die Entwicklungszyklen immer noch mindestens zwei bis drei Jahre, obwohl sie berichten, dass sie kürzer sind. Der Schwerpunkt dieser Beschleuniger liegt weiterhin auf der Beschleunigung von Deep Neural Network (DNN)-Modellen. Die Anwendungsszenarien reichen von eingebetteter Spracherkennung und Bildklassifizierung mit extrem geringem Stromverbrauch bis hin zum Training großer Rechenzentren Ein wichtiger Teil des Wandels vom modernen traditionellen Computing hin zu Lösungen für maschinelles Lernen für Industrie- und Technologieunternehmen.

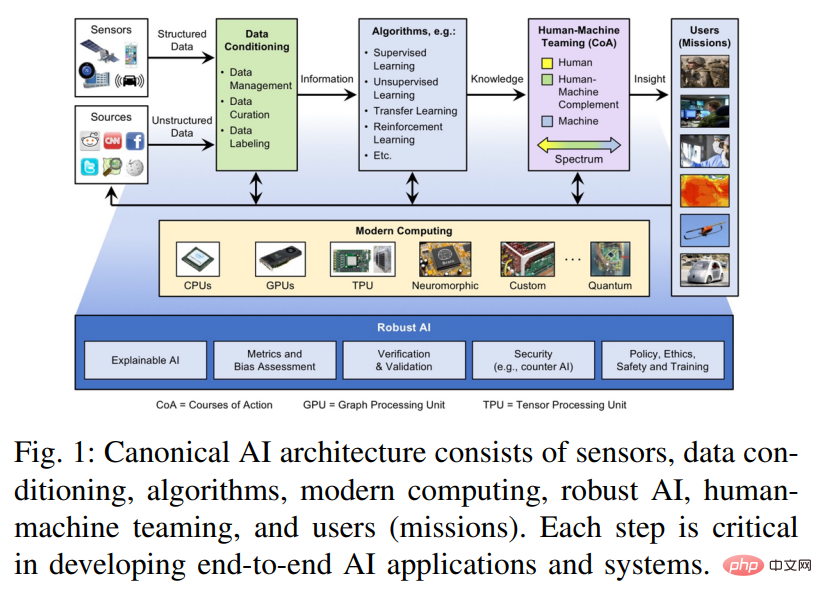

Das KI-Ökosystem vereint Komponenten des Edge Computing, des traditionellen Hochleistungsrechnens (HPC) und der Hochleistungsdatenanalyse (HPDA), die zusammenarbeiten müssen , um Entscheidungsträger, Mitarbeiter an vorderster Front und Analysten effektiv zu befähigen. Abbildung 1 zeigt einen Architekturüberblick über diese End-to-End-KI-Lösung und ihre Komponenten.

Die Originaldaten müssen zunächst datenkuratiert werden. In diesem Schritt werden die Daten fusioniert, aggregiert und strukturiert , gesammelt und in Informationen umgewandelt. Die durch den Data-Wrangling-Schritt generierten Informationen dienen als Eingabe für überwachte oder unüberwachte Algorithmen wie neuronale Netze, die Muster extrahieren, fehlende Daten ergänzen oder Ähnlichkeiten zwischen Datensätzen finden und Vorhersagen treffen, wodurch die Eingabeinformationen in umsetzbares Wissen umgewandelt werden. Dieses umsetzbare Wissen wird auf den Menschen übertragen und im Entscheidungsprozess während der Phase der Mensch-Maschine-Zusammenarbeit genutzt. Die Phase der Mensch-Maschine-Kollaboration liefert Benutzern nützliche und wichtige Erkenntnisse und wandelt Wissen in umsetzbare Intelligenz oder Erkenntnisse um.

Diesem System liegt ein modernes Computersystem zugrunde. Der Trend zum Mooreschen Gesetz ist beendet, aber gleichzeitig werden viele verwandte Gesetze und Trends vorgeschlagen, wie zum Beispiel das Denardsche Gesetz (Leistungsdichte), Taktfrequenz, Kernanzahl, Anweisungen pro Taktzyklus und Anweisungen pro Joule (Koomeys Gesetz). Vom System-on-a-Chip (SoC)-Trend, der erstmals in Automobilanwendungen, Robotik und Smartphones auftrat, schreitet die Innovation durch die Entwicklung und Integration von Beschleunigern häufig verwendeter Kerne, Methoden oder Funktionen weiter voran. Diese Beschleuniger bieten ein unterschiedliches Gleichgewicht zwischen Leistung und funktionaler Flexibilität, einschließlich einer Explosion von Innovationen bei Deep-Learning-Prozessoren und -Beschleunigern. In diesem Artikel werden die relativen Vorteile dieser Technologien durch die Lektüre einer großen Anzahl verwandter Artikel untersucht, da sie besonders wichtig für die Anwendung künstlicher Intelligenz in eingebetteten Systemen und Rechenzentren sind, in denen Größe, Gewicht und Leistung äußerst wichtig sind.

Dieser Artikel ist eine Aktualisierung der IEEE-HPEC-Papiere der letzten drei Jahre. Wie in den vergangenen Jahren konzentriert sich dieser Artikel weiterhin auf Beschleuniger und Prozessoren für Deep Neural Networks (DNN) und Convolutional Neural Networks (CNN), die äußerst rechenintensiv sind. Dieser Artikel konzentriert sich auf die Entwicklung von Beschleunigern und Prozessoren im Bereich Inferenz, da viele KI/ML-Edge-Anwendungen stark auf Inferenz angewiesen sind. In diesem Artikel werden alle von Beschleunigern unterstützten numerischen Präzisionstypen behandelt. Bei den meisten Beschleunigern ist die beste Inferenzleistung jedoch int8 oder fp16/bf16 (16-Bit-Gleitkomma von IEEE oder 16-Bit-Brain-Float von Google).

Papierlink: https://arxiv.org/pdf/2210.04055.pdf#🎜 🎜#

Derzeit gibt es viele Artikel über KI-Beschleuniger. Im ersten Artikel dieser Umfragereihe wird beispielsweise die Spitzenleistung von FPGAs für bestimmte KI-Modelle erörtert. Frühere Umfragen haben FPGAs ausführlich behandelt und sind daher nicht mehr in dieser Umfrage enthalten. Diese laufende Umfrage und dieser Artikel zielen darauf ab, eine umfassende Liste von KI-Beschleunigern zusammenzustellen, einschließlich ihrer Rechenfähigkeiten, Energieeffizienz und Recheneffizienz bei der Verwendung von Beschleunigern in eingebetteten Anwendungen und Rechenzentrumsanwendungen. Gleichzeitig werden in dem Artikel hauptsächlich neuronale Netzwerkbeschleuniger für staatliche und industrielle Sensor- und Datenverarbeitungsanwendungen verglichen. Einige Beschleuniger und Prozessoren, die in Veröffentlichungen aus früheren Jahren enthalten waren, wurden von der diesjährigen Umfrage ausgeschlossen, da sie möglicherweise durch neue Beschleuniger desselben Unternehmens ersetzt wurden, nicht mehr gewartet werden oder für das Thema nicht mehr relevant sind.

Prozessorumfrage

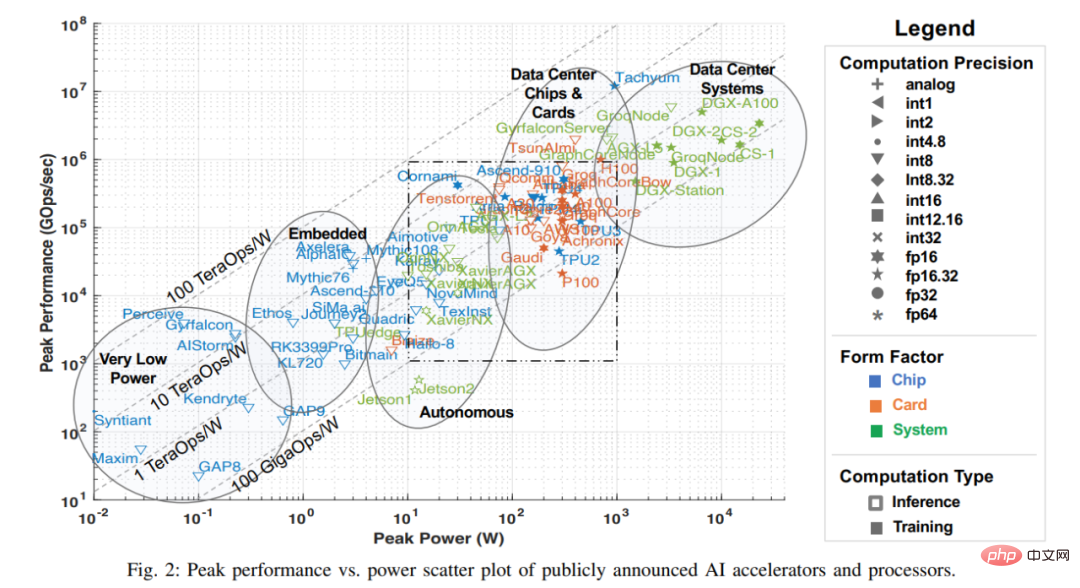

Viele aktuelle Fortschritte in der künstlichen Intelligenz sind teilweise auf Verbesserungen der Hardwareleistung zurückzuführen, die maschinelle Lernalgorithmen ermöglichen, die enorme Rechenleistung erfordern, insbesondere Netzwerke wie DNNs. Die Umfrage für diesen Artikel sammelte eine Vielzahl von Informationen aus öffentlich zugänglichen Materialien, darunter verschiedene Forschungsarbeiten, Fachzeitschriften, von Unternehmen veröffentlichte Benchmarks usw. Es gibt zwar andere Möglichkeiten, Informationen über Unternehmen und Start-ups zu erhalten (auch solche in stillen Phasen), in diesem Artikel werden diese Informationen zum Zeitpunkt dieser Umfrage jedoch weggelassen und die Daten werden in die Umfrage einbezogen, wenn sie veröffentlicht werden. Die wichtigsten Kennzahlen dieser öffentlichen Daten sind in der folgenden Tabelle dargestellt, die die aktuelle Spitzenleistung des Prozessors im Vergleich zum Stromverbrauch widerspiegelt (Stand: Juli 2022).

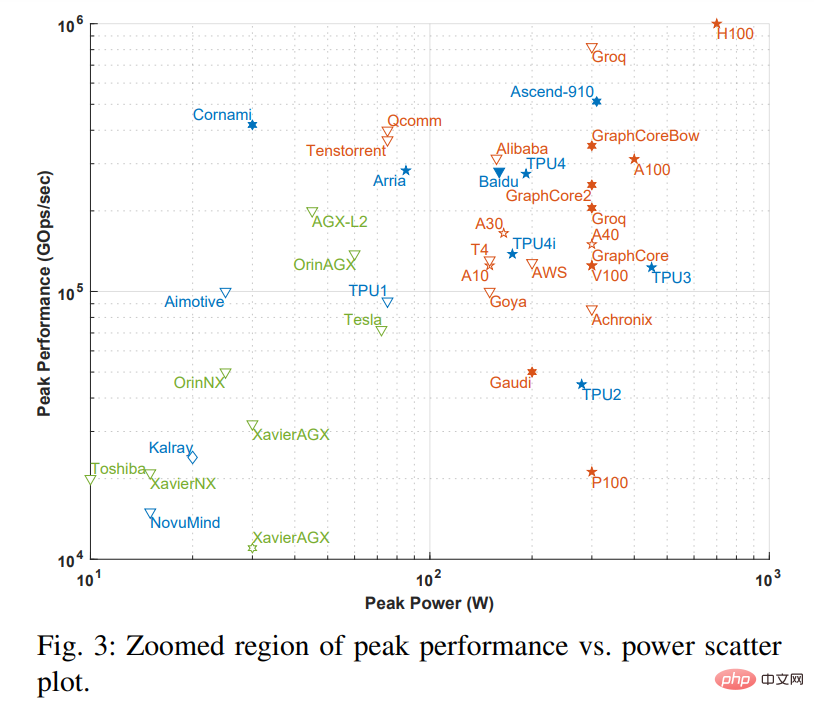

Hinweis: Das gepunktete Kästchen in Abbildung 2 entspricht Abbildung 3 unten. Abbildung 3 ist eine vergrößerte Version des gepunkteten Kästchens.

Die X-Achse in der Abbildung stellt die Spitzenleistung dar, und die Y-Achse stellt die Spitzen-Gigabit-Operationen pro Sekunde (GOps/s) dar, beide im logarithmischen Maßstab. Die Berechnungsgenauigkeit der Rechenleistung wird durch unterschiedliche Geometrien dargestellt, die von int1 bis int32 und von fp16 bis fp64 reichen. Es werden zwei Arten der Genauigkeit angezeigt. Die linke Seite stellt die Genauigkeit von Multiplikationsoperationen dar und die rechte Seite stellt die Genauigkeit von Akkumulations-/Additionsoperationen dar (z. B. stellt fp16.32 die fp16-Multiplikation und die fp32-Akkumulation/Addition dar). Verwenden Sie Farben und Formen, um zwischen verschiedenen Systemtypen und Spitzenleistungen zu unterscheiden. Blau steht für einen einzelnen Chip; Orange steht für eine Karte; Grün steht für ein Gesamtsystem (Einzelknoten-Desktop- und Serversysteme). Diese Untersuchung ist auf Systeme mit einem Motherboard und einem Speicher beschränkt. Die offenen Geometrien in der Abbildung stellen die Spitzenleistung von Beschleunigern dar, die nur Inferenz durchführen, während die Volumengeometrien die Leistung von Beschleunigern darstellen, die sowohl Training als auch Inferenz durchführen.

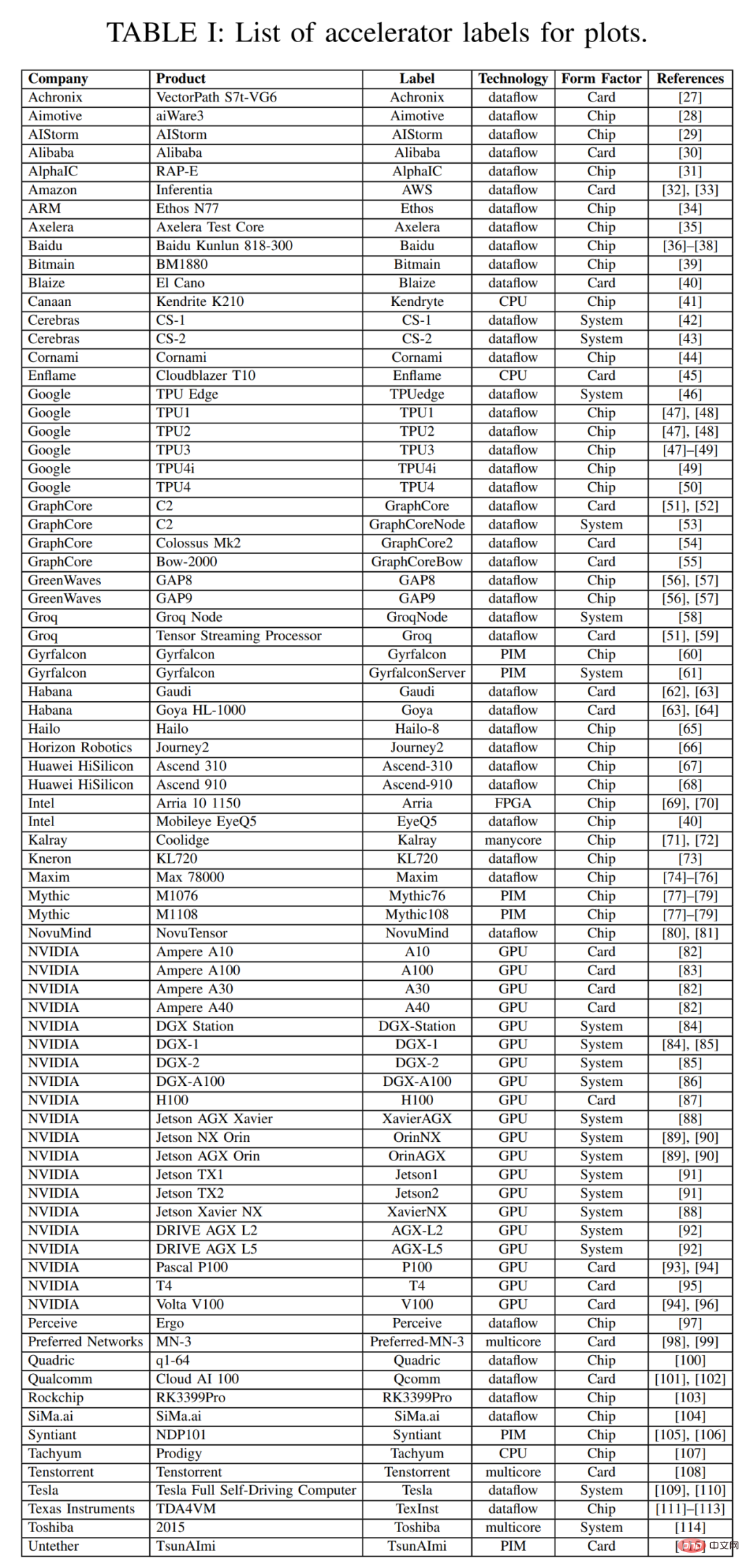

In dieser Umfrage beginnt dieser Artikel mit einem Streudiagramm der Umfragedaten der letzten drei Jahre. Dieser Artikel fasst einige wichtige Metadaten für den Beschleuniger, die Karte und das Gesamtsystem in Tabelle 1 unten zusammen, einschließlich Beschriftungen für jeden Punkt in Abbildung 2, wobei viele Punkte aus der letztjährigen Umfrage stammen. Die meisten Spalten und Einträge in Tabelle 1 sind korrekt und klar. Bei zwei Technologieelementen ist dies jedoch wahrscheinlich nicht der Fall: Dataflow und PIM. Prozessoren vom Typ „Datenfluss“ sind Prozessoren, die für die Inferenz und das Training neuronaler Netzwerke angepasst sind. Da neuronale Netzwerktrainings- und Inferenzberechnungen vollständig deterministisch aufgebaut sind, eignen sie sich für die Datenflussverarbeitung, bei der Berechnungen, Speicherzugriffe und Inter-ALU-Kommunikationen explizit/statisch programmiert oder platziert und an die Rechenhardware weitergeleitet werden. Processor-in-Memory-Beschleuniger (PIM) integrieren Verarbeitungselemente mit Speichertechnologie. Zu diesen PIM-Beschleunigern gehören solche, die auf analoger Computertechnologie basieren und Flash-Speicherschaltungen mit integrierten analogen Multiplikations-Add-Funktionen erweitern. Weitere Einzelheiten zu dieser innovativen Technologie finden Sie in der Dokumentation der Mythic- und Gyrfalcon-Beschleuniger.

In diesem Artikel werden Beschleuniger sinnvoll nach ihren erwarteten Anwendungen kategorisiert. Abbildung 1 verwendet Ellipsen, um fünf Arten von Beschleunigern entsprechend ihrer Leistung und ihrem Stromverbrauch zu identifizieren: sehr geringer Stromverbrauch, sehr kleiner Sensor, eingebettete Kameras , kleine Drohnen und Roboter; Fahrerassistenzsysteme, autonomes Fahren und autonome Roboter;

Die Leistung, Funktionen und andere Indikatoren der meisten Beschleuniger haben sich nicht geändert. Relevante Informationen finden Sie in den Veröffentlichungen der letzten zwei Jahre. Im Folgenden finden Sie Beschleuniger, die in früheren Artikeln nicht enthalten waren.

Das niederländische Embedded-System-Startup Acelera behauptet, dass der von ihnen hergestellte Embedded-Testchip über digitale und analoge Designfähigkeiten verfügt, und dieser Testchip soll den Umfang der digitalen Designfähigkeiten testen. Sie hoffen, in zukünftigen Arbeiten analoge (und möglicherweise Flash-)Designelemente hinzufügen zu können.

Maxim Integrated hat ein System-on-Chip (SoC) namens MAX78000 für Anwendungen mit extrem geringem Stromverbrauch herausgebracht. Es umfasst ARM-CPU-Kerne, RISC-V-CPU-Kerne und KI-Beschleuniger. Der ARM-Kern wird für schnelles Prototyping und Code-Wiederverwendung verwendet, während der RISC-V-Kern für niedrigsten Stromverbrauch optimiert ist. Der KI-Beschleuniger verfügt über 64 parallele Prozessoren, die 1-Bit-, 2-Bit-, 4-Bit- und 8-Bit-Integer-Operationen unterstützen. Der SoC arbeitet mit einer maximalen Leistung von 30 mW und eignet sich daher für batteriebetriebene Anwendungen mit geringer Latenz.

Tachyum hat kürzlich einen All-in-One-Prozessor namens Prodigy herausgebracht, der die Funktionen von CPU und GPU integriert. Er ist für HPC- und Machine-Learning-Anwendungen konzipiert und läuft mit einem Frequenz von 5,7 GHz.

NVIDIA hat im März 2022 seine GPU der nächsten Generation namens Hopper (H100) veröffentlicht. Hopper integriert mehr symmetrische Multiprozessoren (SIMD- und Tensor-Kerne), 50 % mehr Speicherbandbreite und SXM-Mezzanine-Karteninstanzen mit 700 W Leistung. (Die Leistung der PCIe-Karte beträgt 450 W)

In den letzten Jahren hat NVIDIA eine Reihe von Systemplattformen für GPUs mit Ampere-Architektur herausgebracht, die in der Automobil-, Robotik- und anderen eingebetteten Anwendungen eingesetzt werden. Für Automobilanwendungen fügt die DRIVE AGX-Plattform zwei neue Systeme hinzu: DRIVE AGX L2 ermöglicht autonomes Fahren der Stufe 2 im 45-W-Leistungsbereich und DRIVE AGX L5 ermöglicht autonomes Fahren der Stufe 5 im 800-W-Leistungsbereich. Jetson AGX Orin und Jetson NX Orin verwenden auch GPUs mit Ampere-Architektur für Robotik, Fabrikautomation und mehr und haben eine maximale Spitzenleistung von 60 W und 25 W.

Graphcore bringt seinen Beschleunigerchip CG200 der zweiten Generation auf den Markt, der auf einer PCIe-Karte eingesetzt wird und eine Spitzenleistung von etwa 300 W hat. Im vergangenen Jahr brachte Graphcore außerdem den Bow-Beschleuniger auf den Markt, den ersten Wafer-to-Wafer-Prozessor, der in Zusammenarbeit mit TSMC entwickelt wurde. Der Beschleuniger selbst ist derselbe wie beim oben erwähnten CG200, ist jedoch mit einem zweiten Chip gekoppelt, der die Leistungs- und Taktverteilung über den gesamten CG200-Chip erheblich verbessert. Dies entspricht einer Leistungssteigerung von 40 % und einer Leistungssteigerung pro Watt von 16 %.

Im Juni 2021 gab Google Einzelheiten zu seinem reinen Inferenz-TPU4i-Beschleuniger der vierten Generation bekannt. Fast ein Jahr später hat Google Details zu seinem Trainingsbeschleuniger der 4. Generation, TPUv4, veröffentlicht. Obwohl die offizielle Ankündigung nur wenige Details enthält, werden Spitzenleistung und damit verbundene Leistungsdaten genannt. Wie frühere TPU-Versionen ist TPU4 über Google Compute Cloud verfügbar und wird für interne Vorgänge verwendet.

Das Folgende ist eine Einführung in Beschleuniger, die nicht in Abbildung 2 angezeigt werden. Jede Version veröffentlicht einige Benchmark-Ergebnisse, aber einigen fehlt die Spitzenleistung und andere veröffentlichen keine Spitzenleistung, wie folgt.

SambaNova veröffentlichte letztes Jahr einige Benchmark-Ergebnisse der rekonfigurierbaren KI-Beschleunigertechnologie und veröffentlichte in Zusammenarbeit mit dem Argonne National Laboratory keine Details Leistung oder Stromverbrauch ihrer Lösung aus öffentlich zugänglichen Quellen.

Im Mai dieses Jahres kündigten Intel Habana Labs die Einführung des Goya-Inferenzbeschleunigers und des Gaudi-Trainingsbeschleunigers der zweiten Generation mit den Namen Greco bzw. Gaudi2 an. Beide schneiden um ein Vielfaches besser ab als frühere Versionen. Die Greco ist eine 75-W-PCIe-Karte mit einfacher Breite, während die Gaudi2 ebenfalls eine 650-W-PCIe-Karte mit doppelter Breite ist (wahrscheinlich in einem PCIe 5.0-Steckplatz). Habana veröffentlichte einige Benchmark-Vergleiche von Gaudi2 mit der Nvidia A100-GPU, gab jedoch keine Spitzenleistungswerte für einen der beiden Beschleuniger bekannt.

Esperanto hat einige Demo-Chips für Samsung und andere Partner zur Evaluierung produziert. Der Chip ist ein 1000-Kern-RISC-V-Prozessor mit einem KI-Tensorbeschleuniger pro Kern. Esperanto hat einige Leistungsdaten veröffentlicht, die Spitzenleistung oder Spitzenleistung werden jedoch nicht bekannt gegeben.

Am Tesla AI Day stellte Tesla seinen maßgeschneiderten Dojo-Beschleuniger und einige Details des Systems vor. Ihre Chips haben eine Spitzenleistung von 22,6 TF FP32, der Spitzenstromverbrauch für jeden Chip wurde jedoch nicht bekannt gegeben. Möglicherweise werden diese Details zu einem späteren Zeitpunkt bekannt gegeben.

Letztes Jahr brachte Centaur Technology eine x86-CPU mit integriertem KI-Beschleuniger auf den Markt, die über eine 4096 Byte breite SIMD-Einheit verfügt und eine sehr wettbewerbsfähige Leistung bietet. Doch die Muttergesellschaft von Centaur, VIA Technologies, scheint die Entwicklung von CNS-Prozessoren eingestellt zu haben, nachdem sie ihr in den USA ansässiges Prozessorentwicklungsteam an Intel verkauft hat.

Einige Beobachtungen und Trends

In Abbildung 2 gibt es mehrere erwähnenswerte Beobachtungen, die Details sind wie folgt.

Int8 bleibt die standardmäßige numerische Genauigkeit für eingebettete, autonome und Rechenzentrums-Inferenzanwendungen. Diese Genauigkeit reicht für die meisten KI/ML-Anwendungen aus, die rationale Zahlen verwenden. Einige Beschleuniger verwenden auch fp16 oder bf16. Das Modelltraining verwendet eine Ganzzahldarstellung.

Neben dem Beschleuniger für maschinelles Lernen wurden in dem extrem stromsparenden Chip keine weiteren Zusatzfunktionen gefunden. In den Kategorien Ultra-Low-Power-Chip und Embedded werden häufig System-on-Chip-Lösungen (SoC) auf den Markt gebracht, die häufig CPU-Kerne mit geringem Stromverbrauch, Audio- und Video-Analog-Digital-Wandler (ADCs) und kryptografische Engines umfassen , Netzwerkschnittstellen usw. . Diese zusätzlichen Funktionen des SoC verändern die Spitzenleistungsmetriken nicht, haben aber einen direkten Einfluss auf die vom Chip gemeldete Spitzenleistung, was beim Vergleich wichtig ist.

Am eingebetteten Teil hat sich nicht viel geändert, was bedeutet, dass die Rechenleistung und Spitzenleistung ausreichen, um die Anwendungsanforderungen in diesem Bereich zu erfüllen.

Mehrere Unternehmen, darunter Texas Instruments, haben in den letzten Jahren KI-Beschleuniger herausgebracht. Und NVIDIA hat, wie bereits erwähnt, auch einige leistungsstärkere Systeme für Automobil- und Robotikanwendungen herausgebracht. Im Rechenzentrum wird die PCIe v5-Spezifikation mit Spannung erwartet, um die 300-W-Leistungsgrenze von PCIe v4 zu durchbrechen.

Schließlich liefern High-End-Trainingssysteme nicht nur beeindruckende Leistungszahlen, sondern diese Unternehmen bringen auch hoch skalierbare Verbindungstechnologie auf den Markt, um Tausende von Karten miteinander zu verbinden. Dies ist besonders wichtig für Datenflussbeschleuniger wie Cerebras, GraphCore, Groq, Tesla Dojo und SambaNova, die über explizite/statische Programmierung oder Place-and-Route auf der Rechenhardware programmiert werden. Auf diese Weise können diese Beschleuniger in sehr große Modelle wie Transformatoren eingebaut werden.

Weitere Informationen finden Sie im Originalartikel.

Das obige ist der detaillierte Inhalt vonDas MIT fasst die letzten drei Jahre zusammen und veröffentlicht einen Übersichtsartikel zu KI-Beschleunigern. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!

Heiße KI -Werkzeuge

Undresser.AI Undress

KI-gestützte App zum Erstellen realistischer Aktfotos

AI Clothes Remover

Online-KI-Tool zum Entfernen von Kleidung aus Fotos.

Undress AI Tool

Ausziehbilder kostenlos

Clothoff.io

KI-Kleiderentferner

AI Hentai Generator

Erstellen Sie kostenlos Ai Hentai.

Heißer Artikel

Heiße Werkzeuge

Notepad++7.3.1

Einfach zu bedienender und kostenloser Code-Editor

SublimeText3 chinesische Version

Chinesische Version, sehr einfach zu bedienen

Senden Sie Studio 13.0.1

Leistungsstarke integrierte PHP-Entwicklungsumgebung

Dreamweaver CS6

Visuelle Webentwicklungstools

SublimeText3 Mac-Version

Codebearbeitungssoftware auf Gottesniveau (SublimeText3)

Heiße Themen

1376

1376

52

52

Bytedance Cutting führt SVIP-Supermitgliedschaft ein: 499 Yuan für ein fortlaufendes Jahresabonnement, das eine Vielzahl von KI-Funktionen bietet

Jun 28, 2024 am 03:51 AM

Bytedance Cutting führt SVIP-Supermitgliedschaft ein: 499 Yuan für ein fortlaufendes Jahresabonnement, das eine Vielzahl von KI-Funktionen bietet

Jun 28, 2024 am 03:51 AM

Diese Seite berichtete am 27. Juni, dass Jianying eine von FaceMeng Technology, einer Tochtergesellschaft von ByteDance, entwickelte Videobearbeitungssoftware ist, die auf der Douyin-Plattform basiert und grundsätzlich kurze Videoinhalte für Benutzer der Plattform produziert Windows, MacOS und andere Betriebssysteme. Jianying kündigte offiziell die Aktualisierung seines Mitgliedschaftssystems an und führte ein neues SVIP ein, das eine Vielzahl von KI-Schwarztechnologien umfasst, wie z. B. intelligente Übersetzung, intelligente Hervorhebung, intelligente Verpackung, digitale menschliche Synthese usw. Preislich beträgt die monatliche Gebühr für das Clipping von SVIP 79 Yuan, die Jahresgebühr 599 Yuan (Hinweis auf dieser Website: entspricht 49,9 Yuan pro Monat), das fortlaufende Monatsabonnement beträgt 59 Yuan pro Monat und das fortlaufende Jahresabonnement beträgt 499 Yuan pro Jahr (entspricht 41,6 Yuan pro Monat). Darüber hinaus erklärte der Cut-Beamte auch, dass diejenigen, die den ursprünglichen VIP abonniert haben, das Benutzererlebnis verbessern sollen

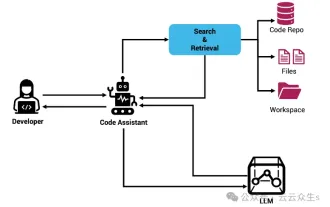

Kontexterweiterter KI-Codierungsassistent mit Rag und Sem-Rag

Jun 10, 2024 am 11:08 AM

Kontexterweiterter KI-Codierungsassistent mit Rag und Sem-Rag

Jun 10, 2024 am 11:08 AM

Verbessern Sie die Produktivität, Effizienz und Genauigkeit der Entwickler, indem Sie eine abrufgestützte Generierung und ein semantisches Gedächtnis in KI-Codierungsassistenten integrieren. Übersetzt aus EnhancingAICodingAssistantswithContextUsingRAGandSEM-RAG, Autor JanakiramMSV. Obwohl grundlegende KI-Programmierassistenten natürlich hilfreich sind, können sie oft nicht die relevantesten und korrektesten Codevorschläge liefern, da sie auf einem allgemeinen Verständnis der Softwaresprache und den gängigsten Mustern beim Schreiben von Software basieren. Der von diesen Coding-Assistenten generierte Code eignet sich zur Lösung der von ihnen zu lösenden Probleme, entspricht jedoch häufig nicht den Coding-Standards, -Konventionen und -Stilen der einzelnen Teams. Dabei entstehen häufig Vorschläge, die geändert oder verfeinert werden müssen, damit der Code in die Anwendung übernommen wird

Sieben coole technische Interviewfragen für GenAI und LLM

Jun 07, 2024 am 10:06 AM

Sieben coole technische Interviewfragen für GenAI und LLM

Jun 07, 2024 am 10:06 AM

Um mehr über AIGC zu erfahren, besuchen Sie bitte: 51CTOAI.x Community https://www.51cto.com/aigc/Translator|Jingyan Reviewer|Chonglou unterscheidet sich von der traditionellen Fragendatenbank, die überall im Internet zu sehen ist erfordert einen Blick über den Tellerrand hinaus. Large Language Models (LLMs) gewinnen in den Bereichen Datenwissenschaft, generative künstliche Intelligenz (GenAI) und künstliche Intelligenz zunehmend an Bedeutung. Diese komplexen Algorithmen verbessern die menschlichen Fähigkeiten, treiben Effizienz und Innovation in vielen Branchen voran und werden zum Schlüssel für Unternehmen, um wettbewerbsfähig zu bleiben. LLM hat ein breites Anwendungsspektrum und kann in Bereichen wie der Verarbeitung natürlicher Sprache, der Textgenerierung, der Spracherkennung und Empfehlungssystemen eingesetzt werden. Durch das Lernen aus großen Datenmengen ist LLM in der Lage, Text zu generieren

Kann LLM durch Feinabstimmung wirklich neue Dinge lernen: Die Einführung neuen Wissens kann dazu führen, dass das Modell mehr Halluzinationen hervorruft

Jun 11, 2024 pm 03:57 PM

Kann LLM durch Feinabstimmung wirklich neue Dinge lernen: Die Einführung neuen Wissens kann dazu führen, dass das Modell mehr Halluzinationen hervorruft

Jun 11, 2024 pm 03:57 PM

Large Language Models (LLMs) werden auf riesigen Textdatenbanken trainiert und erwerben dort große Mengen an realem Wissen. Dieses Wissen wird in ihre Parameter eingebettet und kann dann bei Bedarf genutzt werden. Das Wissen über diese Modelle wird am Ende der Ausbildung „verdinglicht“. Am Ende des Vortrainings hört das Modell tatsächlich auf zu lernen. Richten Sie das Modell aus oder verfeinern Sie es, um zu erfahren, wie Sie dieses Wissen nutzen und natürlicher auf Benutzerfragen reagieren können. Aber manchmal reicht Modellwissen nicht aus, und obwohl das Modell über RAG auf externe Inhalte zugreifen kann, wird es als vorteilhaft angesehen, das Modell durch Feinabstimmung an neue Domänen anzupassen. Diese Feinabstimmung erfolgt mithilfe von Eingaben menschlicher Annotatoren oder anderer LLM-Kreationen, wobei das Modell auf zusätzliches Wissen aus der realen Welt trifft und dieses integriert

Um ein neues wissenschaftliches und komplexes Frage-Antwort-Benchmark- und Bewertungssystem für große Modelle bereitzustellen, haben UNSW, Argonne, die University of Chicago und andere Institutionen gemeinsam das SciQAG-Framework eingeführt

Jul 25, 2024 am 06:42 AM

Um ein neues wissenschaftliches und komplexes Frage-Antwort-Benchmark- und Bewertungssystem für große Modelle bereitzustellen, haben UNSW, Argonne, die University of Chicago und andere Institutionen gemeinsam das SciQAG-Framework eingeführt

Jul 25, 2024 am 06:42 AM

Herausgeber | Der Frage-Antwort-Datensatz (QA) von ScienceAI spielt eine entscheidende Rolle bei der Förderung der Forschung zur Verarbeitung natürlicher Sprache (NLP). Hochwertige QS-Datensätze können nicht nur zur Feinabstimmung von Modellen verwendet werden, sondern auch effektiv die Fähigkeiten großer Sprachmodelle (LLMs) bewerten, insbesondere die Fähigkeit, wissenschaftliche Erkenntnisse zu verstehen und zu begründen. Obwohl es derzeit viele wissenschaftliche QS-Datensätze aus den Bereichen Medizin, Chemie, Biologie und anderen Bereichen gibt, weisen diese Datensätze immer noch einige Mängel auf. Erstens ist das Datenformular relativ einfach, die meisten davon sind Multiple-Choice-Fragen. Sie sind leicht auszuwerten, schränken jedoch den Antwortauswahlbereich des Modells ein und können die Fähigkeit des Modells zur Beantwortung wissenschaftlicher Fragen nicht vollständig testen. Im Gegensatz dazu offene Fragen und Antworten

Fünf Schulen des maschinellen Lernens, die Sie nicht kennen

Jun 05, 2024 pm 08:51 PM

Fünf Schulen des maschinellen Lernens, die Sie nicht kennen

Jun 05, 2024 pm 08:51 PM

Maschinelles Lernen ist ein wichtiger Zweig der künstlichen Intelligenz, der Computern die Möglichkeit gibt, aus Daten zu lernen und ihre Fähigkeiten zu verbessern, ohne explizit programmiert zu werden. Maschinelles Lernen hat ein breites Anwendungsspektrum in verschiedenen Bereichen, von der Bilderkennung und der Verarbeitung natürlicher Sprache bis hin zu Empfehlungssystemen und Betrugserkennung, und es verändert unsere Lebensweise. Im Bereich des maschinellen Lernens gibt es viele verschiedene Methoden und Theorien, von denen die fünf einflussreichsten Methoden als „Fünf Schulen des maschinellen Lernens“ bezeichnet werden. Die fünf Hauptschulen sind die symbolische Schule, die konnektionistische Schule, die evolutionäre Schule, die Bayes'sche Schule und die Analogieschule. 1. Der Symbolismus, auch Symbolismus genannt, betont die Verwendung von Symbolen zum logischen Denken und zum Ausdruck von Wissen. Diese Denkrichtung glaubt, dass Lernen ein Prozess der umgekehrten Schlussfolgerung durch das Vorhandene ist

SOTA Performance, eine multimodale KI-Methode zur Vorhersage der Protein-Ligand-Affinität in Xiamen, kombiniert erstmals molekulare Oberflächeninformationen

Jul 17, 2024 pm 06:37 PM

SOTA Performance, eine multimodale KI-Methode zur Vorhersage der Protein-Ligand-Affinität in Xiamen, kombiniert erstmals molekulare Oberflächeninformationen

Jul 17, 2024 pm 06:37 PM

Herausgeber |. KX Im Bereich der Arzneimittelforschung und -entwicklung ist die genaue und effektive Vorhersage der Bindungsaffinität von Proteinen und Liganden für das Arzneimittelscreening und die Arzneimitteloptimierung von entscheidender Bedeutung. Aktuelle Studien berücksichtigen jedoch nicht die wichtige Rolle molekularer Oberflächeninformationen bei Protein-Ligand-Wechselwirkungen. Auf dieser Grundlage schlugen Forscher der Universität Xiamen ein neuartiges Framework zur multimodalen Merkmalsextraktion (MFE) vor, das erstmals Informationen über Proteinoberfläche, 3D-Struktur und -Sequenz kombiniert und einen Kreuzaufmerksamkeitsmechanismus verwendet, um verschiedene Modalitäten zu vergleichen Ausrichtung. Experimentelle Ergebnisse zeigen, dass diese Methode bei der Vorhersage von Protein-Ligand-Bindungsaffinitäten Spitzenleistungen erbringt. Darüber hinaus belegen Ablationsstudien die Wirksamkeit und Notwendigkeit der Proteinoberflächeninformation und der multimodalen Merkmalsausrichtung innerhalb dieses Rahmens. Verwandte Forschungen beginnen mit „S

GlobalFoundries erschließt Märkte wie KI und erwirbt die Galliumnitrid-Technologie von Tagore Technology und zugehörige Teams

Jul 15, 2024 pm 12:21 PM

GlobalFoundries erschließt Märkte wie KI und erwirbt die Galliumnitrid-Technologie von Tagore Technology und zugehörige Teams

Jul 15, 2024 pm 12:21 PM

Laut Nachrichten dieser Website vom 5. Juli veröffentlichte GlobalFoundries am 1. Juli dieses Jahres eine Pressemitteilung, in der die Übernahme der Power-Galliumnitrid (GaN)-Technologie und des Portfolios an geistigem Eigentum von Tagore Technology angekündigt wurde, in der Hoffnung, seinen Marktanteil in den Bereichen Automobile und Internet auszubauen Anwendungsbereiche für Rechenzentren mit künstlicher Intelligenz, um höhere Effizienz und bessere Leistung zu erforschen. Da sich Technologien wie generative künstliche Intelligenz (GenerativeAI) in der digitalen Welt weiterentwickeln, ist Galliumnitrid (GaN) zu einer Schlüssellösung für nachhaltiges und effizientes Energiemanagement, insbesondere in Rechenzentren, geworden. Auf dieser Website wurde die offizielle Ankündigung zitiert, dass sich das Ingenieurteam von Tagore Technology im Rahmen dieser Übernahme mit GF zusammenschließen wird, um die Galliumnitrid-Technologie weiterzuentwickeln. G