自己动手写CPU之第五阶段(2)OpenMIPS对数据相关问题的解决

将陆续上传本人写的新书《自己动手写CPU》(尚未出版),今天是第16篇,我尽量每周四篇 5.2OpenMIPS 对数据相关问题的解决措施 OpenMIPS 处理器采用数据前推的方法来解决流水线数据相关问题。通过补充完善图 4-4 原始的数据流图,添加部分信号使得可以完成数

将陆续上传本人写的新书《自己动手写CPU》(尚未出版),今天是第16篇,我尽量每周四篇

5.2 OpenMIPS对数据相关问题的解决措施

OpenMIPS处理器采用数据前推的方法来解决流水线数据相关问题。通过补充完善图4-4原始的数据流图,添加部分信号使得可以完成数据前推的工作,如图5-7所示。主要是将执行阶段的结果、访存阶段的结果前推到译码阶段,参与译码阶段选择运算源操作数的过程。

图5-8给出了为实现数据前推而对OpenMIPS系统结构所做的修改。有两个方面。

(1)将处于流水线执行阶段的指令的运算结果,包括:是否要写目的寄存器wreg_o、要写的目的寄存器地址wd_o、要写入目的寄存器的数据wdata_o等信息送到译码阶段,如图5-8中虚线所示。

(2)将处于流水线访存阶段的指令的运算结果,包括:是否要写目的寄存器wreg_o、要写的目的寄存器地址wd_o、要写入目的寄存器的数据wdata_o等信息送到译码阶段。

为此,译码阶段的ID模块要增加如表5-1所示的接口。

译码阶段的ID模块会依据送入的信息,进行综合判断,解决数据相关,给出最后要参与运算的操作数。ID模块的代码要做如下修改,其中主要修改部分使用加粗、斜体表示。修改后的代码位于本书光盘的Code\Chapter5_1目录下的id.v文件。

module id(

......

//处于执行阶段的指令的运算结果

input wire ex_wreg_i,

input wire[`RegBus] ex_wdata_i,

input wire[`RegAddrBus] ex_wd_i,

//处于访存阶段的指令的运算结果

input wire mem_wreg_i,

input wire[`RegBus] mem_wdata_i,

input wire[`RegAddrBus] mem_wd_i,

......

//送到执行阶段的源操作数1、源操作数2

output reg[`RegBus] reg1_o,

output reg[`RegBus] reg2_o,

......

);

......

//给reg1_o赋值的过程增加了两种情况:

//1、如果Regfile模块读端口1要读取的寄存器就是执行阶段要写的目的寄存器,

// 那么直接把执行阶段的结果ex_wdata_i作为reg1_o的值;

//2、如果Regfile模块读端口1要读取的寄存器就是访存阶段要写的目的寄存器,

// 那么直接把访存阶段的结果mem_wdata_i作为reg1_o的值;

always @ (*) begin

if(rst == `RstEnable) begin

reg1_o <br>

<p> 除了修改译码阶段<span>ID</span><span>模块的代码,还要修改顶层模块</span><span>OpenMIPS</span><span>对应的代码,在其中增加图</span><span>5-8</span><span>所示的连接关系。具体修改过程不在书中列出,读者可以参考本书附带光盘的</span><span>Code\</span>Chapter5_1目录下的<span>openmips.v</span><span>文件。(代码会在稍后上传)</span></p>

<h2>5.3 <span>测试数据相关问题解决效果</span>

</h2>

<p> 测试程序如下,其中存在<span>5.1</span><span>节讨论的</span><span>RAW</span><span>相关的三种情况,源文件是本书附带光盘</span><span>Code\</span>Chapter5_1\AsmTest<span>目录下的</span><span>inst_rom.S</span><span>文件。</span></p>

<pre class="brush:php;toolbar:false">.org 0x0

.global _start

.set noat

_start:

ori $1,$0,0x1100 # $1 = $0 | 0x1100 = 0x1100

ori $1,$1,0x0020 # $1 = $1 | 0x0020 = 0x1120

ori $1,$1,0x4400 # $1 = $1 | 0x4400 = 0x5520

ori $1,$1,0x0044 # $1 = $1 | 0x0044 = 0x5564指令的注释给出了预期执行效果。将上述inst_rom.S文件,与第4章实现的Bin2Mem.exe、Makefile、ram.ld这三个文件拷贝到Ubuntu虚拟机中的同一个目录下,打开终端,使用cd命令进入该目录,然后输入make all,即可得到能够用于ModelSim仿真的inst_rom.data文件。

在ModelSim中新建一个工程,添加本书附带光盘Code\Chapter5_1目录下的所有.v文件,然后可以编译。再复制上面得到的inst_rom.data文件到ModelSim工程的目录下,就可以进行仿真了。ModelSim中新建工程、仿真的详细步骤可以参考第2章。

运行仿真,观察寄存器$1值的变化,如图5-9所示,$1的变化符合预期,所以修改后的OpenMIPS正确解决了数据相关问题。

下一步将实现逻辑、移位、空指令,敬请关注!

Hot AI Tools

Undresser.AI Undress

AI-powered app for creating realistic nude photos

AI Clothes Remover

Online AI tool for removing clothes from photos.

Undress AI Tool

Undress images for free

Clothoff.io

AI clothes remover

AI Hentai Generator

Generate AI Hentai for free.

Hot Article

Hot Tools

Notepad++7.3.1

Easy-to-use and free code editor

SublimeText3 Chinese version

Chinese version, very easy to use

Zend Studio 13.0.1

Powerful PHP integrated development environment

Dreamweaver CS6

Visual web development tools

SublimeText3 Mac version

God-level code editing software (SublimeText3)

Hot Topics

1382

1382

52

52

Open source! Beyond ZoeDepth! DepthFM: Fast and accurate monocular depth estimation!

Apr 03, 2024 pm 12:04 PM

Open source! Beyond ZoeDepth! DepthFM: Fast and accurate monocular depth estimation!

Apr 03, 2024 pm 12:04 PM

0.What does this article do? We propose DepthFM: a versatile and fast state-of-the-art generative monocular depth estimation model. In addition to traditional depth estimation tasks, DepthFM also demonstrates state-of-the-art capabilities in downstream tasks such as depth inpainting. DepthFM is efficient and can synthesize depth maps within a few inference steps. Let’s read about this work together ~ 1. Paper information title: DepthFM: FastMonocularDepthEstimationwithFlowMatching Author: MingGui, JohannesS.Fischer, UlrichPrestel, PingchuanMa, Dmytr

The operation process of WIN10 service host occupying too much CPU

Mar 27, 2024 pm 02:41 PM

The operation process of WIN10 service host occupying too much CPU

Mar 27, 2024 pm 02:41 PM

1. First, we right-click the blank space of the taskbar and select the [Task Manager] option, or right-click the start logo, and then select the [Task Manager] option. 2. In the opened Task Manager interface, we click the [Services] tab on the far right. 3. In the opened [Service] tab, click the [Open Service] option below. 4. In the [Services] window that opens, right-click the [InternetConnectionSharing(ICS)] service, and then select the [Properties] option. 5. In the properties window that opens, change [Open with] to [Disabled], click [Apply] and then click [OK]. 6. Click the start logo, then click the shutdown button, select [Restart], and complete the computer restart.

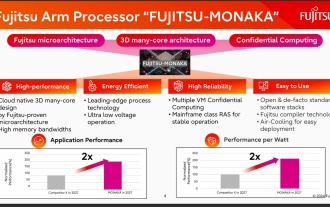

144-core, 3D-stacked SRAM: Fujitsu details next-generation data center processor MONAKA

Jul 29, 2024 am 11:40 AM

144-core, 3D-stacked SRAM: Fujitsu details next-generation data center processor MONAKA

Jul 29, 2024 am 11:40 AM

According to news from this website on July 28, foreign media TechRader reported that Fujitsu introduced in detail the FUJITSU-MONAKA (hereinafter referred to as MONAKA) processor planned to be shipped in 2027. MONAKACPU is based on the "cloud native 3D many-core" architecture and adopts the Arm instruction set. It is oriented to the data center, edge and telecommunications fields. It is suitable for AI computing and can realize mainframe-level RAS1. Fujitsu said that MONAKA will achieve a leap in energy efficiency and performance: thanks to technologies such as ultra-low voltage (ULV) technology, the CPU can achieve 2 times the energy efficiency of competing products in 2027, and cooling does not require water cooling; in addition, the application performance of the processor It can also reach twice as much as your opponent. In terms of instructions, MONAKA is equipped with vector

Leak reveals key specs of Intel Arrow Lake-U, -H, -HX and -S

Jun 15, 2024 pm 09:49 PM

Leak reveals key specs of Intel Arrow Lake-U, -H, -HX and -S

Jun 15, 2024 pm 09:49 PM

IntelArrowLakeisexpectedtobebasedonthesameprocessorarchitectureasLunarLake,meaningthatIntel'sbrandnewLionCoveperformancecoreswillbecombinedwiththeeconomicalSkymontefficiencycores.WhileLunarLakeisonlyavailableasava

AM4 refuses to die, news says AMD will launch Ryzen 9 5900XT/7 5800XT: clocked at up to 4.8GHz

Jun 05, 2024 pm 09:43 PM

AM4 refuses to die, news says AMD will launch Ryzen 9 5900XT/7 5800XT: clocked at up to 4.8GHz

Jun 05, 2024 pm 09:43 PM

According to news from this website on June 1st, the source @CodeCommando tweeted today, sharing some screenshots of AMD’s upcoming presentation documents at the Computex2024 event. The content of the tweet was “AM4 will never die”, and the accompanying picture showed two new Ryzen5000XT series processors. The screenshots show the following two products: Ryzen 95900 Ryzen75800XT It is a faster variant of AMD's existing Ryzen75800X processor. Both processors are clocked up to 4.8G

Google is ecstatic: JAX performance surpasses Pytorch and TensorFlow! It may become the fastest choice for GPU inference training

Apr 01, 2024 pm 07:46 PM

Google is ecstatic: JAX performance surpasses Pytorch and TensorFlow! It may become the fastest choice for GPU inference training

Apr 01, 2024 pm 07:46 PM

The performance of JAX, promoted by Google, has surpassed that of Pytorch and TensorFlow in recent benchmark tests, ranking first in 7 indicators. And the test was not done on the TPU with the best JAX performance. Although among developers, Pytorch is still more popular than Tensorflow. But in the future, perhaps more large models will be trained and run based on the JAX platform. Models Recently, the Keras team benchmarked three backends (TensorFlow, JAX, PyTorch) with the native PyTorch implementation and Keras2 with TensorFlow. First, they select a set of mainstream

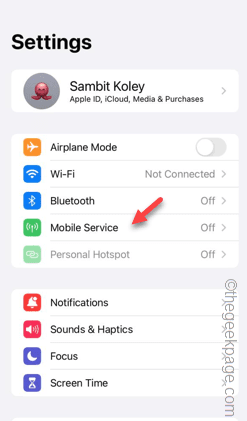

Slow Cellular Data Internet Speeds on iPhone: Fixes

May 03, 2024 pm 09:01 PM

Slow Cellular Data Internet Speeds on iPhone: Fixes

May 03, 2024 pm 09:01 PM

Facing lag, slow mobile data connection on iPhone? Typically, the strength of cellular internet on your phone depends on several factors such as region, cellular network type, roaming type, etc. There are some things you can do to get a faster, more reliable cellular Internet connection. Fix 1 – Force Restart iPhone Sometimes, force restarting your device just resets a lot of things, including the cellular connection. Step 1 – Just press the volume up key once and release. Next, press the Volume Down key and release it again. Step 2 – The next part of the process is to hold the button on the right side. Let the iPhone finish restarting. Enable cellular data and check network speed. Check again Fix 2 – Change data mode While 5G offers better network speeds, it works better when the signal is weaker

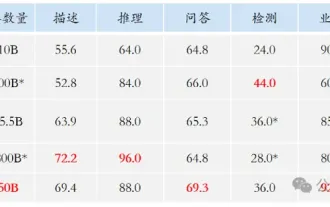

The vitality of super intelligence awakens! But with the arrival of self-updating AI, mothers no longer have to worry about data bottlenecks

Apr 29, 2024 pm 06:55 PM

The vitality of super intelligence awakens! But with the arrival of self-updating AI, mothers no longer have to worry about data bottlenecks

Apr 29, 2024 pm 06:55 PM

I cry to death. The world is madly building big models. The data on the Internet is not enough. It is not enough at all. The training model looks like "The Hunger Games", and AI researchers around the world are worrying about how to feed these data voracious eaters. This problem is particularly prominent in multi-modal tasks. At a time when nothing could be done, a start-up team from the Department of Renmin University of China used its own new model to become the first in China to make "model-generated data feed itself" a reality. Moreover, it is a two-pronged approach on the understanding side and the generation side. Both sides can generate high-quality, multi-modal new data and provide data feedback to the model itself. What is a model? Awaker 1.0, a large multi-modal model that just appeared on the Zhongguancun Forum. Who is the team? Sophon engine. Founded by Gao Yizhao, a doctoral student at Renmin University’s Hillhouse School of Artificial Intelligence.