cocos2dx多线程以及线程同步 与 cocos2dx内存管理与多线程问题

//-------------------------------------------------------------------- // // CCPoolManager // //-------------------------------------------------------------------- /////【diff - begin】- by layne////// CCPoolManager* CCPoolManager::shared

//--------------------------------------------------------------------

//

// CCPoolManager

//

//--------------------------------------------------------------------

/////【diff - begin】- by layne//////

CCPoolManager* CCPoolManager::sharedPoolManager()

{

if (s_pPoolManager == NULL)

{

s_pPoolManager = new CCPoolManager();

}

return s_pPoolManager;

}

void CCPoolManager::purgePoolManager()

{

CC_SAFE_DELETE(s_pPoolManager);

}

CCPoolManager::CCPoolManager()

{

// m_pReleasePoolStack = new CCArray();

// m_pReleasePoolStack->init();

// m_pCurReleasePool = 0;

m_pReleasePoolMultiStack = new CCDictionary();

}

CCPoolManager::~CCPoolManager()

{

// finalize();

// // we only release the last autorelease pool here

// m_pCurReleasePool = 0;

// m_pReleasePoolStack->removeObjectAtIndex(0);

//

// CC_SAFE_DELETE(m_pReleasePoolStack);

finalize();

CC_SAFE_DELETE(m_pReleasePoolMultiStack);

}

void CCPoolManager::finalize()

{

if(m_pReleasePoolMultiStack->count() > 0)

{

//CCAutoreleasePool* pReleasePool;

CCObject* pkey = NULL;

CCARRAY_FOREACH(m_pReleasePoolMultiStack->allKeys(), pkey)

{

if(!pkey)

break;

CCInteger *key = (CCInteger*)pkey;

CCArray *poolStack = (CCArray *)m_pReleasePoolMultiStack->objectForKey(key->getValue());

CCObject* pObj = NULL;

CCARRAY_FOREACH(poolStack, pObj)

{

if(!pObj)

break;

CCAutoreleasePool* pPool = (CCAutoreleasePool*)pObj;

pPool->clear();

}

}

}

}

void CCPoolManager::push()

{

// CCAutoreleasePool* pPool = new CCAutoreleasePool(); //ref = 1

// m_pCurReleasePool = pPool;

//

// m_pReleasePoolStack->addObject(pPool); //ref = 2

//

// pPool->release(); //ref = 1

pthread_mutex_lock(&m_mutex);

CCArray* pCurReleasePoolStack = getCurReleasePoolStack();

CCAutoreleasePool* pPool = new CCAutoreleasePool(); //ref = 1

pCurReleasePoolStack->addObject(pPool); //ref = 2

pPool->release(); //ref = 1

pthread_mutex_unlock(&m_mutex);

}

void CCPoolManager::pop()

{

// if (! m_pCurReleasePool)

// {

// return;

// }

//

// int nCount = m_pReleasePoolStack->count();

//

// m_pCurReleasePool->clear();

//

// if(nCount > 1)

// {

// m_pReleasePoolStack->removeObjectAtIndex(nCount-1);

//

// // if(nCount > 1)

// // {

// // m_pCurReleasePool = m_pReleasePoolStack->objectAtIndex(nCount - 2);

// // return;

// // }

// m_pCurReleasePool = (CCAutoreleasePool*)m_pReleasePoolStack->objectAtIndex(nCount - 2);

// }

//

// /*m_pCurReleasePool = NULL;*/

pthread_mutex_lock(&m_mutex);

CCArray* pCurReleasePoolStack = getCurReleasePoolStack();

CCAutoreleasePool* pCurReleasePool = getCurReleasePool();

if (pCurReleasePoolStack && pCurReleasePool)

{

int nCount = pCurReleasePoolStack->count();

pCurReleasePool->clear();

if(nCount > 1)

{

pCurReleasePoolStack->removeObject(pCurReleasePool);

}

}

pthread_mutex_unlock(&m_mutex);

}

void CCPoolManager::removeObject(CCObject* pObject)

{

// CCAssert(m_pCurReleasePool, "current auto release pool should not be null");

//

// m_pCurReleasePool->removeObject(pObject);

pthread_mutex_lock(&m_mutex);

CCAutoreleasePool* pCurReleasePool = getCurReleasePool();

CCAssert(pCurReleasePool, "current auto release pool should not be null");

pCurReleasePool->removeObject(pObject);

pthread_mutex_unlock(&m_mutex);

}

void CCPoolManager::addObject(CCObject* pObject)

{

// getCurReleasePool()->addObject(pObject);

pthread_mutex_lock(&m_mutex);

CCAutoreleasePool* pCurReleasePool = getCurReleasePool(true);

CCAssert(pCurReleasePool, "current auto release pool should not be null");

pCurReleasePool->addObject(pObject);

pthread_mutex_unlock(&m_mutex);

}

CCArray* CCPoolManager::getCurReleasePoolStack()

{

CCArray* pPoolStack = NULL;

pthread_t tid = pthread_self();

if(m_pReleasePoolMultiStack->count() > 0)

{

pPoolStack = (CCArray*)m_pReleasePoolMultiStack->objectForKey((int)tid);

}

if (!pPoolStack) {

pPoolStack = new CCArray();

m_pReleasePoolMultiStack->setObject(pPoolStack, (int)tid);

pPoolStack->release();

}

return pPoolStack;

}

CCAutoreleasePool* CCPoolManager::getCurReleasePool(bool autoCreate)

{

// if(!m_pCurReleasePool)

// {

// push();

// }

//

// CCAssert(m_pCurReleasePool, "current auto release pool should not be null");

//

// return m_pCurReleasePool;

CCAutoreleasePool* pReleasePool = NULL;

CCArray* pPoolStack = getCurReleasePoolStack();

if(pPoolStack->count() > 0)

{

pReleasePool = (CCAutoreleasePool*)pPoolStack->lastObject();

}

if (!pReleasePool && autoCreate) {

CCAutoreleasePool* pPool = new CCAutoreleasePool(); //ref = 1

pPoolStack->addObject(pPool); //ref = 2

pPool->release(); //ref = 1

pReleasePool = pPool;

}

return pReleasePool;

}

/////【diff - end】- by layne//////

Hot AI Tools

Undresser.AI Undress

AI-powered app for creating realistic nude photos

AI Clothes Remover

Online AI tool for removing clothes from photos.

Undress AI Tool

Undress images for free

Clothoff.io

AI clothes remover

AI Hentai Generator

Generate AI Hentai for free.

Hot Article

Hot Tools

Notepad++7.3.1

Easy-to-use and free code editor

SublimeText3 Chinese version

Chinese version, very easy to use

Zend Studio 13.0.1

Powerful PHP integrated development environment

Dreamweaver CS6

Visual web development tools

SublimeText3 Mac version

God-level code editing software (SublimeText3)

Hot Topics

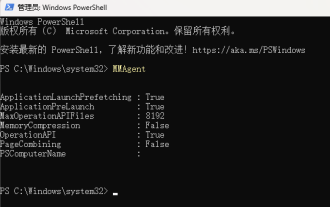

Large memory optimization, what should I do if the computer upgrades to 16g/32g memory speed and there is no change?

Jun 18, 2024 pm 06:51 PM

Large memory optimization, what should I do if the computer upgrades to 16g/32g memory speed and there is no change?

Jun 18, 2024 pm 06:51 PM

For mechanical hard drives or SATA solid-state drives, you will feel the increase in software running speed. If it is an NVME hard drive, you may not feel it. 1. Import the registry into the desktop and create a new text document, copy and paste the following content, save it as 1.reg, then right-click to merge and restart the computer. WindowsRegistryEditorVersion5.00[HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Control\SessionManager\MemoryManagement]"DisablePagingExecutive"=d

How to check memory usage on Xiaomi Mi 14Pro?

Mar 18, 2024 pm 02:19 PM

How to check memory usage on Xiaomi Mi 14Pro?

Mar 18, 2024 pm 02:19 PM

Recently, Xiaomi released a powerful high-end smartphone Xiaomi 14Pro, which not only has a stylish design, but also has internal and external black technology. The phone has top performance and excellent multitasking capabilities, allowing users to enjoy a fast and smooth mobile phone experience. However, performance will also be affected by memory. Many users want to know how to check the memory usage of Xiaomi 14Pro, so let’s take a look. How to check memory usage on Xiaomi Mi 14Pro? Introduction to how to check the memory usage of Xiaomi 14Pro. Open the [Application Management] button in [Settings] of Xiaomi 14Pro phone. To view the list of all installed apps, browse the list and find the app you want to view, click on it to enter the app details page. In the application details page

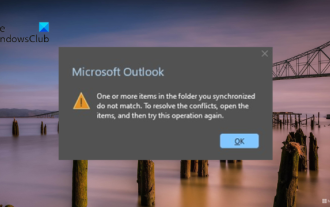

One or more items in the folder you synced do not match Outlook error

Mar 18, 2024 am 09:46 AM

One or more items in the folder you synced do not match Outlook error

Mar 18, 2024 am 09:46 AM

When you find that one or more items in your sync folder do not match the error message in Outlook, it may be because you updated or canceled meeting items. In this case, you will see an error message saying that your local version of the data conflicts with the remote copy. This situation usually happens in Outlook desktop application. One or more items in the folder you synced do not match. To resolve the conflict, open the projects and try the operation again. Fix One or more items in synced folders do not match Outlook error In Outlook desktop version, you may encounter issues when local calendar items conflict with the server copy. Fortunately, though, there are some simple ways to help

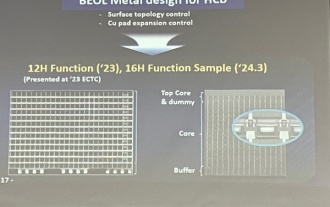

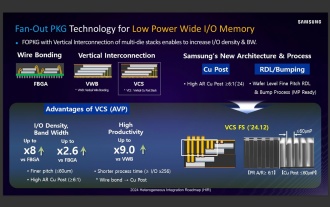

Samsung announced the completion of 16-layer hybrid bonding stacking process technology verification, which is expected to be widely used in HBM4 memory

Apr 07, 2024 pm 09:19 PM

Samsung announced the completion of 16-layer hybrid bonding stacking process technology verification, which is expected to be widely used in HBM4 memory

Apr 07, 2024 pm 09:19 PM

According to the report, Samsung Electronics executive Dae Woo Kim said that at the 2024 Korean Microelectronics and Packaging Society Annual Meeting, Samsung Electronics will complete the verification of the 16-layer hybrid bonding HBM memory technology. It is reported that this technology has passed technical verification. The report also stated that this technical verification will lay the foundation for the development of the memory market in the next few years. DaeWooKim said that Samsung Electronics has successfully manufactured a 16-layer stacked HBM3 memory based on hybrid bonding technology. The memory sample works normally. In the future, the 16-layer stacked hybrid bonding technology will be used for mass production of HBM4 memory. ▲Image source TheElec, same as below. Compared with the existing bonding process, hybrid bonding does not need to add bumps between DRAM memory layers, but directly connects the upper and lower layers copper to copper.

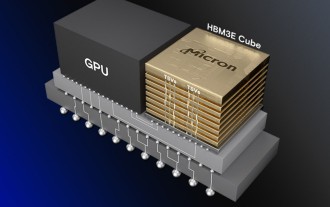

Micron: HBM memory consumes 3 times the wafer volume, and production capacity is basically booked for next year

Mar 22, 2024 pm 08:16 PM

Micron: HBM memory consumes 3 times the wafer volume, and production capacity is basically booked for next year

Mar 22, 2024 pm 08:16 PM

This site reported on March 21 that Micron held a conference call after releasing its quarterly financial report. At the conference, Micron CEO Sanjay Mehrotra said that compared to traditional memory, HBM consumes significantly more wafers. Micron said that when producing the same capacity at the same node, the current most advanced HBM3E memory consumes three times more wafers than standard DDR5, and it is expected that as performance improves and packaging complexity intensifies, in the future HBM4 This ratio will further increase. Referring to previous reports on this site, this high ratio is partly due to HBM’s low yield rate. HBM memory is stacked with multi-layer DRAM memory TSV connections. A problem with one layer means that the entire

Sources say Samsung Electronics and SK Hynix will commercialize stacked mobile memory after 2026

Sep 03, 2024 pm 02:15 PM

Sources say Samsung Electronics and SK Hynix will commercialize stacked mobile memory after 2026

Sep 03, 2024 pm 02:15 PM

According to news from this website on September 3, Korean media etnews reported yesterday (local time) that Samsung Electronics and SK Hynix’s “HBM-like” stacked structure mobile memory products will be commercialized after 2026. Sources said that the two Korean memory giants regard stacked mobile memory as an important source of future revenue and plan to expand "HBM-like memory" to smartphones, tablets and laptops to provide power for end-side AI. According to previous reports on this site, Samsung Electronics’ product is called LPWide I/O memory, and SK Hynix calls this technology VFO. The two companies have used roughly the same technical route, which is to combine fan-out packaging and vertical channels. Samsung Electronics’ LPWide I/O memory has a bit width of 512

Lexar launches Ares Wings of War DDR5 7600 16GB x2 memory kit: Hynix A-die particles, 1,299 yuan

May 07, 2024 am 08:13 AM

Lexar launches Ares Wings of War DDR5 7600 16GB x2 memory kit: Hynix A-die particles, 1,299 yuan

May 07, 2024 am 08:13 AM

According to news from this website on May 6, Lexar launched the Ares Wings of War series DDR57600CL36 overclocking memory. The 16GBx2 set will be available for pre-sale at 0:00 on May 7 with a deposit of 50 yuan, and the price is 1,299 yuan. Lexar Wings of War memory uses Hynix A-die memory chips, supports Intel XMP3.0, and provides the following two overclocking presets: 7600MT/s: CL36-46-46-961.4V8000MT/s: CL38-48-49 -1001.45V In terms of heat dissipation, this memory set is equipped with a 1.8mm thick all-aluminum heat dissipation vest and is equipped with PMIC's exclusive thermal conductive silicone grease pad. The memory uses 8 high-brightness LED beads and supports 13 RGB lighting modes.

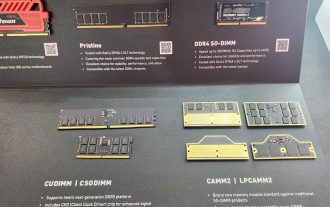

Kingbang launches new DDR5 8600 memory, offering CAMM2, LPCAMM2 and regular models to choose from

Jun 08, 2024 pm 01:35 PM

Kingbang launches new DDR5 8600 memory, offering CAMM2, LPCAMM2 and regular models to choose from

Jun 08, 2024 pm 01:35 PM

According to news from this site on June 7, GEIL launched its latest DDR5 solution at the 2024 Taipei International Computer Show, and provided SO-DIMM, CUDIMM, CSODIMM, CAMM2 and LPCAMM2 versions to choose from. ▲Picture source: Wccftech As shown in the picture, the CAMM2/LPCAMM2 memory exhibited by Jinbang adopts a very compact design, can provide a maximum capacity of 128GB, and a speed of up to 8533MT/s. Some of these products can even be stable on the AMDAM5 platform Overclocked to 9000MT/s without any auxiliary cooling. According to reports, Jinbang’s 2024 Polaris RGBDDR5 series memory can provide up to 8400