Hardware Tutorial

Hardware Tutorial

Hardware News

Hardware News

DDR5 MRDIMM and LPDDR6 CAMM memory specifications are ready for launch, JEDEC releases key technical details

DDR5 MRDIMM and LPDDR6 CAMM memory specifications are ready for launch, JEDEC releases key technical details

DDR5 MRDIMM and LPDDR6 CAMM memory specifications are ready for launch, JEDEC releases key technical details

This site reported on July 23 that the microelectronics standard setter JEDEC Solid State Technology Association announced on the 22nd local time that the DDR5 MRDIMM and LPDDR6 CAMM memory technical specifications will be officially launched soon, and introduced the key details of these two memories.

The "MR" in DDR5 MRDIMM stands for Multiplexed Rank, which means that the memory supports two or more Ranks and can combine and transmit multiple data signals on a single channel. Bandwidth can be effectively increased without the need for additional physical connections.

JEDEC has planned multiple generations of DDR5 MRDIMM memory, with the goal of eventually increasing its bandwidth to 12.8Gbps, doubling the current 6.4Gbps of DDR5 RDIMM memory.

In JEDEC’s vision, DDR5 MRDIMM will utilize the same pin, SPD, PMIC, etc. designs as existing DDR5 DIMM, be compatible with the RDIMM platform, and utilize the existing LRDIMM ecosystem for design and testing.

In addition, JEDEC has also planned the Tall MRDIMM form factor. As the name suggests, the design will feature a taller form factor that will double the number of DRAM packages it supports, further increasing memory capacity.

As for LPDDR6 CAMM, JEDEC said it is expected to achieve a maximum speed of more than 14.4GT/s, and will also mention 24bit wide sub-channel, 48bit Wide channel and supports "connector array" (note from this site: the original text is connector array).

The above is the detailed content of DDR5 MRDIMM and LPDDR6 CAMM memory specifications are ready for launch, JEDEC releases key technical details. For more information, please follow other related articles on the PHP Chinese website!

Hot AI Tools

Undresser.AI Undress

AI-powered app for creating realistic nude photos

AI Clothes Remover

Online AI tool for removing clothes from photos.

Undress AI Tool

Undress images for free

Clothoff.io

AI clothes remover

Video Face Swap

Swap faces in any video effortlessly with our completely free AI face swap tool!

Hot Article

Hot Tools

Notepad++7.3.1

Easy-to-use and free code editor

SublimeText3 Chinese version

Chinese version, very easy to use

Zend Studio 13.0.1

Powerful PHP integrated development environment

Dreamweaver CS6

Visual web development tools

SublimeText3 Mac version

God-level code editing software (SublimeText3)

Hot Topics

1664

1664

14

14

1422

1422

52

52

1316

1316

25

25

1267

1267

29

29

1239

1239

24

24

Printer has insufficient memory and cannot print the page Excel or PowerPoint error

Feb 19, 2024 pm 05:45 PM

Printer has insufficient memory and cannot print the page Excel or PowerPoint error

Feb 19, 2024 pm 05:45 PM

If you encounter the problem of insufficient printer memory when printing Excel worksheets or PowerPoint presentations, this article may be helpful to you. You may receive a similar error message stating that the printer does not have enough memory to print the page. However, there are some suggestions you can follow to resolve this issue. Why is printer memory unavailable when printing? Insufficient printer memory may cause a memory not available error. Sometimes it's because the printer driver settings are too low, but it can also be for other reasons. Large file size Printer driver Outdated or corrupt Interruption from installed add-ons Misconfiguration of printer settings This issue may also occur because of low memory settings on the Microsoft Windows printer driver. Repair printing

Large memory optimization, what should I do if the computer upgrades to 16g/32g memory speed and there is no change?

Jun 18, 2024 pm 06:51 PM

Large memory optimization, what should I do if the computer upgrades to 16g/32g memory speed and there is no change?

Jun 18, 2024 pm 06:51 PM

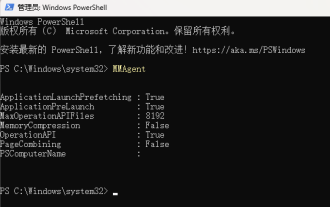

For mechanical hard drives or SATA solid-state drives, you will feel the increase in software running speed. If it is an NVME hard drive, you may not feel it. 1. Import the registry into the desktop and create a new text document, copy and paste the following content, save it as 1.reg, then right-click to merge and restart the computer. WindowsRegistryEditorVersion5.00[HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Control\SessionManager\MemoryManagement]"DisablePagingExecutive"=d

![Windows input encounters hang or high memory usage [Fix]](https://img.php.cn/upload/article/000/887/227/170835409686241.jpg?x-oss-process=image/resize,m_fill,h_207,w_330) Windows input encounters hang or high memory usage [Fix]

Feb 19, 2024 pm 10:48 PM

Windows input encounters hang or high memory usage [Fix]

Feb 19, 2024 pm 10:48 PM

The Windows input experience is a key system service responsible for processing user input from various human interface devices. It starts automatically at system startup and runs in the background. However, sometimes this service may automatically hang or occupy too much memory, resulting in reduced system performance. Therefore, it is crucial to monitor and manage this process in a timely manner to ensure system efficiency and stability. In this article, we will share how to fix issues where the Windows input experience hangs or causes high memory usage. The Windows Input Experience Service does not have a user interface, but it is closely related to handling basic system tasks and functions related to input devices. Its role is to help the Windows system understand every input entered by the user.

How to check memory usage on Xiaomi Mi 14Pro?

Mar 18, 2024 pm 02:19 PM

How to check memory usage on Xiaomi Mi 14Pro?

Mar 18, 2024 pm 02:19 PM

Recently, Xiaomi released a powerful high-end smartphone Xiaomi 14Pro, which not only has a stylish design, but also has internal and external black technology. The phone has top performance and excellent multitasking capabilities, allowing users to enjoy a fast and smooth mobile phone experience. However, performance will also be affected by memory. Many users want to know how to check the memory usage of Xiaomi 14Pro, so let’s take a look. How to check memory usage on Xiaomi Mi 14Pro? Introduction to how to check the memory usage of Xiaomi 14Pro. Open the [Application Management] button in [Settings] of Xiaomi 14Pro phone. To view the list of all installed apps, browse the list and find the app you want to view, click on it to enter the app details page. In the application details page

Is there a big difference between 8g and 16g memory in computers? (Choose 8g or 16g of computer memory)

Mar 13, 2024 pm 06:10 PM

Is there a big difference between 8g and 16g memory in computers? (Choose 8g or 16g of computer memory)

Mar 13, 2024 pm 06:10 PM

When novice users buy a computer, they will be curious about the difference between 8g and 16g computer memory? Should I choose 8g or 16g? In response to this problem, today the editor will explain it to you in detail. Is there a big difference between 8g and 16g of computer memory? 1. For ordinary families or ordinary work, 8G running memory can meet the requirements, so there is not much difference between 8g and 16g during use. 2. When used by game enthusiasts, currently large-scale games basically start at 6g, and 8g is the minimum standard. Currently, when the screen is 2k, higher resolution will not bring higher frame rate performance, so there is no big difference between 8g and 16g. 3. For audio and video editing users, there will be obvious differences between 8g and 16g.

Sources say Samsung Electronics and SK Hynix will commercialize stacked mobile memory after 2026

Sep 03, 2024 pm 02:15 PM

Sources say Samsung Electronics and SK Hynix will commercialize stacked mobile memory after 2026

Sep 03, 2024 pm 02:15 PM

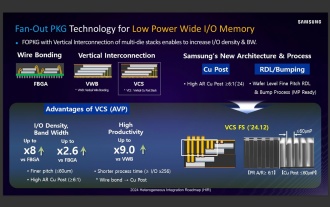

According to news from this website on September 3, Korean media etnews reported yesterday (local time) that Samsung Electronics and SK Hynix’s “HBM-like” stacked structure mobile memory products will be commercialized after 2026. Sources said that the two Korean memory giants regard stacked mobile memory as an important source of future revenue and plan to expand "HBM-like memory" to smartphones, tablets and laptops to provide power for end-side AI. According to previous reports on this site, Samsung Electronics’ product is called LPWide I/O memory, and SK Hynix calls this technology VFO. The two companies have used roughly the same technical route, which is to combine fan-out packaging and vertical channels. Samsung Electronics’ LPWide I/O memory has a bit width of 512

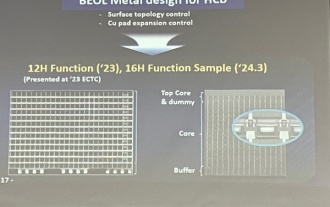

Samsung announced the completion of 16-layer hybrid bonding stacking process technology verification, which is expected to be widely used in HBM4 memory

Apr 07, 2024 pm 09:19 PM

Samsung announced the completion of 16-layer hybrid bonding stacking process technology verification, which is expected to be widely used in HBM4 memory

Apr 07, 2024 pm 09:19 PM

According to the report, Samsung Electronics executive Dae Woo Kim said that at the 2024 Korean Microelectronics and Packaging Society Annual Meeting, Samsung Electronics will complete the verification of the 16-layer hybrid bonding HBM memory technology. It is reported that this technology has passed technical verification. The report also stated that this technical verification will lay the foundation for the development of the memory market in the next few years. DaeWooKim said that Samsung Electronics has successfully manufactured a 16-layer stacked HBM3 memory based on hybrid bonding technology. The memory sample works normally. In the future, the 16-layer stacked hybrid bonding technology will be used for mass production of HBM4 memory. ▲Image source TheElec, same as below. Compared with the existing bonding process, hybrid bonding does not need to add bumps between DRAM memory layers, but directly connects the upper and lower layers copper to copper.

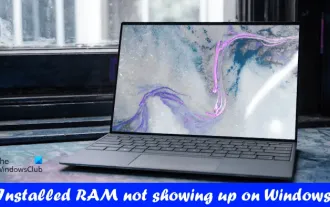

Installed memory not showing up on Windows 11

Mar 10, 2024 am 09:31 AM

Installed memory not showing up on Windows 11

Mar 10, 2024 am 09:31 AM

If you have installed new RAM but it is not showing up on your Windows computer, this article will help you resolve the issue. Usually, we improve the performance of the system by upgrading RAM. However, system performance also depends on other hardware such as CPU, SSD, etc. Upgrading RAM can also improve your gaming experience. Some users have noticed that installed memory is not showing up in Windows 11/10. If this happens to you, you can use the advice provided here. Installed RAM not showing up on Windows 11 If the installed RAM is not showing up on your Windows 11/10 PC, the following suggestions will help you. Is the installed memory compatible with your computer's motherboard? in BIO