What register is tcon?

TCON: Timer control register

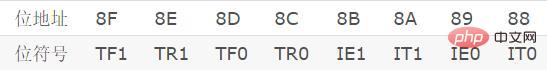

Register address 88H, bit addressing 8FH~88H

TF0(TF1)——Count overflow flag bit. When the counter overflows, this bit is set to 1.

TR0 (TR1) - timer operation control bit

When TR0 (TR1) = 0, stop the timer/counter operation

When TR0 (TR1) = 1, start Timer/counter operation

IE0 (IE1)——External interrupt request flag

When the CPU samples a valid interrupt request in P3.2 (P3.3), this bit is set by the hardware Set to 1. After the interrupt response is completed and the interrupt service is transferred, the hardware will automatically clear it to 0.

IT0 (IT1) - External interrupt request signal mode control bit

When IT0 (IT1) = 1 pulse mode (negative jump on the trailing edge is valid)

When IT0 ( IT1) = 0 level mode (active low level) This bit is set to 1 or cleared to 0 by software.

TF0 (TF1)——Count overflow flag bit

When the counter overflows, this bit is set to 1 by hardware. When switching to interrupt service, the hardware will automatically clear it to 0. There are two situations in which the count overflow flag bit is used: when the interrupt mode is used, it is used as the interrupt request flag bit; when the query mode is used, it is used as the query status bit.

For more related knowledge, please pay attention to PHP Chinese website!

The above is the detailed content of What register is tcon?. For more information, please follow other related articles on the PHP Chinese website!

Hot AI Tools

Undresser.AI Undress

AI-powered app for creating realistic nude photos

AI Clothes Remover

Online AI tool for removing clothes from photos.

Undress AI Tool

Undress images for free

Clothoff.io

AI clothes remover

AI Hentai Generator

Generate AI Hentai for free.

Hot Article

Hot Tools

Notepad++7.3.1

Easy-to-use and free code editor

SublimeText3 Chinese version

Chinese version, very easy to use

Zend Studio 13.0.1

Powerful PHP integrated development environment

Dreamweaver CS6

Visual web development tools

SublimeText3 Mac version

God-level code editing software (SublimeText3)

Hot Topics

1385

1385

52

52

What is the register that stores the offset address in the code segment?

Jan 22, 2021 pm 01:54 PM

What is the register that stores the offset address in the code segment?

Jan 22, 2021 pm 01:54 PM

The register that stores the offset address in the code segment is: the instruction pointer register. The instruction pointer register IP is used to control the execution sequence of instructions in the program; during normal operation, the IP contains the offset address of the next instruction (byte) to be fetched by the BIU. Under normal circumstances, the instruction code is accessed from memory every time , the IP will automatically increase by 1 to ensure the sequential execution of instructions.

In-depth understanding of Go language's control of registers

Apr 04, 2024 am 09:51 AM

In-depth understanding of Go language's control of registers

Apr 04, 2024 am 09:51 AM

The Go language optimizes performance by allowing direct control of CPU registers through assembly instructions: registers are temporary locations in the CPU where data is stored. The Go language provides assembly instructions through the asm package, which can be used to access x86 and ARM registers. Assembly instructions avoid the memory allocation overhead of iterators and improve loop performance. Caution is required when using assembly instructions due to platform and system dependencies, potential program crash risks, and the use-only-when-necessary principle.

In C language, what is the register storage class?

Aug 30, 2023 am 09:45 AM

In C language, what is the register storage class?

Aug 30, 2023 am 09:45 AM

There are four storage classes in the C programming language, namely: autoexternstaticregister. The keyword of the register variable is register. The value of a register variable is stored in the CPU's register instead of in memory, where ordinary variables are stored. Registers are temporary storage units in the CPU. They allow register variables to have faster access times than ordinary variables. Example 1 The following is the register storage class of the C program: Demonstration #include<stdio.h>main(){ registerinti;&

Analyze the Go language's ability to manipulate registers

Apr 03, 2024 pm 09:03 PM

Analyze the Go language's ability to manipulate registers

Apr 03, 2024 pm 09:03 PM

The Go language provides access to and operations on registers through assembly inlining. Program performance can be significantly improved by using registers such as integer registers, floating point registers, and vector registers. Through a practical case demonstration of optimizing integer multiplication operations, this article shows how to use registers for efficient low-level operations to create faster Go applications.

What is the register that controls how the serial port works?

Jul 22, 2022 am 10:53 AM

What is the register that controls how the serial port works?

Jul 22, 2022 am 10:53 AM

The register that controls the working mode of the serial port is SCON, which is the serial port control register; SCON is used to control the selection, reception and transmission of serial communication methods, and indicates the status of the serial port. SCON can be both byte-addressed and bit-addressed. address, the byte address is "98H", and the address bits are "98H~9FH".

What is a device that contains a small amount of data stored in the CPU called?

Jul 18, 2022 pm 04:29 PM

What is a device that contains a small amount of data stored in the CPU called?

Jul 18, 2022 pm 04:29 PM

It's called a "register". Registers are small storage areas used to store data inside the CPU. They are used to temporarily store data and operation results involved in operations. The function of the register is to store binary codes, which are composed of flip-flops with storage functions; one flip-flop can store 1-bit binary code, so a register that stores n-bit binary codes needs n flip-flops.

Research on register control capabilities of Go language

Apr 04, 2024 am 08:09 AM

Research on register control capabilities of Go language

Apr 04, 2024 am 08:09 AM

The Go language provides limited control over registers, allowing low-level optimizations. Assembly instructions (MOVQ, MOVL, MOVB, ADDQ, SUBQ) can be used to control registers, but they need to be used with caution to avoid breaking register references in the garbage collection mechanism. In addition, the use of assembly instructions requires knowledge of assembly language and is platform dependent.

Can go language control registers?

Aug 24, 2023 pm 01:41 PM

Can go language control registers?

Aug 24, 2023 pm 01:41 PM

The Go language cannot directly control registers. The Go language is limited in its ability to access registers because the design goal of the Go language is to provide a safer and easier-to-use programming environment rather than directly accessing hardware. Although the registers cannot be controlled directly, some mechanisms are provided to interact with the hardware. Developers can use these interfaces to communicate with external devices and control their behavior. The Go language also provides some low-level programming capabilities to bypass the restrictions of the type system and directly access memory.