mstatus.MIE 写入 0(默认复位值)来全局禁用中断。将机器模式异常处理程序的基地址写入 mtvec CSR。这是任何引导流程中的必需步骤。将 mstatus.MPP 写入 0 以将之前的模式设置为 User,这允许我们返回到该模式。设置物理内存保护 (PMP) 区域以将所需区域授予用户和主管模式,并可选择从机器模式撤消权限。用主管模式异常处理程序的基地址写入 stvec CSR。编写 medeleg 寄存器,将异常委托给主管模式。考虑 ECALL 和页面错误异常。编写 mstatus.FS 以启用浮点(如果支持)。将机器模式用户寄存器存储到堆栈或应用程序特定的帧指针。用用户态软件的入口点编写mepc

mret指令进入用户模式。Note:只有一组用户寄存器 (x1 - x31) 用于所有权限级别,因此应用软件负责在进入和退出不同级别时保存和恢复状态。本地中断 软件中断(中断 ID #3):通过写入特定 hart 的内存映射中断挂起寄存器 msip 来触发。定时器中断:当寄存器 mtime 大于或等于寄存器 mtimecmp 并且两个寄存器都是 CLINT 内存映射的一部分时,会触发定时器中断(中断 ID #7)。mtime 和 mtimecmp 寄存器通常仅在机器模式下可用,除非 PMP 授予用户或管理员模式访问它们所在的内存映射区域的权限。全局中断通常首先路由到 PLIC,然后使用外部中断进入 hart(中断 ID #11)中断操作 在特权模式 m 内,如果相关的全局中断使能 {ie} 清零,则在该特权模式下不会产生任何中断,但更高特权模式下的待决启用中断将抢占当前执行。如果设置了 {ie},则在相同特权模式下处于更高中断级别的挂起启用中断将抢占当前执行并运行更高中断级别的中断处理程序。当发生中断或同步异常时,会修改特权模式以反映新的特权模式。处理程序特权模式的全局中断使能位被清除中断进入和退出当中断发生时:• mstatus.MIE 的值被复制到mcause.MPIE 中,然后mstatus.MIE 被清除,有效地禁用了中断。• 中断前的特权模式在mstatus.MPP 中编码。• 当前 pc 被复制到 mepc 寄存器中,然后将 pc 设置为 mtvec 指定的值此时,控制权移交给中断处理程序中的软件,并禁用中断。执行 mret 指令时,会发生以下情况:• 特权模式设置为在 mstatus.MPP 中编码的值。• 全局中断使能 mstatus.MIE 设置为 mcause.MPIE 的值。• pc 设置为mepc 的值。此时,控制权交给软件。中断控制和状态寄存器 Machine Status Register (mstatus)mstatus 寄存器跟踪并控制 hart 的当前操作状态,包括是否启用中断。通过设置 mstatus 中的 MIE 位来启用中断。在写入 mstatus.MIE=1 之前,建议先在 mie 中开启中断。Machine Trap Vector (mtvec)mtvec 寄存器有两个主要功能:定义陷阱向量的基地址,以及设置 U54内核处理中断的模式。对于 Direct 和 Vectored 模式,中断处理模式在 mtvec 寄存器的 MODE 字段中定义。mtvec 寄存器在表 86 中描述,mtvec.MODE 字段在表 87 中描述。Mode Direct在直接模式下操作时,所有中断和异常都会捕获到 mtvec.BASE 地址。在陷阱处理程序内部,软件必须读取 mcause 寄存器以确定触发陷阱的原因。在直接模式下操作时,BASE 必须是 4 字节对齐的。Mode Vectored在向量模式下运行时,中断将 pc 设置为 mtvec.BASE + 4 × 异常代码(mcause.EXCCODE)。例如,如果发生机器定时器中断,则将 pc 设置为 mtvec.BASE + 0x1C。通常,陷阱向量表填充有跳转指令,以将控制转移到特定于中断的陷阱处理程序。在向量中断模式下,BASE 必须是 256 字节对齐的。所有机器外部中断(全局中断)都映射到异常代码 11。因此,当启用中断向量时,pc 设置为任何全局中断的地址 mtvec.BASE + 0x2C。Machine Interrupt Enable (mie)通过设置 mie 寄存器中的相应位来启用各个中断。Machine Interrupt Pending (mip)机器中断挂起 (mip) 寄存器指示当前哪些中断处于挂起状态。特权模式中断 U54内核支持有选择地将中断和异常定向到S模式。该功能由中断和异常委托CSR处理:mideleg和medeleg。S模式中断和异常可以通过stvec、sip、sie 和 scause 管理。在M模式下,软件还可以直接写入SIP寄存器,从而有效地向S模式发送中断。这对于定时器和软件中断特别有用,因为可能需要在M模式和S模式下处理这些中断。Delegation Registers (mideleg and medeleg)默认情况下,所有的trap都在M模式下处理。M模式下软件可以通过CSR 有选择地将中断和异常委托给S模式。具体的映射如表 92 和表 93 。注意,本地中断可以委托给M模式。Supervisor Status Register (sstatus)与M模式类似,S模式有一个寄存器,专门用于跟踪 hart 的当前状态,称为 sstatus。sstatus 实际上是 mstatus 的受限视图,因为对 sstatus 所做的更改反映在 mstatus 中。通过在 sstatus 中设置 SIE 位并在 sie 寄存器中启用所需的单个中断来启用中断。Supervisor Interrupt Enable Register (sie)通过在 sie 寄存器中设置适当的位来启用管理员中断。Supervisor Interrupt Pending (sip)S模式中断挂起 (sip) 寄存器指示当前哪些中断挂起。Supervisor Cause Register (scause)当S模式下捕获陷阱时,将导致陷阱的事件的代码写入 cause。当导致陷阱的事件是中断时,最高有效位

scause 设置为 1,最低有效位表示中断号,使用与 sip 中的位置相同的编码。例如,S模式定时器中断导致 cause 被设置为 0x8000_0000_0000_0005。scause 也用于指示同步异常的原因,在这种情况下,scause 的最高有效位设置为 0。有关同步异常代码的列表,请参见表 98。Supervisor Trap Vector (stvec)默认情况下,所有中断都会捕获到 stvec 寄存器中定义的单个地址。由中断处理程序读取原因并做出相应的反应。RISC‑V 和 U54 内核还支持选择性地启用中断向量的能力。当启用向量时,在 sie 中定义的每个中断都会陷入到它自己的特定中断处理程序中。当 stvec 寄存器的 MODE 字段设置为 1 时,向量中断被启用。如果向量中断被禁用 (stvec.MODE=0),所有中断都会陷入 stvec.BASE 地址。如果启用矢量中断 (stvec.MODE=1),中断将 pc 设置为 stvec.BASE + 4 × 异常代码 (scause.EXCCODE)。例如,如果发生管理定时器中断,则 pc 设置为 stvec.BASE + 0x14。通常,陷阱向量表中填充有跳转指令,以将控制转移到特定于中断的陷阱处理程序。在向量中断模式下,BASE 必须是 128 字节对齐的。所有主管外部中断(全局中断)都映射到异常代码 9。因此,当启用中断向量时,pc 被设置为任何全局中断的地址 stvec.BASE + 0x24。Delegated Interrupt Handling接受委派陷阱后,会发生以下情况:sstatus.SIE 的值被复制到 sstatus.SPIE,然后 sstatus.SIE 被清除,有效地禁用中断。当前pc被复制到sepc寄存器中,然后pc被设置为stvec的值。在启用矢量中断的情况下,pc 设置为 stvec.BASE + 4 × 异常代码 (scause.EXCCODE)。中断前的特权模式编码在 sstatus.SPP 中此时,控制权移交给中断处理程序中的软件,中断被禁用。可以通过显式设置 sstatus.SIE 或执行 SRET 指令退出处理程序来重新启用中断。执行 SRET 指令时,会发生以下情况:特权模式设置为 sstatus.SPP 中编码的值status.SPIE 的值被复制到 status.SIEpc is set to the value of sepcAt this time, Control is given to the software

The interrupt latency of the U54 core is four external_source_for_core_N_clock cycles, calculated The way to do this is to get the number of cycles required from the first instruction that sends an interrupt signal to hart to the handler.

Global interrupts routed through the PLIC cause an additional delay of three clock cycles, where the PLIC is clocked by the clock. This means that the total latency of global interrupts in cycles is: 4 3 × (external_source_for_core_N_clock Hz ÷ clock Hz). This is a best-case loop count and assumes the handler is cached. It does not account for additional delays from peripheral sources

rnmi (recoverable non-maskable interrupt) interrupt signal is hart's electrical level sensitive input. Non-maskable interrupts have higher priority than any other interrupt or exception on hart and cannot be disabled by software. Specifically, they are not disabled by clearing the mstatus.mie register.

NMI has an associated exception trap handler address. This address is set by an external input signal.

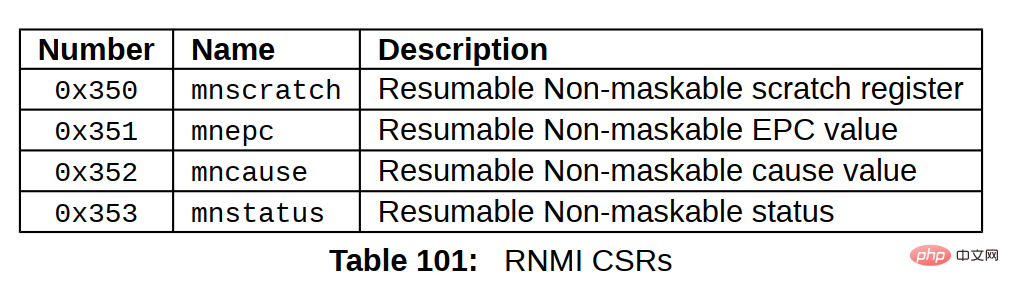

These M-mode CSRs enable Recoverable Non-Maskable Interrupts (RNMI).

此仅 M 模式指令使用 mnepc 和 mnstatus 中的值分别返回中断上下文的程序计数器和特权模式。该指令还设置内部 rnmie 状态位。

编码与 MRET 相同,除了第 30 位设置(即 funct7=0111000)。例如:

.word 0x70200073 // opcode for MNRET (return from RNMI)

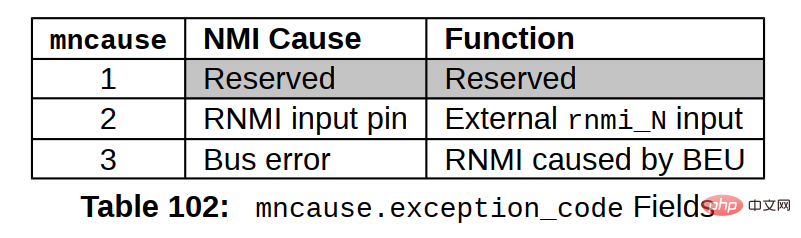

当检测到RNMI中断时,将中断的PC写入mnepc CSR,RNMI的类型写入mncause CSR,中断上下文的特权模式写入mnstatus CSR。内部微体系结构状态位 rnmie 被清除以指示处理器处于 RNMI 处理程序中并且不能接受新的 RNMI 中断。清除时,内部 rnmie 位还会禁用所有其他中断

这些中断被称为不可屏蔽的,因为软件无法屏蔽中断。但是,为了正确操作,必须推迟同一中断的其他实例,直到处理程序完成,因此内部状态位

RNMI 处理程序可以使用 MNRET 指令(在第 7.11.3 节中描述)恢复原始执行,该指令从 mnepc 恢复 PC,从 mnstatus 恢复特权模式,并设置内部 rnmie 状态位,重新启用其他中断。

如果hart在rnmie位清零时遇到异常,则将异常状态写入mepc和mcause,mstatus.mpp设置为M-mode,hart跳转到RNMI异常处理程序地址。

RNMI 处理程序中的陷阱只有在处理程序正在服务发生在机器模式之外的中断时发生时才能恢复。

The above is the detailed content of RISC-V SiFive U54 core - detailed explanation of interrupts and exceptions. For more information, please follow other related articles on the PHP Chinese website!

How to check server status

How to check server status

How to solve the computer prompt of insufficient memory

How to solve the computer prompt of insufficient memory

How to optimize a single page

How to optimize a single page

What should I do if the web video cannot be opened?

What should I do if the web video cannot be opened?

How to implement linked list in go

How to implement linked list in go

How to buy and sell Bitcoin legally

How to buy and sell Bitcoin legally

Introduction to the main work content of the backend

Introduction to the main work content of the backend

Use of jQuery hover() method

Use of jQuery hover() method

Why does the computer have a blue screen?

Why does the computer have a blue screen?