Operation and Maintenance

Operation and Maintenance

Linux Operation and Maintenance

Linux Operation and Maintenance

Practical combat | RISC-V Linux entry address 2M reserved memory optimization

Practical combat | RISC-V Linux entry address 2M reserved memory optimization

Practical combat | RISC-V Linux entry address 2M reserved memory optimization

The previous article analyzed the page table creation for RISC-V Linux startup. It was mentioned that the RISC-V Linux entry address must be 2M aligned. Today I will talk about how to solve the 2M alignment problem, or how to optimize the part. Memory.

Note: This article is based on the linux5.10.111 kernel

Memory usage analysis

When each chip leaves the factory, its bootrom has been solidified inside the chip. Assume that the address of the bootrom is 0x0, that is, after power-on, the program will start running from the 0x0 address.

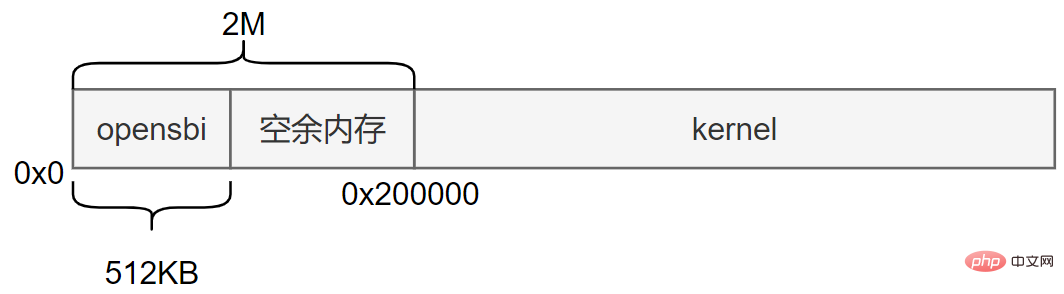

Before starting RISC-V Linux, you need to run opensbi first, so opensbi should be placed at the address 0x0, so that after the chip is powered on, it will start from 0x0Execute opensbi at the address. After opensbi runs, it will jump to the location where the opensbi running address is offset by 2M to execute the next-level boot (the next-level boot here is the kernel), that is, jump to the 0x200000 address to run the kernel. Therefore, the kernel should be placed at 0x200000 in the memory.

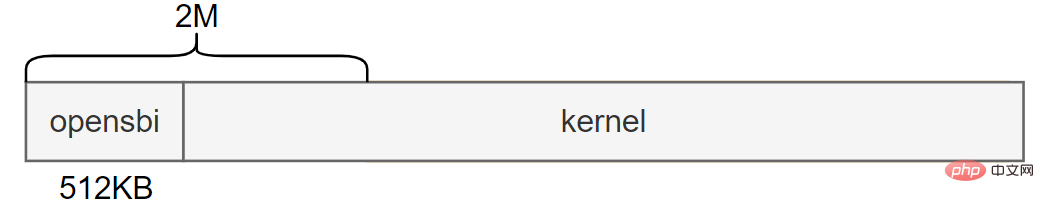

The memory distribution diagram is as follows:

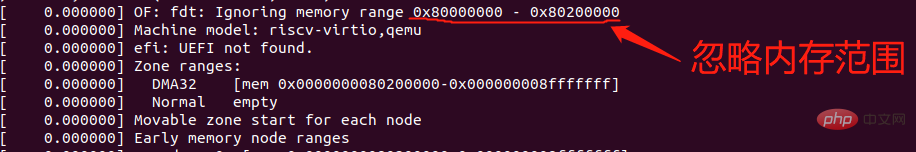

For the kernel, the page table mapping will be established starting from its own kernel loading address (i.e. 0x200000) at startup. Only the physical memory is established. Page table mapping, these memories can be accessed later. The 2M memory in front of the kernel loading address (i.e. 0x0 - 0x200000) will be ignored by the kernel, and a page table will not be established for this 2M memory, that is, the kernel cannot access this 2M memory.

Startup information of RISC-V Linux on QEMU:

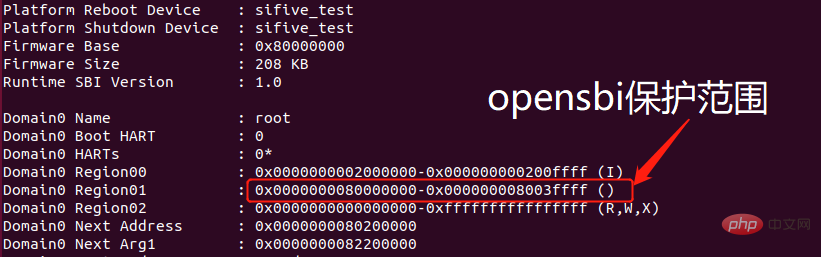

But opensbi does not actually need to use a range as large as 2M, the default is 512KB , opensbi's pmp will protect this 512KB memory and prevent other programs from accessing it.

Therefore, there will be a memory gap of 1.5M between Kernel and opensbi, and this part of the memory gap is not used by the program, which will cause memory It's a waste, so how do you let the kernel use the previous part of the memory?

Optimization plan

There are two options for optimizing this 2M memory:

Option 1: Put opensbi at the end of the memory, and the kernel entry address remains 2M aligned.

Option 2: Opensbi is still placed at the starting position of the memory. By modifying the kernel source code and lifting the 2M alignment restriction, the kernel address can be moved forward.

Option 1

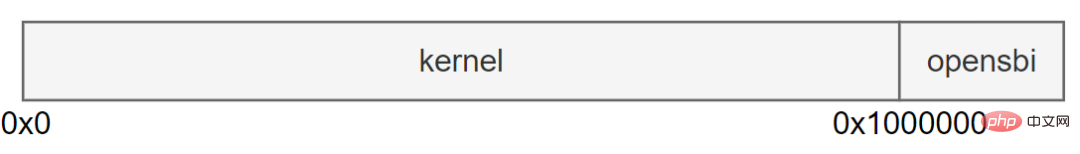

We put opensbi at the end of the memory, and the kernel entry address still maintains 2M alignment.

That is, the kernel is placed at the front of the memory, and opensbi is placed at the back:

For example, the kernel is placed at the address 0x0 of the memory. , opensbi is placed at the 0x10000000 address in the memory. In this way, there will be no reserved memory in front of the kernel, but needs to modify the bootrom address from 0x0 to 0x0x10000000. This solution is only suitable before the chip leaves the factory, because the user cannot modify the bootrom address. After the chip leaves the factory, the bootrom address is fixed. Assuming that the bootrom address is 0x0, then the bootrom address on the chip After powering up, the program will start running from 0x0, so opensbi must be placed at the address 0x0, so the kernel can only be offset by 2M.

Option 2

We can also modify the kernel source code of RISC-V Linux to lift the 2M alignment restriction. We only need to change the original second-level page table to the third-level page table in the setup_vm() function, so that the kernel entry address only needs to be aligned at 4K, so the kernel can be Move forward to use the memory at the front.

Modify the code

Path: arch/riscv/mm/init.c

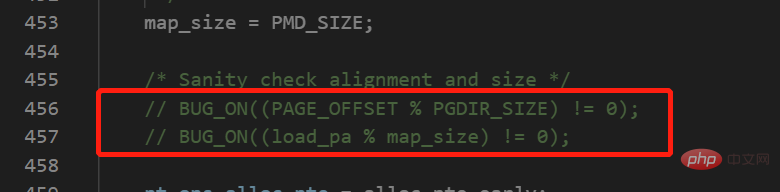

Comment original 2M alignment check:

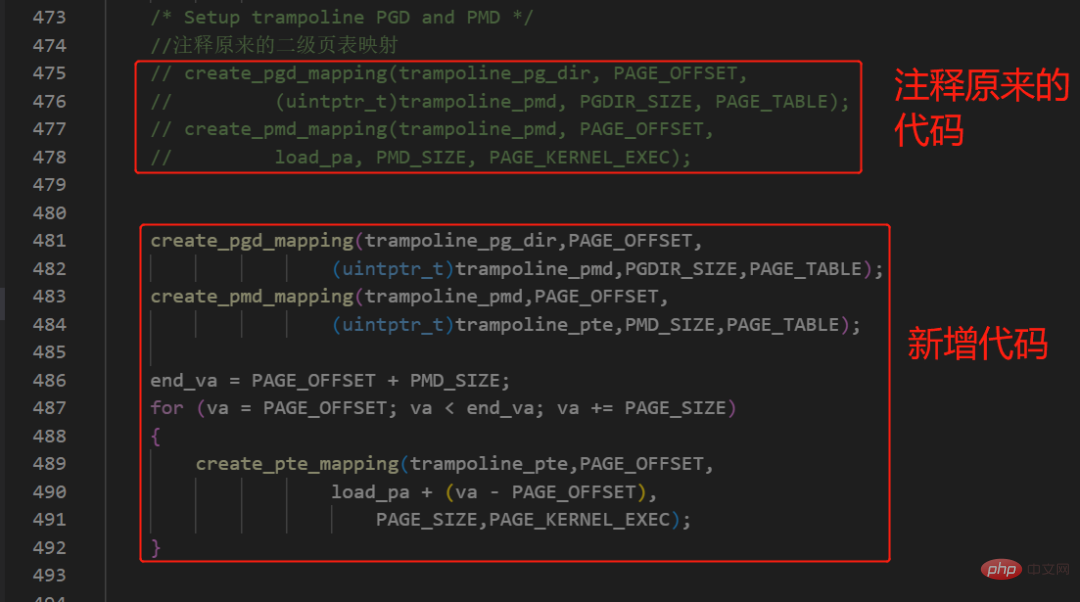

The mapping of the first 2M page table of the kernel is changed from the second-level page table to the third-level page table:

//新增一个PTE

pte_t trampoline_pte[PTRS_PER_PTE] __page_aligned_bss;

create_pgd_mapping(trampoline_pg_dir,PAGE_OFFSET,

(uintptr_t)trampoline_pmd,PGDIR_SIZE,PAGE_TABLE);

create_pmd_mapping(trampoline_pmd,PAGE_OFFSET,

(uintptr_t)trampoline_pte,PMD_SIZE,PAGE_TABLE);

end_va = PAGE_OFFSET + PMD_SIZE;

for (va = PAGE_OFFSET; va < end_va; va += PAGE_SIZE)

{

create_pte_mapping(trampoline_pte,PAGE_OFFSET,

load_pa + (va - PAGE_OFFSET),

PAGE_SIZE,PAGE_KERNEL_EXEC);

}

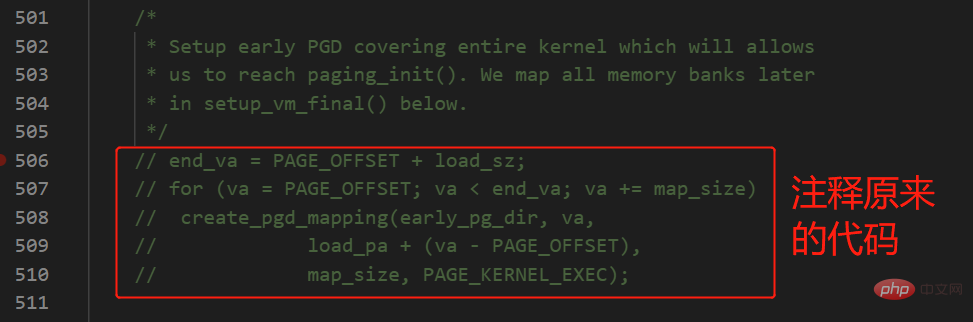

The page table mapping of the entire kernel is changed from the second-level page table to the third-level page table:

Assume that the kernel size is 4M

//定义三个PTE

pte_t load_sz_pte[PTRS_PER_PTE] __page_aligned_bss;

pte_t load_sz_pte1[PTRS_PER_PTE] __page_aligned_bss;

pte_t load_sz_pte2[PTRS_PER_PTE] __page_aligned_bss;

//=======0-2M======

create_pgd_mapping(early_pg_dir,PAGE_OFFSET,

(uintptr_t)early_pmd,PGDIR_SIZE,PAGE_TABLE);

create_pmd_mapping(early_pmd,PAGE_OFFSET,

(uintptr_t)load_sz_pte,PMD_SIZE,PAGE_TABLE);

end_va = PAGE_OFFSET + PMD_SIZE;

for (va = PAGE_OFFSET; va < end_va; va += PAGE_SIZE)

{

create_pte_mapping(load_sz_pte,PAGE_OFFSET,

load_pa + (va - PAGE_OFFSET),

PAGE_SIZE,PAGE_KERNEL_EXEC);

}

//=======2-4M==========

create_pgd_mapping(early_pg_dir,PAGE_OFFSET + PMD_SIZE,

(uintptr_t)early_pmd,PGDIR_SIZE,PAGE_TABLE);

create_pmd_mapping(early_pmd,PAGE_OFFSET,

(uintptr_t)load_sz_pte1,PMD_SIZE,PAGE_TABLE);

end_va = PAGE_OFFSET + (PMD_SIZE * 2);

for (va = PAGE_OFFSET + PMD_SIZE; va < end_va; va += PAGE_SIZE)

{

create_pte_mapping(load_sz_pte1,va,

load_pa + (va - PAGE_OFFSET),

PAGE_SIZE,PAGE_KERNEL_EXEC);

}

//=======4-6M==========

create_pgd_mapping(early_pg_dir,PAGE_OFFSET + (PMD_SIZE*2),

(uintptr_t)early_pmd,PGDIR_SIZE,PAGE_TABLE);

create_pmd_mapping(early_pmd,PAGE_OFFSET,

(uintptr_t)load_sz_pte2,PMD_SIZE,PAGE_TABLE);

end_va = PAGE_OFFSET + (PMD_SIZE * 3);

for (va = PAGE_OFFSET + (PMD_SIZE*2); va < end_va; va += PAGE_SIZE)

{

create_pte_mapping(load_sz_pte2,va,

load_pa + (va - PAGE_OFFSET),

PAGE_SIZE,PAGE_KERNEL_EXEC);

}

Through the above code modification, the Kernel entry address can be moved forward by 1.5M, and only 512KB is reserved for opensbi. In this way, after RISC-V Linux starts, Available physical memory will increase.

Summary

RISC-V Linux entry address 2M alignment operation is not yet available I saw someone explaining it, but it should be to reserve 2M for opensbi, so the kernel only established a secondary page table, so that the entry address must be aligned with 2M. No one has yet given an optimization solution for this part of memory. I hope the optimization solution in this article can help some people and give you some inspiration.

The above is the detailed content of Practical combat | RISC-V Linux entry address 2M reserved memory optimization. For more information, please follow other related articles on the PHP Chinese website!

Hot AI Tools

Undresser.AI Undress

AI-powered app for creating realistic nude photos

AI Clothes Remover

Online AI tool for removing clothes from photos.

Undress AI Tool

Undress images for free

Clothoff.io

AI clothes remover

AI Hentai Generator

Generate AI Hentai for free.

Hot Article

Hot Tools

Notepad++7.3.1

Easy-to-use and free code editor

SublimeText3 Chinese version

Chinese version, very easy to use

Zend Studio 13.0.1

Powerful PHP integrated development environment

Dreamweaver CS6

Visual web development tools

SublimeText3 Mac version

God-level code editing software (SublimeText3)

Hot Topics

1378

1378

52

52

Exploring the functions of the Linux kernel: a detailed introduction to the five major parts

Mar 21, 2024 am 09:57 AM

Exploring the functions of the Linux kernel: a detailed introduction to the five major parts

Mar 21, 2024 am 09:57 AM

As the core part of the operating system, the Linux kernel is responsible for important functions such as managing hardware resources and providing system calls. This article will delve into the five major parts of the Linux kernel, including process management, file system, network communication, device driver and memory management, and provide a detailed introduction and code examples. 1. Process Management Process Creation In the Linux kernel, process creation is implemented through the fork() system call. Here is a simple example code: #include

Is non-MMU support provided by the uClinux port of the Linux kernel?

Jan 26, 2024 pm 05:18 PM

Is non-MMU support provided by the uClinux port of the Linux kernel?

Jan 26, 2024 pm 05:18 PM

It’s long and has a lot of technical content, so click to follow it and you won’t get lost. Preface: Understanding the Linux Kernel A computer system is a symbiosis of hardware and software. They are interdependent and inseparable. Computer hardware Linux kernel transplantation steps include peripheral devices, processors, memory, hard drives and other electronic devices that make up the computer cylinder. And without software to operate and control it, it cannot work by itself. The software that completes this control work is called the operating system. In Linux terminology, it is called the "kernel" or "core". The main modules (or components) of the Linux kernel are divided into the following parts: storage management, CPU and process management, file system, device management and driver, network communication Linux forum, and system

Practical combat | RISC-V Linux entry address 2M reserved memory optimization

Aug 01, 2023 pm 03:37 PM

Practical combat | RISC-V Linux entry address 2M reserved memory optimization

Aug 01, 2023 pm 03:37 PM

The previous article analyzed the page table creation for RISC-V Linux startup. It was mentioned that the RISC-V Linux entry address must be 2M aligned. Today I will talk about how to solve the 2M alignment problem, or how to optimize part of the memory.

Secret tips for Linux kernel TCP protocol stack optimization revealed

Jan 28, 2024 am 09:39 AM

Secret tips for Linux kernel TCP protocol stack optimization revealed

Jan 28, 2024 am 09:39 AM

Hello dear readers! Here, I am honored to share with you the valuable experience and skills I have accumulated as a senior network engineer with my professional skills in the development and optimization of the Linux kernel TCP protocol stack. I believe that through this article, we can learn from each other and discuss it, and bring practical and useful reference materials to you who have a strong interest in this field or are currently working on it. 1. TCP connection establishment TCP connection establishment is a key transaction of the TCP protocol stack, but it is not uncommon to face many connection problems. After careful consideration and detailed debugging, I discovered some common and practical problems and their solutions, including preventing SYN flooding attacks (by adjusting system parameters) and dealing with network congestion (that is, using TCPFastOp

Linux Kernel: Revealing the Hidden BOSS of Computer Operating Systems

Mar 24, 2024 am 09:10 AM

Linux Kernel: Revealing the Hidden BOSS of Computer Operating Systems

Mar 24, 2024 am 09:10 AM

Discusses the view that the Linux kernel plays an important role in computer operating systems. Linux kernel design and implementation. Through in-depth analysis of Linux kernel design and practical applications, it reveals its prominent position and influence in this field. 1. Optimized memory management By using virtual memory management technology, the Linux kernel can efficiently complete memory allocation and recycling. With the help of the replacement page algorithm, the Linux kernel is designed and implemented to accurately handle the mapping relationship between physical memory and virtual memory. Flexible adjustments can be made based on the specific needs of the application, thereby improving overall system performance. 2. The powerful process management kernel uses its excellent multi-tasking technology to enable multiple processes to coexist harmoniously in a single system. Carefully formulated

An in-depth exploration of the Linux kernel source code distribution

Mar 15, 2024 am 10:21 AM

An in-depth exploration of the Linux kernel source code distribution

Mar 15, 2024 am 10:21 AM

This is a 1500-word article that explores the Linux kernel source code distribution in depth. Due to limited space, we will focus on the organizational structure of the Linux kernel source code and provide some specific code examples to help readers better understand. The Linux kernel is an open source operating system kernel whose source code is hosted on GitHub. The entire Linux kernel source code distribution is very large, containing hundreds of thousands of lines of code, involving multiple different subsystems and modules. To gain a deeper understanding of the Linux kernel source code

Explore the relationship between the Android system and the Linux kernel

Mar 14, 2024 pm 12:48 PM

Explore the relationship between the Android system and the Linux kernel

Mar 14, 2024 pm 12:48 PM

The Android system and the Linux kernel are two closely related entities, and the relationship between them is close and complex. In the Android system, the Linux kernel plays an important role, providing underlying hardware drivers and system call support for the Android system. This article will explore the relationship between the Android system and the Linux kernel, how they interact and work together, and provide some specific code examples. Android is a mobile operating system developed based on the Linux kernel and is mainly used for mobile devices such as smartphones and tablets. L

Do you really know how to debug Linux kernel failures? You will be enlightened after reading this article!

Aug 03, 2023 pm 04:50 PM

Do you really know how to debug Linux kernel failures? You will be enlightened after reading this article!

Aug 03, 2023 pm 04:50 PM

The Linux kernel is the core of the operating system and controls access to system resources such as the CPU, I/O devices, physical memory, and file systems. During the boot process and while the system is running, the kernel writes various messages to the kernel ring buffer. These messages include a variety of information about system operations.