Web Front-end

Web Front-end

HTML Tutorial

HTML Tutorial

The principle and implementation of the update mechanism of the second level cache

The principle and implementation of the update mechanism of the second level cache

The principle and implementation of the update mechanism of the second level cache

The principle and implementation method of the second-level cache update mechanism

1. Introduction

With the development of computer technology, the demand for data processing and storage increases. System performance requirements are also getting higher and higher. In order to improve the operating efficiency of the system, caching technology came into being. In caching technology, second-level cache is an important component. This article will introduce the principle and implementation of the second-level cache update mechanism.

2. The concept and function of the second-level cache

The second-level cache refers to the second-level cache between the first-level cache and the third-level cache between the CPU and main memory. Its role is to improve the efficiency of data transmission between the processor and main memory and the overall performance of the system. In computer systems, there are differences in data access speeds. The CPU accesses registers the fastest, while accessing memory is slower. Therefore, in order to reduce the access delay between the CPU and memory and improve the performance of the system, the second level cache is introduced.

3. Principle of the second-level cache update mechanism

The principle of the second-level cache update mechanism is to use a series of technical means to dynamically update the data in the cache, maintain data consistency, and improve data access efficiency. Specifically, the principles of the second-level cache update mechanism have the following aspects:

- Write-back strategy: When the second-level cache adopts the write-back strategy, when the CPU writes to the cache, it does not write immediately. Instead, the data is written to the cache first, and then the data is written to the memory when a certain condition is met. This can reduce the number of writes to the memory and improve the system's response speed.

- Cache write invalidation mechanism: When the data written by the CPU to the cache changes, the cache write invalidation mechanism will be triggered. During the write invalidation process, the cache controller will be responsible for updating modified data into memory and updating other levels of cache when necessary.

- Invalidation processing: When a data block is modified in the cache, other levels of cache need to be invalidated. Invalidation processing refers to invalidating the status of the corresponding data block in other levels of cache, so that other levels of cache can re-read the data block from memory.

- Write hit rate optimization: Due to frequent write operations, it is easy to cause the write hit rate to decrease. In order to optimize the write hit rate, a write allocation strategy and a write non-allocation strategy can be adopted. The write allocation strategy means writing the written data directly into the cache, while the write non-allocation strategy means writing the written data directly into the main memory without writing it into the cache.

4. Implementation method of the second-level cache update mechanism

The implementation method of the second-level cache update mechanism can be selected according to the specific hardware architecture and system requirements. Currently, the common implementation methods are as follows:

- Direct update: When the CPU writes to the cache, the data is written directly to the memory without going through other levels of cache. The advantage of this method is that it is simple to implement, but in a multi-level cache system, it will cause frequent memory write operations and reduce system performance.

- Level-by-level update: When the CPU writes to the cache, the data will be updated to other levels of cache and memory step by step. The advantage of this method is that it can maintain data consistency, but it will increase the delay of data update.

- Delayed update: When the CPU writes to the cache, the data is not written to the memory immediately, but is written delayed. The advantage of delayed updates is that it can improve the response speed of the system and reduce the frequency of memory write operations. But it will also increase the delay of data update.

5. Conclusion

The second-level cache update mechanism plays an important role in improving system performance and reducing latency. By adopting appropriate update mechanisms and implementation methods, data consistency can be effectively maintained, data access efficiency can be improved, and memory write operations can be effectively reduced. For different systems and application scenarios, appropriate mechanisms and implementation methods can be selected to meet needs. Through continuous optimization and improvement, the second-level cache update mechanism will play a more important role in future computer systems.

The above is the detailed content of The principle and implementation of the update mechanism of the second level cache. For more information, please follow other related articles on the PHP Chinese website!

Hot AI Tools

Undresser.AI Undress

AI-powered app for creating realistic nude photos

AI Clothes Remover

Online AI tool for removing clothes from photos.

Undress AI Tool

Undress images for free

Clothoff.io

AI clothes remover

AI Hentai Generator

Generate AI Hentai for free.

Hot Article

Hot Tools

Notepad++7.3.1

Easy-to-use and free code editor

SublimeText3 Chinese version

Chinese version, very easy to use

Zend Studio 13.0.1

Powerful PHP integrated development environment

Dreamweaver CS6

Visual web development tools

SublimeText3 Mac version

God-level code editing software (SublimeText3)

Hot Topics

1359

1359

52

52

What does dao mean in java

Apr 21, 2024 am 02:08 AM

What does dao mean in java

Apr 21, 2024 am 02:08 AM

DAO (Data Access Object) in Java is used to separate application code and persistence layer, its advantages include: Separation: Independent from application logic, making it easier to modify it. Encapsulation: Hide database access details and simplify interaction with the database. Scalability: Easily expandable to support new databases or persistence technologies. With DAOs, applications can call methods to perform database operations such as create, read, update, and delete entities without directly dealing with database details.

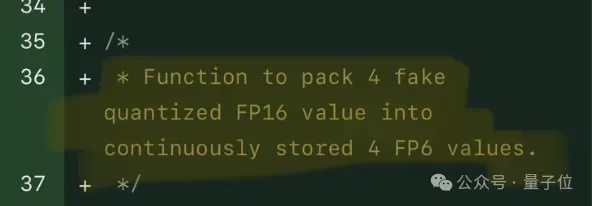

Single card running Llama 70B is faster than dual card, Microsoft forced FP6 into A100 | Open source

Apr 29, 2024 pm 04:55 PM

Single card running Llama 70B is faster than dual card, Microsoft forced FP6 into A100 | Open source

Apr 29, 2024 pm 04:55 PM

FP8 and lower floating point quantification precision are no longer the "patent" of H100! Lao Huang wanted everyone to use INT8/INT4, and the Microsoft DeepSpeed team started running FP6 on A100 without official support from NVIDIA. Test results show that the new method TC-FPx's FP6 quantization on A100 is close to or occasionally faster than INT4, and has higher accuracy than the latter. On top of this, there is also end-to-end large model support, which has been open sourced and integrated into deep learning inference frameworks such as DeepSpeed. This result also has an immediate effect on accelerating large models - under this framework, using a single card to run Llama, the throughput is 2.65 times higher than that of dual cards. one

How to remove the write protection of a USB flash drive? Several simple and effective methods can help you do it

May 02, 2024 am 09:04 AM

How to remove the write protection of a USB flash drive? Several simple and effective methods can help you do it

May 02, 2024 am 09:04 AM

U disk is one of the commonly used storage devices in our daily work and life, but sometimes we encounter situations where the U disk is write-protected and cannot write data. This article will introduce several simple and effective methods to help you quickly remove the write protection of the USB flash drive and restore the normal use of the USB flash drive. Tool materials: System version: Windows1020H2, macOS BigSur11.2.3 Brand model: SanDisk UltraFlair USB3.0 flash drive, Kingston DataTraveler100G3USB3.0 flash drive Software version: DiskGenius5.4.2.1239, ChipGenius4.19.1225 1. Check the physical write protection switch of the USB flash drive on some USB flash drives Designed with

What does mysql database do?

Apr 22, 2024 pm 06:12 PM

What does mysql database do?

Apr 22, 2024 pm 06:12 PM

MySQL is a relational database management system that provides the following main functions: Data storage and management: Create and organize data, supporting various data types, primary keys, foreign keys, and indexes. Data query and retrieval: Use SQL language to query, filter and retrieve data, and optimize execution plans to improve efficiency. Data updates and modifications: Add, modify or delete data through INSERT, UPDATE, DELETE commands, supporting transactions to ensure consistency and rollback mechanisms to undo changes. Database management: Create and modify databases and tables, back up and restore data, and provide user management and permission control.

What is the API interface for?

Apr 23, 2024 pm 01:51 PM

What is the API interface for?

Apr 23, 2024 pm 01:51 PM

An API interface is a specification for interaction between software components and is used to implement communication and data exchange between different applications or systems. The API interface acts as a "translator", converting the developer's instructions into computer language so that the applications can work together. Its advantages include convenient data sharing, simplified development, improved performance, enhanced security, improved productivity and interoperability.

What does schema mean in mysql

May 01, 2024 pm 08:33 PM

What does schema mean in mysql

May 01, 2024 pm 08:33 PM

Schema in MySQL is a logical structure used to organize and manage database objects (such as tables, views) to ensure data consistency, data access control and simplify database design. The functions of Schema include: 1. Data organization; 2. Data consistency; 3. Data access control; 4. Database design.

Redis cache implementation principle

Apr 19, 2024 pm 10:36 PM

Redis cache implementation principle

Apr 19, 2024 pm 10:36 PM

The Redis caching mechanism is implemented through key-value storage, memory storage, expiration policies, data structures, replication, and persistence. It follows the steps of obtaining data, cache hit, cache miss, writing to cache, and updating cache to provide fast data access and high-performance caching services.

Usage of service layer in java

May 07, 2024 am 04:24 AM

Usage of service layer in java

May 07, 2024 am 04:24 AM

The Service layer in Java is responsible for business logic and business rules for executing applications, including processing business rules, data encapsulation, centralizing business logic and improving testability. In Java, the Service layer is usually designed as an independent module, interacts with the Controller and Repository layers, and is implemented through dependency injection, following steps such as creating an interface, injecting dependencies, and calling Service methods. Best practices include keeping it simple, using interfaces, avoiding direct manipulation of data, handling exceptions, and using dependency injection.