AMD Zen 5 execution engine exposed: using true 512-bit FPU

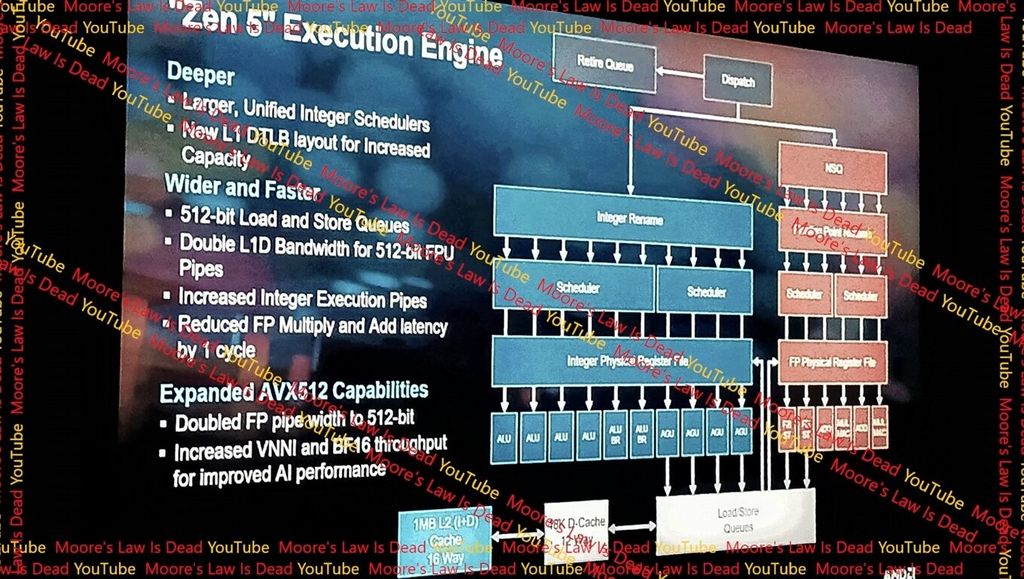

According to news from this site on April 5, the source Moore's Law is Dead shared information about the AMD Zen 5 processor execution engine (Execution Engine) in the latest video, saying that it will use a true 512-bit Floating point unit (FPU).

According to the slides shared by the source, Zen 5’s execution engine is described in detail, using a true 512-bit FPU.

AMD Zen 4 processor uses a dual-channel 256-bit FPU when executing AVX-512 instruction workload, while Zen 5 uses a real 512-bit FPU to process 512-bit There will be higher performance in terms of AVX or VNNI instructions.

This site also learned from the report that AMD has upgraded relevant components for the 512-bit FPU, increased the capacity of L1 DTLB, expanded the load-store queue, and doubled the bandwidth of the L1 data cache. Size increased by 50%. The size of L1D has increased from 32 KB in "Zen 4" to 48 KB now.

FPU MADD latency reduced by 1 cycle. In addition to the FPU, AMD has increased the number of Integer execution pipes from 8 (Zen 4) to 10, and the exclusive L2 cache size per core is still 1 MB.

The above is the detailed content of AMD Zen 5 execution engine exposed: using true 512-bit FPU. For more information, please follow other related articles on the PHP Chinese website!

Hot AI Tools

Undresser.AI Undress

AI-powered app for creating realistic nude photos

AI Clothes Remover

Online AI tool for removing clothes from photos.

Undress AI Tool

Undress images for free

Clothoff.io

AI clothes remover

Video Face Swap

Swap faces in any video effortlessly with our completely free AI face swap tool!

Hot Article

Hot Tools

Notepad++7.3.1

Easy-to-use and free code editor

SublimeText3 Chinese version

Chinese version, very easy to use

Zend Studio 13.0.1

Powerful PHP integrated development environment

Dreamweaver CS6

Visual web development tools

SublimeText3 Mac version

God-level code editing software (SublimeText3)

Hot Topics

ASUS unveils Adol Book 14 Air with AMD Ryzen 9 8945H and curious incense dispenser

Aug 01, 2024 am 11:12 AM

ASUS unveils Adol Book 14 Air with AMD Ryzen 9 8945H and curious incense dispenser

Aug 01, 2024 am 11:12 AM

ASUS already offers various 14-inch laptops, including the Zenbook 14 OLED (curr. $1,079.99 on Amazon). Now, it has decided to introduce the Adol Book 14 Air, which looks like a typical 14-inch laptop on the face of it. However, an inconspicuous meta

AMD Radeon RX 7800M in OneXGPU 2 outperforms Nvidia RTX 4070 Laptop GPU

Sep 09, 2024 am 06:35 AM

AMD Radeon RX 7800M in OneXGPU 2 outperforms Nvidia RTX 4070 Laptop GPU

Sep 09, 2024 am 06:35 AM

OneXGPU 2 is the first eGPUto feature the Radeon RX 7800M, a GPU that even AMD hasn't announced yet. As revealed by One-Netbook, the manufacturer of the external graphics card solution, the new AMD GPU is based on RDNA 3 architecture and has the Navi

Ryzen AI software gets support for new Strix Halo and Kraken Point AMD Ryzen processors

Aug 01, 2024 am 06:39 AM

Ryzen AI software gets support for new Strix Halo and Kraken Point AMD Ryzen processors

Aug 01, 2024 am 06:39 AM

AMD Strix Point laptopshave just hit the market, and the next-gen Strix Halo processors are expected to be released sometime next year. However, the company has already added support for the Strix Halo and Krackan Point APUs to its Ryzen AI software.

AMD Z2 Extreme chip for handheld consoles tipped for an early 2025 launch

Sep 07, 2024 am 06:38 AM

AMD Z2 Extreme chip for handheld consoles tipped for an early 2025 launch

Sep 07, 2024 am 06:38 AM

Even though AMD tailor-made the Ryzen Z1 Extreme (and its non-Extreme variant) for handheld consoles, the chip only ever found itself in two mainstream handhelds, the Asus ROG Ally (curr. $569 on Amazon) and Lenovo Legion Go (three if you count the R

First Minisforum mini PC with Ryzen AI 9 HX 370 rumored to launch with high price tag

Sep 29, 2024 am 06:05 AM

First Minisforum mini PC with Ryzen AI 9 HX 370 rumored to launch with high price tag

Sep 29, 2024 am 06:05 AM

Aoostar was among the first to announce a Strix Point mini PC, and later, Beelink launched the SER9with a soaring starting price tag of $999. Minisforum joined the party by teasingthe EliteMini AI370, and as the name suggests, it will be the company'

AMD announces 'Sinkclose' high-severity vulnerability, affecting millions of Ryzen and EPYC processors

Aug 10, 2024 pm 10:31 PM

AMD announces 'Sinkclose' high-severity vulnerability, affecting millions of Ryzen and EPYC processors

Aug 10, 2024 pm 10:31 PM

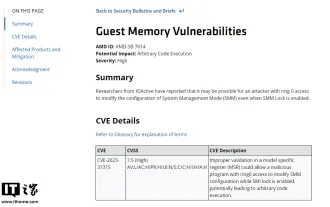

According to news from this site on August 10, AMD officially confirmed that some EPYC and Ryzen processors have a new vulnerability called "Sinkclose" with the code "CVE-2023-31315", which may involve millions of AMD users around the world. So, what is Sinkclose? According to a report by WIRED, the vulnerability allows intruders to run malicious code in "System Management Mode (SMM)." Allegedly, intruders can use a type of malware called a bootkit to take control of the other party's system, and this malware cannot be detected by anti-virus software. Note from this site: System Management Mode (SMM) is a special CPU working mode designed to achieve advanced power management and operating system independent functions.

Deal | Lenovo ThinkPad P14s Gen 5 with 120Hz OLED, 64GB RAM and AMD Ryzen 7 Pro is 60% off right now

Sep 07, 2024 am 06:31 AM

Deal | Lenovo ThinkPad P14s Gen 5 with 120Hz OLED, 64GB RAM and AMD Ryzen 7 Pro is 60% off right now

Sep 07, 2024 am 06:31 AM

Many students are going back to school these days, and some may notice that their old laptop isn't up to the task anymore. Some college students might even be in the market for a high-end business notebook with a gorgeous OLED screen, in which case t

Beelink SER9: Compact AMD Zen 5 mini-PC announced with Radeon 890M iGPU but limited eGPU options

Sep 12, 2024 pm 12:16 PM

Beelink SER9: Compact AMD Zen 5 mini-PC announced with Radeon 890M iGPU but limited eGPU options

Sep 12, 2024 pm 12:16 PM

Beelink continues to introduce new mini-PCs and accompanying accessories at a rate of knots. To recap, little over a month has passed since it released the EQi12, EQR6 and the EX eGPU dock. Now, the company has turned its attention to AMD's new Strix