Combien coûte le trfc ?

La valeur TRFC appartient au deuxième petit paramètre, qui représente la période d'intervalle de rafraîchissement. L'unité est le cycle. Plus la valeur est petite, mieux c'est. .

La mémoire DDR3 a généralement une valeur de 90 à 120. En dessous de 80, cela peut provoquer une instabilité. CL, tRCD, tRP et tRAS sont appelés premiers timings et ont l'impact le plus évident et le plus important sur les performances des particules. (Apprentissage recommandé : phpstorm)

Tout d'abord, les timings de mémoire (anglais : Memory timings ou RAM timings) sont quatre paramètres qui décrivent les performances de la mémoire vive dynamique synchrone (SDRAM) : CL, TRCD, TRP et TRAS, l'unité est le cycle d'horloge.

Il est clair que pour que l'ordinateur fonctionne de manière ordonnée, il existe des exigences strictes concernant le temps de génération, le temps de stabilisation, le temps d'annulation et la relation mutuelle des différents signaux de fonctionnement.

L'application d'un contrôle temporel au signal de fonctionnement est appelée contrôle temporel. Seul un contrôle temporel strict peut garantir un système informatique organique doté de divers composants fonctionnels.

Facteurs affectant la synchronisation de la mémoire :

Lors de la conversion de la synchronisation de la mémoire en latence réelle, la chose la plus importante à noter est qu'elle est exprimée en unités de cycles d'horloge. Sans connaître la durée d'un cycle d'horloge, il est impossible de savoir si un ensemble de nombres est plus rapide qu'un autre.

Par exemple, la fréquence d'horloge de la mémoire DDR3-2000 est de 1 000 MHz et sa période d'horloge est de 1 ns. Sur la base de cette horloge de 1 ns, CL=7 donne un retard absolu de 7 ns.

La DDR3-2666 plus rapide (horloge 1333 MHz, 0,75 ns par cycle) peut utiliser un CL=9 plus grand, mais le délai absolu résultant de 6,75 ns est plus court.

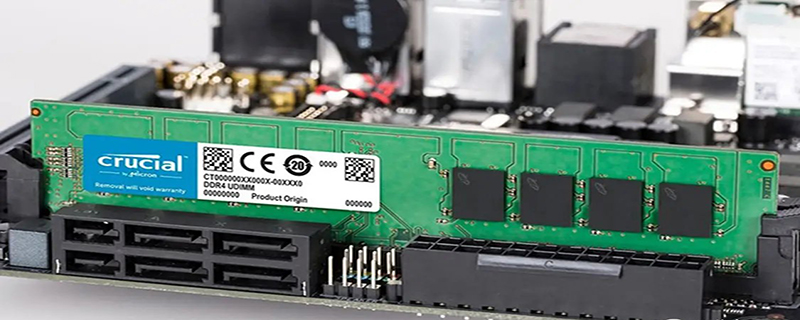

Les DIMM modernes incluent une puce ROM de détection de présence en série (SPD) qui contient les durées de mémoire recommandées pour la configuration automatique.

Le BIOS du PC peut permettre à l'utilisateur d'ajuster les timings pour améliorer les performances (au risque de réduire la stabilité), ou dans certains cas, d'augmenter la stabilité (comme en utilisant les timings recommandés).

Remarque : la bande passante mémoire est une mesure du débit mémoire et est généralement limitée par le taux de transfert plutôt que par la latence.

En entrelaçant l'accès à plusieurs banques internes de SDRAM, il est possible de transférer en continu aux taux de pointe. Une bande passante accrue peut se faire au détriment d’une latence accrue.

Concrètement, chaque nouvelle génération de mémoire DDR a un taux de transfert plus élevé, mais la latence absolue ne change pas de manière significative, en particulier les premiers produits de nouvelle génération du marché, qui ont généralement des taux de transfert plus élevés que la génération précédente. Long retard

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!

Outils d'IA chauds

Undresser.AI Undress

Application basée sur l'IA pour créer des photos de nu réalistes

AI Clothes Remover

Outil d'IA en ligne pour supprimer les vêtements des photos.

Undress AI Tool

Images de déshabillage gratuites

Clothoff.io

Dissolvant de vêtements AI

AI Hentai Generator

Générez AI Hentai gratuitement.

Article chaud

Outils chauds

Bloc-notes++7.3.1

Éditeur de code facile à utiliser et gratuit

SublimeText3 version chinoise

Version chinoise, très simple à utiliser

Envoyer Studio 13.0.1

Puissant environnement de développement intégré PHP

Dreamweaver CS6

Outils de développement Web visuel

SublimeText3 version Mac

Logiciel d'édition de code au niveau de Dieu (SublimeText3)

Sujets chauds

Version Web Deepseek Entrée officielle

Mar 12, 2025 pm 01:42 PM

Version Web Deepseek Entrée officielle

Mar 12, 2025 pm 01:42 PM

La profondeur domestique de l'IA Dark Horse a fortement augmenté, choquant l'industrie mondiale de l'IA! Cette société chinoise de renseignement artificiel, qui n'a été créée que depuis un an et demi, a gagné des éloges des utilisateurs mondiaux pour ses maquettes gratuites et open source, Deepseek-V3 et Deepseek-R1. Deepseek-R1 est désormais entièrement lancé, avec des performances comparables à la version officielle d'Openaio1! Vous pouvez vivre ses fonctions puissantes sur la page Web, l'application et l'interface API. Méthode de téléchargement: prend en charge les systèmes iOS et Android, les utilisateurs peuvent le télécharger via l'App Store; Version Web Deepseek Entrée officielle: HT

Recherche approfondie Entrée du site officiel Deepseek

Mar 12, 2025 pm 01:33 PM

Recherche approfondie Entrée du site officiel Deepseek

Mar 12, 2025 pm 01:33 PM

Au début de 2025, l'IA domestique "Deepseek" a fait un début magnifique! Ce modèle d'IA gratuit et open source a une performance comparable à la version officielle d'OpenAI d'Openai, et a été entièrement lancé sur le côté Web, l'application et l'API, prenant en charge l'utilisation multi-terminale des versions iOS, Android et Web. Recherche approfondie du site officiel de Deepseek et du guide d'utilisation: Adresse officielle du site Web: https://www.deepseek.com/using étapes pour la version Web: cliquez sur le lien ci-dessus pour entrer le site officiel Deepseek. Cliquez sur le bouton "Démarrer la conversation" sur la page d'accueil. Pour la première utilisation, vous devez vous connecter avec votre code de vérification de téléphone mobile. Après vous être connecté, vous pouvez entrer dans l'interface de dialogue. Deepseek est puissant, peut écrire du code, lire des fichiers et créer du code

Comment résoudre le problème des serveurs occupés pour Deepseek

Mar 12, 2025 pm 01:39 PM

Comment résoudre le problème des serveurs occupés pour Deepseek

Mar 12, 2025 pm 01:39 PM

Deepseek: Comment gérer l'IA populaire qui est encombré de serveurs? En tant qu'IA chaude en 2025, Deepseek est gratuit et open source et a une performance comparable à la version officielle d'Openaio1, qui montre sa popularité. Cependant, une concurrence élevée apporte également le problème de l'agitation du serveur. Cet article analysera les raisons et fournira des stratégies d'adaptation. Entrée de la version Web Deepseek: https://www.deepseek.com/deepseek serveur Raison: Accès simultané: des fonctionnalités gratuites et puissantes de Deepseek attirent un grand nombre d'utilisateurs à utiliser en même temps, ce qui entraîne une charge de serveur excessive. Cyber Attack: Il est rapporté que Deepseek a un impact sur l'industrie financière américaine.