Quelle est la vitesse maximale du pcie3.0x4

La vitesse maximale théorique de lecture ou d'écriture du PCIe3.0x4 est de 4 Go/s. Quelle que soit la surcharge du protocole, il peut transmettre 4 Go/4K IO par seconde. La valeur est de 1 Mo, ce qui signifie que l'IOPS maximum théorique est de 1 000 K. Par conséquent, quel que soit le support utilisé dans la couche sous-jacente d'un SSD, qu'il s'agisse de Flash ou de Xpoint 3D, la vitesse de l'interface est limitée et les IOPS maximales ne peuvent pas dépasser cette valeur.

L'environnement d'exploitation de ce tutoriel : système Windows 7, ordinateur Dell G3.

Introduction à l'interface PCIe

PCIe s'est développé jusqu'à présent et la vitesse est plus rapide que la génération précédente.

Dans la ligne Link width, on voit X1, X2, X4..., qu'est-ce que cela signifie ? Il s'agit du nombre de voies (Lane) de la connexion PCIe. Tout comme les autoroutes, il existe des voies simples, 2 voies et 4 voies. Cependant, les autoroutes à 8 voies ou plus ne sont pas courantes, mais le PCIe peut avoir jusqu'à 32 voies.

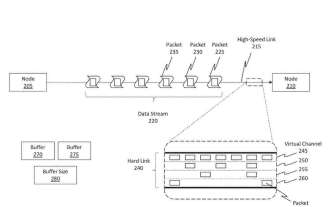

La connexion PCIe entre deux appareils est appelée un lien, comme le montre la figure ci-dessous :

De A à B, il existe une connexion bidirectionnelle. La voiture peut conduire de A à B. En même temps, la voiture Vous pouvez également conduire de B à A et suivre votre propre chemin. Il existe des canaux d'envoi et de réception dédiés entre deux périphériques PCIe, et les données peuvent être transmises dans les deux sens en même temps. Les spécifications PCIe appellent ce mode de fonctionnement mode double simplex, qui peut être compris comme mode duplex intégral.

Quel est le mode de fonctionnement du SATA ?

Comme PCIe, SATA dispose également de canaux d'envoi et de réception indépendants, mais il est différent du mode de fonctionnement PCIe : en même temps, un seul canal peut transmettre des données, c'est-à-dire que vous envoyez des données sur un seul. canal, et une autre donnée ne peut pas être reçue sur une voie et vice versa. Ce mode de travail doit être le mode semi-duplex. PCIe est comme notre téléphone mobile, les deux parties peuvent parler en même temps, tandis que SATA est comme un talkie-walkie. Lorsqu'une personne parle, l'autre ne peut qu'écouter mais pas parler.

Retournez au tableau précédent de la bande passante PCIe. La bande passante ci-dessus, telle que PCIe3.0x1, a une bande passante de 2 Go/s, qui fait référence à la bande passante bidirectionnelle, c'est-à-dire la bande passante de lecture et d'écriture. S'il s'agit uniquement de lecture ou d'écriture, la valeur doit être réduite de moitié, c'est-à-dire une vitesse de lecture ou d'écriture de 1 Go/s.

Voyons comment la bande passante dans le tableau est calculée.

PCIe est un bus série. Le taux de transmission des bits en ligne du PCIe1.0 est de 2,5 Gb/s. La couche physique utilise un codage 8/10, c'est-à-dire que 8 bits de données doivent être transmis. sur la ligne physique. Par conséquent :

PCIe1.0 x 1的带宽=(2.5Gb/s x 2(双向通道))/ 10bit = 0.5GB/s

C'est la bande passante d'une seule voie. S'il y a plusieurs voies, alors la bande passante totale est de 0,5 Go/s multipliée par le nombre de voies.

Le taux de transmission de bits en ligne de PCIe2.0 a doublé sur la base de PCIe1.0 à 5 Gb/s. La couche physique utilise également un codage 8/10, donc :

PCIe2.0 x 1的带宽=(5Gb/s x 2(双向通道))/ 10bit = 1GB/s

De même, combien de voies y a-t-il, la bande passante est de 1 Go. /s multiplié par le nombre de voies.

Le débit de transmission de bits en ligne de PCIe3.0 n'a pas doublé par rapport à PCIe2.0, ce n'est pas 10 Gb/s, mais 8 Gb/s, mais la couche physique utilise un encodage 128/130 pour la transmission de données, donc :

PCIe3.0 x 1的带宽=(8Gb/s x 2(双向通道))/ 8bit = 2GB/s

De même, la bande passante est de 2 Go/s multiplié par le nombre de voies.

En raison de l'utilisation du codage 128/130, les données 128 bits n'ajoutent que 2 bits supplémentaires et le taux de transmission de données effectif augmente. Bien que le débit de transmission de bits en ligne ne double pas, la bande passante effective des données reste dans les limites. PCIe2.0 En gros, doublez-le.

Il convient de mentionner ici que la bande passante des données calculée ci-dessus a pris en compte l'encodage 8/10 ou 128/130. Par conséquent, lors du calcul de la bande passante, il n'est pas nécessaire de prendre en compte l'encodage en ligne.

Contrairement au canal unique SATA, la connexion PCIe peut étendre la bande passante en augmentant le nombre de canaux, ce qui est plein de flexibilité. Plus le nombre de canaux est élevé, plus la vitesse est rapide. Cependant, plus le nombre de canaux est élevé, plus le coût est élevé, prend plus de place et consomme plus d'énergie. Par conséquent, le nombre de canaux à utiliser doit être une considération globale entre les performances et d’autres facteurs. En ne considérant que les performances, la bande passante maximale du PCIe peut atteindre 64 Go/s, et la bande passante correspondant au PCIe 3.0 x 32 est un chiffre terrifiant. Cependant, les SSD d'interface PCIe existants utilisent généralement jusqu'à 4 canaux, tels que PCIe3.0x4, avec une bande passante bidirectionnelle de 8 Go/s et une bande passante en lecture ou en écriture de 4 Go/s.

Avec une vitesse de transfert de plusieurs Go/s, lire et écrire des petits films est toute une prouesse.

Ici, calculons le maximum théorique d'IOPS 4K de PCIe3.0x4. La vitesse de lecture ou d'écriture maximale théorique du PCIe3.0x4 est de 4 Go/s. Quelle que soit la surcharge du protocole, il peut transmettre 4 Go/4K IOS par seconde. Cette valeur est de 1 Mo, ce qui signifie que l'IOPS maximum théorique est de 1 000 K. Par conséquent, pour un SSD, quel que soit le support que vous utilisez en bas, qu'il s'agisse de flash ou de xpoint 3D, la vitesse de l'interface est très faible et les IOPS maximales ne peuvent pas dépasser cette valeur.

PCIe est développé à partir de PCI Le « e » de PCIe est l'abréviation d'express, qui signifie rapide. Comment le PCIe peut-il être plus rapide que le PCI (ou PCI-X) ? PCIe est fondamentalement différent de PCI en termes de transmission physique : PCI utilise un port parallèle pour transmettre les données, tandis que PCIe utilise une transmission par port série. Mon bus parallèle PCI peut transmettre 32 bits ou 64 bits en un seul cycle d'horloge. Pourquoi ne peut-il pas être comparé à votre bus série qui transmet 1 bit de données en un seul cycle d'horloge ?

Lorsque la fréquence d'horloge réelle est relativement basse, le port parallèle est en effet plus rapide que le port série car il peut transmettre plusieurs bits en même temps. Avec le développement de la technologie, le taux de transmission des données doit être de plus en plus rapide, et la fréquence d'horloge doit également être de plus en plus rapide. Cependant, la fréquence d'horloge du bus parallèle ne peut pas être aussi rapide que vous le souhaitez.

Du côté de l'envoi, les données sont transmises sur un certain front d'horloge (le premier front montant de l'horloge à gauche), et du côté de la réception, les données sont reçues sur le front d'horloge suivant (le deuxième front montant de l'horloge à gauche). bord de l'horloge à droite). Par conséquent, pour collecter correctement les données à l’extrémité réceptrice, le cycle d’horloge doit être supérieur au temps de transmission des données (temps de vol de l’extrémité émettrice à l’extrémité réceptrice). Limitée par le temps de transmission des données (qui augmente également à mesure que la longueur de la ligne de données augmente), la fréquence d'horloge ne peut pas être trop élevée. De plus, lorsque le signal d'horloge est transmis en ligne, il y aura également un décalage de phase (décalage d'horloge), qui affecte la collecte de données à l'extrémité réceptrice. De plus, en transmission parallèle, l'extrémité réceptrice doit attendre le bit de données le plus lent ; pour arriver avant qu'il ne puisse verrouiller l'intégralité des données (désalignement du signal).

PCIe n'a pas ces problèmes lors de l'utilisation d'un bus série pour la transmission de données. Il n'a pas de signal d'horloge externe. Ses informations d'horloge sont intégrées dans le flux de données via un codage 8/10 ou 128/130. L'extrémité réceptrice peut récupérer les informations d'horloge du flux de données. Par conséquent, elle n'est pas limitée par la transmission de données. temps en ligne. Vous Peu importe la longueur du fil ou la vitesse de transmission de vos données ; sans signal d'horloge externe, il n'y a naturellement pas de problème de décalage d'horloge puisqu'il s'agit uniquement d'une transmission série ; un bit est transmis, il n'y a donc pas de problème de distorsion du signal. Cependant, si plusieurs voies sont utilisées pour transmettre des données (il y a du parallélisme en série, haha), le problème revient, car le destinataire doit également attendre que les données sur la voie la plus lente arrivent avant de pouvoir traiter l'intégralité des données.

Connaissance de base du bus PCIe

Différent du bus PCIe, le bus PCIe utilise une méthode de connexion de bout en bout. Un seul appareil peut être connecté aux deux extrémités d'une liaison PCIe. sont des données l'une pour l'autre. En plus des liaisons de bus, le bus PCIe comporte également plusieurs couches. L'expéditeur passera par ces couches lors de l'envoi de données, et le destinataire utilisera également ces couches lors de la réception des données. La structure hiérarchique utilisée par le bus PCIe est similaire à la pile de protocoles réseau.

La liaison PCIe utilise une « méthode de transmission de données de bout en bout ». L'extrémité émettrice et l'extrémité réceptrice contiennent toutes deux TX (logique de transmission) et RX (logique de réception), et leur structure est celle indiquée sur la figure.

Comme le montre la figure ci-dessus, dans un chemin de données (Lane) de la liaison physique du bus PCIe, il y a deux ensembles de signaux différentiels, soit un total de 4 lignes de signaux. Le composant TX à l'extrémité émettrice et le composant RX à l'extrémité réceptrice sont connectés à l'aide d'un ensemble de signaux différentiels. Cette liaison est également appelée liaison émettrice à l'extrémité émettrice et est également la liaison réceptrice à l'extrémité réceptrice ; Le composant à l'extrémité émettrice et le composant TX à l'extrémité réceptrice utilisent un autre ensemble de signaux différentiels. Un groupe de connexions de signaux différentiels, cette liaison est également appelée liaison de réception à l'extrémité de l'expéditeur et est également la liaison de transmission à l'extrémité du récepteur. Une liaison PCIe peut être composée de plusieurs voies.

La spécification électrique pour les signaux différentiels à grande vitesse exige qu'un condensateur soit connecté en série à l'extrémité de transmission pour le couplage CA. Ce condensateur est également appelé condensateur de couplage AC. La liaison PCIe utilise des signaux différentiels pour la transmission de données. Un signal différentiel se compose de deux signaux, D+ et D-. L'extrémité réceptrice du signal compare la différence entre les deux signaux pour déterminer si l'extrémité émettrice envoie un « 1 » logique ou un « logique ». 0" ".

Par rapport aux signaux asymétriques, les signaux différentiels sont plus résistants aux interférences, car les signaux différentiels nécessitent une « longueur égale », une « largeur égale », une « proximité étroite » pendant le câblage et sont sur la même couche. Par conséquent, le bruit parasite externe sera chargé sur les deux signaux D+ et D- à la même valeur et en même temps. La différence est de 0 dans des circonstances idéales, ce qui aura peu d'impact sur la valeur logique du signal. La signalisation différentielle peut donc utiliser des fréquences de bus plus élevées.

De plus, l'utilisation de signaux différentiels peut supprimer efficacement les interférences électromagnétiques (EMI). Parce que les signaux différentiels D+ et D- sont très proches et ont une amplitude de signal égale et une polarité opposée. L'amplitude du champ électromagnétique couplé entre ces deux fils et le fil de terre est égale et s'annulera, de sorte que le signal différentiel provoque moins d'interférences électromagnétiques avec le monde extérieur. Bien entendu, les inconvénients des signaux différentiels sont également évidents. Premièrement, les signaux différentiels utilisent deux signaux pour transmettre un bit de données. Deuxièmement, le câblage des signaux différentiels est relativement strict.

Le lien PCIe peut être composé de plusieurs voies. Actuellement, le lien PCIe peut prendre en charge 1, 2, 4, 8, 12, 16 et 32 voies, à savoir ×1, ×2, ×4, ×8, ×12, ×16. et des liaisons PCIe de largeur ×32. La fréquence du bus utilisée sur chaque Lane est liée à la version du bus PCIe utilisée.

La première spécification de bus PCIe est V1.0, suivie de V1.0a, V1.1, V2.0 et V2.1. La dernière spécification du bus PCIe est actuellement la V2.1, tandis que la V3.0 est en cours de développement et devrait être publiée en 2010. Différentes spécifications de bus PCIe définissent différentes fréquences de bus et méthodes de codage de liaison, comme indiqué dans le tableau 41.

La relation entre la spécification du bus PCIe, la fréquence et l'encodage du bus

| Spécification du bus PCIe | Fréquence du bus [1] | Bande passante maximale d'une seule voie | Méthode d'encodage |

|---|---|---|---|

| 1. x | 1,25 GHz | 2,5GT/s | 8/10b encodage |

| 2.x | 2,5GHz | 5GT/s | 8/10b encodage |

| 3.0 | 4GHz | 8GT /s | Encodage 128/130b |

Comme le montre le tableau ci-dessus, différentes spécifications de bus PCIe utilisent différentes fréquences de bus et différentes méthodes d'encodage de données. Les spécifications du bus PCIe V1.x et V2.0 utilisent un codage 8/10b dans la couche physique, c'est-à-dire que 10 bits sur la liaison PCIe contiennent 8 bits de données valides tandis que la spécification V3.0 utilise un codage 128/130b ; Les 130 bits de la liaison PCIe contiennent 128 bits de données valides.

Comme le montre le tableau ci-dessus, bien que la fréquence du bus utilisée par la spécification V3.0 ne soit que de 4 GHz, sa bande passante effective est le double de celle de la V2.x. Ce qui suit prendra la spécification V2.x comme exemple pour illustrer la bande passante maximale que les liaisons PCIe de différentes largeurs peuvent fournir, comme indiqué dans le tableau 42.

Bande passante maximale du bus PCIe

| Largeur en bits de données du bus PCIe | ×1 | ×2 | ×4 | ×8 | ×12 | ×16 | × 32 |

|---|---|---|---|---|---|---|---|

| Bande passante maximale (GT/s) | 5 | 10 | 20 | 40 | 60 | 80 | 160 |

Comme indiqué dans le tableau ci-dessus, ×32 La liaison PCIe peut Fournit une bande passante de liaison de 160 GT/s, ce qui est bien supérieur à la bande passante maximale fournie par le bus PCI/PCI-X. La prochaine spécification PCIe V3.0 utilise une fréquence de bus de 4 GHz, ce qui augmentera encore la bande passante maximale de la liaison PCIe.

Dans le bus PCIe, utilisez GT (Gigatransfer) pour calculer la bande passante maximale de la liaison PCIe. GT est la bande passante maximale transmise sur la liaison PCIe et sa formule de calcul est la fréquence du bus × la largeur des bits de données × 2.

Dans le bus PCIe, de nombreux facteurs affectent la bande passante effective, sa bande passante effective est donc difficile à calculer. Malgré cela, la bande passante effective fournie par le bus PCIe reste bien supérieure à celle du bus PCI. Le bus PCIe a également ses faiblesses, la plus importante étant la latence de transmission.

La liaison PCIe utilise le mode série pour la transmission des données. Cependant, à l'intérieur de la puce, le bus de données est toujours parallèle, donc l'interface de liaison PCIe doit effectuer une conversion série-parallèle entraînera une conversion série-parallèle importante. retard. De plus, les paquets de données sur le bus PCIe doivent passer par la couche de transaction, la couche de liaison de données et la couche physique. Ces paquets de données entraîneront également des retards lors du passage à travers ces couches.

Parmi les périphériques basés sur un bus PCIe, les liaisons PCIe ×1 sont les plus courantes, tandis que les liaisons PCIe ×12 sont rares, et les périphériques PCIe ×4 et ×8 sont également rares. Intel intègre généralement plusieurs liaisons PCIe ×1 dans l'ICH pour connecter des périphériques basse vitesse, et intègre une liaison PCIe ×16 dans le MCH pour connecter le contrôleur de la carte graphique. Les processeurs PowerPC prennent généralement en charge les liaisons PCIe ×8, ×4, ×2 et ×1.

La transmission de données entre les liaisons physiques du bus PCIe utilise un mécanisme de transmission synchrone basé sur l'horloge, mais il n'y a pas de ligne d'horloge sur la liaison physique. L'extrémité réceptrice du bus PCIe contient un module de récupération d'horloge CDR (Clock Data Recovery), et le CDR recevra le L'horloge de réception est extraite du message pour effectuer une transmission de données synchrone.

Il convient de noter que dans un périphérique PCIe, en plus d'extraire l'horloge du paquet, les paires de signaux REFCLK+ et REFCLK- sont également utilisées comme horloge de référence locale

Pour plus de connaissances connexes, veuillez visiter la FAQ colonne!

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!

Outils d'IA chauds

Undresser.AI Undress

Application basée sur l'IA pour créer des photos de nu réalistes

AI Clothes Remover

Outil d'IA en ligne pour supprimer les vêtements des photos.

Undress AI Tool

Images de déshabillage gratuites

Clothoff.io

Dissolvant de vêtements AI

AI Hentai Generator

Générez AI Hentai gratuitement.

Article chaud

Outils chauds

Bloc-notes++7.3.1

Éditeur de code facile à utiliser et gratuit

SublimeText3 version chinoise

Version chinoise, très simple à utiliser

Envoyer Studio 13.0.1

Puissant environnement de développement intégré PHP

Dreamweaver CS6

Outils de développement Web visuel

SublimeText3 version Mac

Logiciel d'édition de code au niveau de Dieu (SublimeText3)

Veuillez éteindre l'alimentation et connecter le câble d'alimentation PCIe

Feb 19, 2024 am 11:09 AM

Veuillez éteindre l'alimentation et connecter le câble d'alimentation PCIe

Feb 19, 2024 am 11:09 AM

Si vous voyez le message d'erreur Veuillez éteindre et connecter le câble d'alimentation PCIe sur votre PC Windows 11/10, veuillez lire cet article pour savoir comment résoudre le problème. Cette erreur peut être déclenchée lorsqu'un périphérique PCIe (généralement une carte graphique) ne parvient pas à recevoir suffisamment d'énergie. Les causes possibles incluent un câble d'alimentation PCIe défectueux, des problèmes de connexion ou une alimentation insuffisante. Ce problème peut également survenir si le cordon d'alimentation n'est pas correctement connecté. Veuillez éteindre l'alimentation et connecter le(s) câble(s) d'alimentation PCIE de cette carte graphique. Les nouveaux utilisateurs de PC ou les personnes manquant d'expérience dans l'assemblage de systèmes informatiques rencontrent souvent ce problème. Ce message d'erreur peut également apparaître si le câble PCIe se desserre en raison des vibrations ou du temps. Cet article explique les étapes à suivre pour résoudre ce problème

Les interfaces pcie4.0 et pcie3.0 sont-elles identiques ?

Mar 13, 2023 pm 04:39 PM

Les interfaces pcie4.0 et pcie3.0 sont-elles identiques ?

Mar 13, 2023 pm 04:39 PM

Les interfaces pcie4.0 et pcie3.0 sont différentes. Ce sont deux versions différentes de la norme PCIe. La différence entre les deux : 1. PCIe 4.0 offre une vitesse de transmission de données plus rapide, jusqu'à 16 GT/s, soit le double de celle de PCIe 3.0 ; 2. PCIe 4.0 prend en charge plus de bande passante, jusqu'à 69,6 Go/s uniquement. prend en charge jusqu'à 32 Go/s ; 3. PCIe4.0 prend en charge plus de canaux et peut prendre en charge plus de périphériques ; 4. PCIe4.0 prend en charge une consommation d'énergie inférieure ;

Retardé d'un an, le déploiement de la spécification PCIe 6.0/7.0 rencontre des obstacles

Jun 15, 2024 pm 04:45 PM

Retardé d'un an, le déploiement de la spécification PCIe 6.0/7.0 rencontre des obstacles

Jun 15, 2024 pm 04:45 PM

Selon les informations de ce site le 15 juin, le groupe d'intérêt spécial sur l'interconnexion des composants périphériques (PCI-SIG) a organisé cette semaine la conférence des développeurs 2024 et a annoncé les derniers progrès de PCIe6.0 et PCIe7.0, indiquant que bien que les deux normes ci-dessus Certains progrès ont été réalisés, mais l'adoption du déploiement est plus lente que prévu. PCI-SIG a actuellement reporté le lancement du « Compliance Program » (Compliance Program). Le test de cohérence préliminaire de PCIe6.0 devait initialement démarrer en mars de cette année, mais a été reporté au « deuxième trimestre », ce qui signifie il sera testé avant la fin de ce mois. Feuille de route de la version standard PCIe pour 2023 (en haut) et 2024 (en bas) L'agence a déclaré que des tests approfondis de conformité PCIe6.0 seraient effectués en 2020.

Quelle est la vitesse maximale du pcie3.0x4

Mar 15, 2023 pm 05:09 PM

Quelle est la vitesse maximale du pcie3.0x4

Mar 15, 2023 pm 05:09 PM

La vitesse de lecture ou d'écriture maximale théorique du PCIe3.0x4 est de 4 Go/s. Quelle que soit la surcharge du protocole, il peut transmettre 4 Go/4K IOS par seconde. Cette valeur est de 1 Mo, ce qui signifie que l'IOPS maximum théorique est de 1 000 K. Par conséquent, quel que soit le support utilisé dans la couche sous-jacente d'un SSD, qu'il s'agisse de Flash ou de Xpoint 3D, la vitesse de l'interface est limitée et les IOPS maximales ne peuvent pas dépasser cette valeur.

La première version officielle de la spécification PCIe 7.0 (version 0.5) a été annoncée et devrait être entièrement publiée l'année prochaine.

Apr 04, 2024 am 08:37 AM

La première version officielle de la spécification PCIe 7.0 (version 0.5) a été annoncée et devrait être entièrement publiée l'année prochaine.

Apr 04, 2024 am 08:37 AM

Selon les informations de ce site du 3 avril, PCI-SIG, l'organisation de développement des spécifications PCIe, a récemment annoncé la version 0.5 de la spécification PCIe7.0, c'est-à-dire que sa première version officielle a été publiée auprès des membres du PCI-SIG. Par rapport à la spécification PCIe6.0 publiée début 2022, la spécification PCIe7.0 double à nouveau le débit tout en continuant à utiliser la méthode de modulation du signal PAM4, atteignant un débit de données original de 128 GT/s et un débit bidirectionnel de 512 Go/s en configuration x16. .débit. Le développement de l'architecture PCIe7.0 se concentre sur l'amélioration des paramètres de canal, de la couverture et de l'efficacité énergétique, dans le but de fournir des applications gourmandes en données telles que l'Ethernet 800G, les charges de travail IA/ML, les centres de données à très grande échelle, le calcul haute performance, l'informatique quantique. l'informatique et le cloud.

Gamescom 2024 | Asus et MSI dévoilent des mécanismes innovants de dégagement rapide pour les GPU et les SSD M.2

Aug 25, 2024 am 06:30 AM

Gamescom 2024 | Asus et MSI dévoilent des mécanismes innovants de dégagement rapide pour les GPU et les SSD M.2

Aug 25, 2024 am 06:30 AM

À la Gamescom 2024, Asus et MSI ont vraiment fait tourner les têtes avec des mécanismes de dégagement rapide sympas pour les GPU et les SSD M.2. Ces nouvelles fonctionnalités visent à faciliter la vie des personnes qui construisent des PC, en particulier lorsqu'il s'agit de composants lourds. Asus rouleau

Que faire si le PCIe 6 chauffe ? Intel soumet un nouveau pilote et facilite le contrôle de la vitesse du bus

Jun 04, 2024 am 10:28 AM

Que faire si le PCIe 6 chauffe ? Intel soumet un nouveau pilote et facilite le contrôle de la vitesse du bus

Jun 04, 2024 am 10:28 AM

Selon les informations de ce site du 11 mai, les changements de version PCIe ont apporté une bande passante plus élevée, des vitesses de transmission plus rapides et ont également apporté plus de chaleur. Intel a récemment publié un pilote Linux qui utilise le « contrôleur de bande passante PCIe » open source pour réduire la chaleur et contrôler automatiquement la vitesse de la liaison lorsque la chaleur atteint un certain seuil. Remarque sur ce site : les modifications de la version PCIe augmentent non seulement la vitesse de transmission, mais nécessitent également une meilleure intégrité du signal et une perte de signal moindre. Elles nécessitent donc souvent des fréquences d'horloge plus élevées, une plus grande puissance et une optimisation du codage, ce qui entraînera des calories supplémentaires. L'ingénieur Intel Ilpo Järvinen a écrit dans les dernières notes de mise à jour : « Cette série de correctifs ajoute uniquement la prise en charge du contrôle de la vitesse des liaisons PCIe.

Amélioration de la transmission de liaison de données PCIe interne HoloLens : Microsoft partage des brevets AR/VR

Jan 03, 2024 pm 02:05 PM

Amélioration de la transmission de liaison de données PCIe interne HoloLens : Microsoft partage des brevets AR/VR

Jan 03, 2024 pm 02:05 PM

(Nwe, 27 décembre 2023) Une connexion filaire est souvent appelée « lien dur », qui connecte physiquement un nœud à un autre nœud. Une connexion filaire est PCIe. PCIe est une interface utilisée pour connecter des nœuds à haut débit, et bien que les terminaux et protocoles de connexion à haut débit tels que PCIe offrent des avantages substantiels, ces types de terminaux nécessitent une puissance élevée pour fonctionner. Pour une architecture informatique alimentée par batterie comme un casque, cela imposerait une charge énorme au système. Dans une demande de brevet intitulée « Errorrecoveryandpowermanagementbetweennodesofaninterconnectionnetwork », Microsoft décrit comment récupérer les données des barres d'erreur.