linux vcs est un simulateur Verilog compilé, un outil utilisé pour simuler et visualiser des formes d'onde ; il est similaire aux outils tels que modelsim et questasim sous Windows, ainsi qu'aux opérations de simulation quartus et vivado.

L'environnement d'exploitation de ce tutoriel : système linux5.9.8, ordinateur Dell G3.

Qu'est-ce que Linux VCS ?

Utilisation de base des outils VCS

VCS est un outil utilisé pour simuler et visualiser des formes d'onde sous Linux, similaire à des outils tels que modelsim et questasim sous Windows, ainsi qu'aux simulations quartus et vivado fonctionner.

Suffixes d'instructions communes de vcs

| Commande | signifiant |

|---|---|

-l readme.log -l readme.log

|

用于将编译产生的信息放在log文件内 |

+v2k |

是使VCS兼容verilog 2001以前的标准 |

-debug_all |

用于产生debug所需的文件 |

-f verilog_file.f |

可将.f文件里的源码全部编译 |

-R |

编译后立即运行,即编译完成后立即执行 ./simv |

-Mupdate |

源文件有修改时,只重新编译有改动的**.v**文件,节约编译时间。 |

-sverilog |

打开对Systemverilog的支持,编译Systemverilog文件时使用。 |

-timescale=1ns/1ns |

设置仿真精度 |

-o simv_file |

编译默认产生的可执行文件为simv,可以使用 -o 更改可执行文件名。如果这里修改执行仿真时候就不是使用simv而是对应的o名字了。 |

simv的常见指令

| 指令 | 含义 |

|---|---|

./simv -l run.log |

执行的日志文件保存 |

./simv -gui | utilisé pour Mettez les informations générées par compilation dans le fichier journal

-debug_all🎜 🎜Utiliser Pour générer les fichiers nécessaires au débogage🎜🎜🎜🎜-f verilog_file.f🎜🎜peut compiler tout le code source dans le fichier .f🎜🎜🎜🎜-R🎜🎜 Exécuter immédiatement après la compilation, c'est-à-dire exécuter immédiatement après la compilation 🎜./simv🎜🎜🎜🎜🎜-Mupdate🎜🎜Lorsque le fichier source est modifié, seul le **.v* modifié * Le fichier sera recompilé, économisez du temps de compilation. 🎜🎜🎜🎜-sverilog🎜🎜Activez la prise en charge de 🎜Systemverilog🎜 et utilisez-la lors de la compilation des fichiers 🎜Systemverilog🎜. 🎜🎜🎜🎜-timescale=1ns/1ns🎜🎜Définir la précision de la simulation🎜🎜🎜🎜-o simv_file🎜🎜Le fichier exécutable par défaut généré par la compilation est 🎜simv🎜, Le nom du fichier exécutable peut être modifié en utilisant 🎜-o🎜. Si vous le modifiez ici, vous n'utiliserez pas 🎜simv🎜 mais le nom o correspondant lors de l'exécution de la simulation. 🎜🎜🎜🎜🎜🎜Commandes communes de simv🎜🎜🎜🎜🎜🎜Commande 🎜🎜 signification🎜🎜🎜🎜🎜🎜./simv -l run.log🎜🎜Enregistrer le fichier journal d'exécution 🎜 🎜 🎜🎜./simv -gui🎜🎜Ouvrir avec interface graphique🎜🎜🎜🎜 est basé sur le tutoriel officiel de full adder Tout d'abord, le processus d'exécution sans utiliser de script est présenté.

(1) Exécutez d'abord vcs et ajoutez le fichier full_adder correspondant vcs加入对应的full_adder文件

vcs -sverilog -debug_all -timescale=1ns/1ps full_adder.v full_adder_tb.v -l com.log

这里先写full_adder.v 是因为tb文件需要调用它,所以把被调用的文件先写出来,这条语句会生成simv文件(如果使用了-o simv_file会生成对应的文件名字)。

(2)可以用./simv文件执行波形的界面,也可以采用下面指令以后台方式打开一个界面。

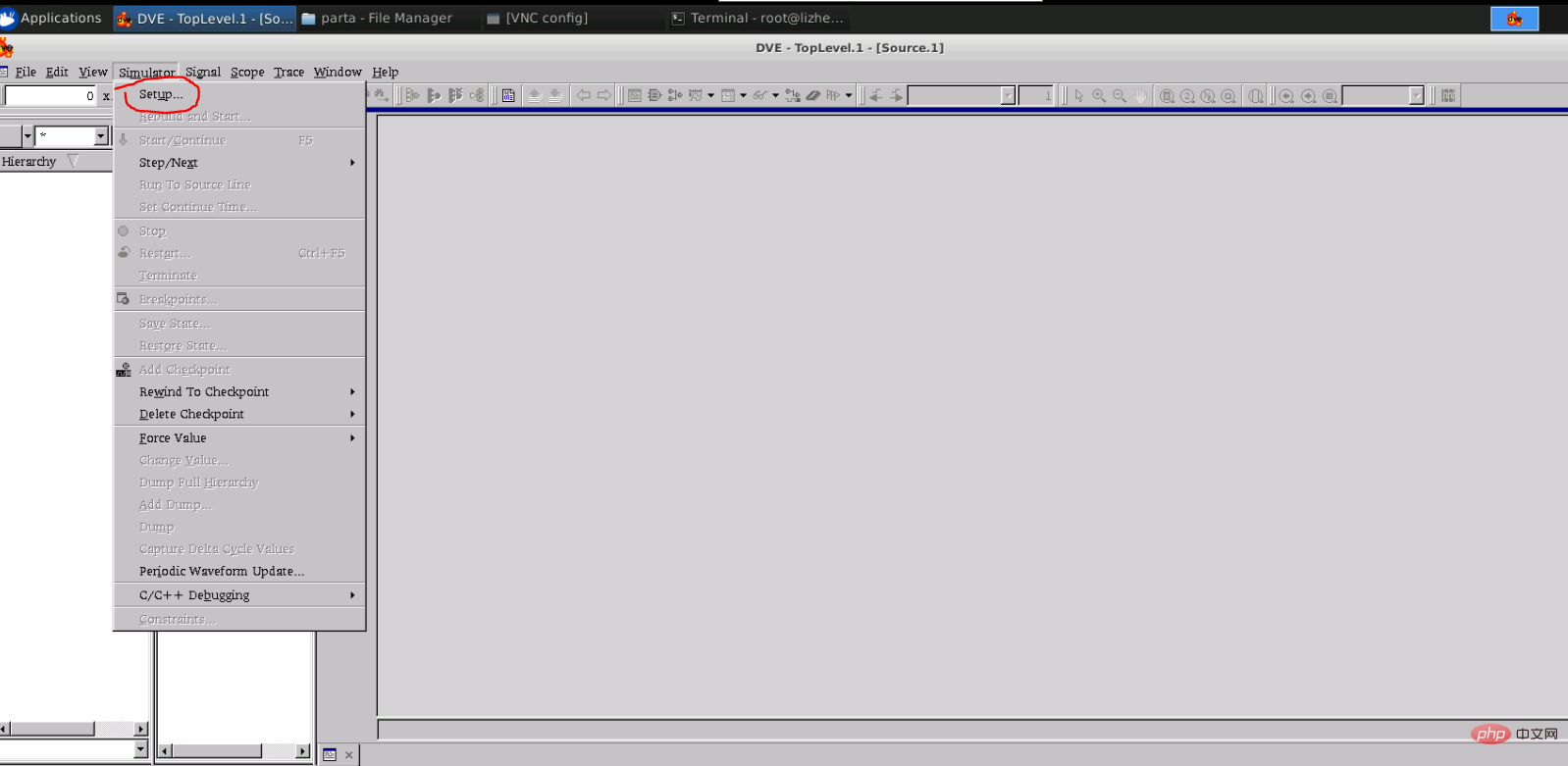

dve &或者 ./simv -l run.log -gui

(3)如果以./simv执行会直接看到波形文件,如果使用dve & 需要自行加入simv

.PHONY:vcs sim dve clean

OUTPUT = adder

VCS = vcs -sverilog +v2k -timescale=1ns/1ns \

-debug_all \

-o ${OUTPUT} \

-l compile.log \SIM = ./${OUTPUT} -l run.log

vcs: ${VCS} -f verilog_file.f

sim: ${SIM}dve:

dve -vpd vcdplus.vpd & clean: rm -rf *.log csrc simv* *.key *.vpd DVEfiles coverage *.vdb-o simv_file est utilisé, le nom de fichier correspondant sera généré).  (2) Vous pouvez utiliser le fichier

(2) Vous pouvez utiliser le fichier ./simv pour exécuter l'interface de forme d'onde, ou vous pouvez utiliser la commande suivante pour ouvrir une interface en arrière-plan. find -name ".*v" > file.list

./simv, vous verrez directement le fichier wave. Si vous utilisez dve &, vous devez ajouter le  ctrl+d

ctrl+d Quatrième : Suivre qui est utilisé pour conduire

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!