Périphériques technologiques

Périphériques technologiques

IA

IA

Un aperçu des trois architectures de puces traditionnelles pour la conduite autonome dans un seul article

Un aperçu des trois architectures de puces traditionnelles pour la conduite autonome dans un seul article

Un aperçu des trois architectures de puces traditionnelles pour la conduite autonome dans un seul article

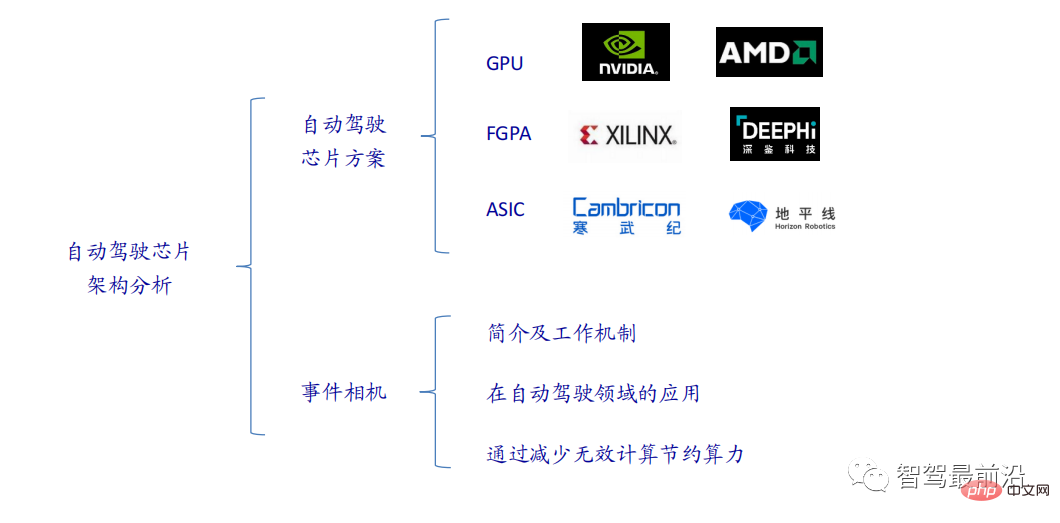

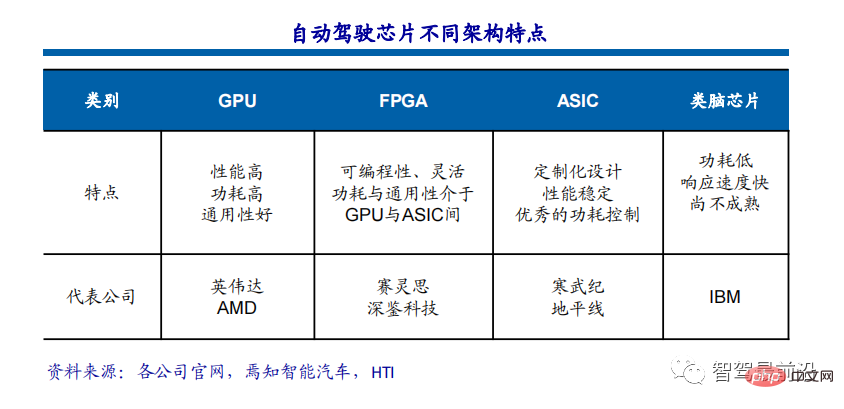

Les puces d'IA grand public actuelles sont principalement divisées en trois catégories : GPU, FPGA et ASIC. Les GPU et les FPGA sont des architectures de puces relativement matures à un stade précoce et sont des puces à usage général. ASIC est une puce personnalisée pour des scénarios d'IA spécifiques. L’industrie a confirmé que les processeurs ne sont pas adaptés au calcul de l’IA, mais qu’ils sont également essentiels dans les applications d’IA.

Solution GPU

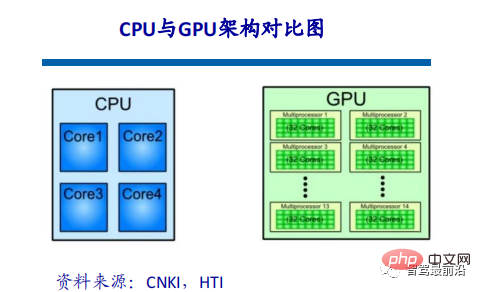

Comparaison d'architecture entre GPU et CPU

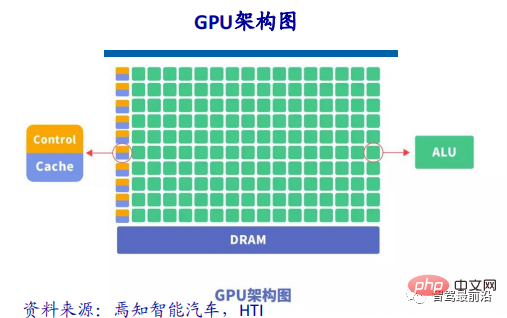

CPU suit l'architecture von Neumann, dont le cœur est de stocker des programmes/données et une exécution séquentielle en série. Par conséquent, l'architecture CPU nécessite une grande quantité d'espace pour placer l'unité de stockage (Cache) et l'unité de contrôle (Control). En revanche, l'unité de calcul (ALU) n'occupe qu'une petite partie, le CPU est donc limité en grande partie. le calcul parallèle à grande échelle. Les limitations sont relativement meilleures pour gérer les contrôles logiques.

GPU (Graphics Processing Unit), c'est-à-dire processeur graphique, est une architecture informatique parallèle à grande échelle composée d'un grand nombre d'unités de calcul. Elle était à l'origine séparée du CPU et spécifiquement utilisée pour traiter les données informatiques parallèles des images. . Il est conçu pour traiter plusieurs images en même temps. Conçu pour des tâches informatiques parallèles. Le GPU contient également des unités de calcul de base, des unités de contrôle et des unités de stockage, mais l'architecture du GPU est très différente de celle du CPU. Son schéma d'architecture est présenté ci-dessous.

Par rapport au CPU, moins de 20 % de l'espace de la puce CPU est ALU, tandis que plus de 80 % de l'espace de la puce GPU est ALU. Autrement dit, le GPU dispose de plus d’ALU pour le traitement parallèle des données.

Différence entre GPU et CPU

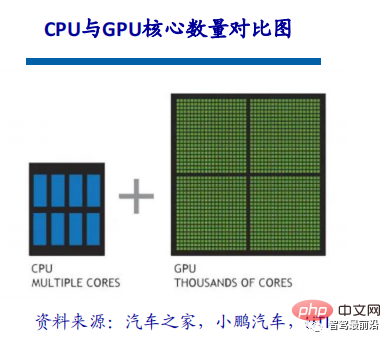

Le CPU est constitué de plusieurs cœurs optimisés pour le traitement série séquentiel, tandis que le GPU a un cœur composé de milliers de cœurs plus petits et plus puissants. de cœurs efficaces. Ces cœurs plus petits sont conçus pour gérer plusieurs tâches simultanément.

La raison pour laquelle le CPU et le GPU sont très différents est due à leurs objectifs de conception différents. Ils ciblent respectivement deux scénarios d'application différents. Le processeur a besoin d'une grande polyvalence pour gérer différents types de données. En même temps, il nécessite un jugement logique et introduit un grand nombre de sauts de branchement et de traitement d'interruptions. Tout cela rend la structure interne du CPU extrêmement complexe. Le GPU est confronté à des données à grande échelle avec des types hautement unifiés et sans dépendance les uns par rapport aux autres et à un environnement informatique pur qui n'a pas besoin d'être interrompu.

Une brève description de la technologie d'accélération GPU

Pour le deep learning, l'accélération matérielle actuelle repose principalement sur l'utilisation d'unités de traitement graphique. Par rapport aux processeurs traditionnels, les GPU ont une puissance de calcul de plusieurs ordres de grandeur supérieure et sont plus faciles à effectuer des calculs parallèles.

L'architecture multicœur du GPU contient des milliers de processeurs de flux, qui peuvent effectuer des opérations en parallèle et réduire considérablement le temps de calcul du modèle. Alors que des sociétés telles que NVIDIA et AMD continuent de promouvoir la prise en charge d'architectures parallèles à grande échelle pour leurs GPU, les GPU destinés à l'informatique générale sont devenus un moyen important d'accélérer les applications parallèles.

Actuellement, le GPU a atteint un stade relativement mature. L'utilisation du GPU pour former des réseaux neuronaux profonds peut exploiter pleinement ses capacités de calcul parallèle efficaces sur des milliers de cœurs de calcul. Dans les scénarios où des données de formation massives sont utilisées, le temps passé est considérablement réduit et moins de serveurs sont occupés. Si elle est correctement optimisée pour un réseau neuronal profond approprié, une carte GPU peut être équivalente à la puissance de calcul de dizaines, voire de centaines de serveurs CPU. Par conséquent, le GPU est devenu la solution préférée de l'industrie pour la formation de modèles d'apprentissage profond.

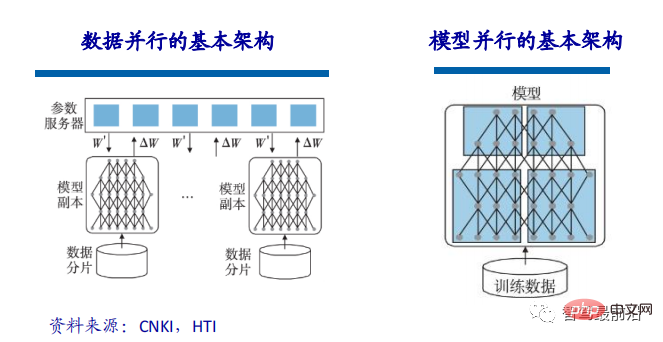

Lorsque l'échelle du modèle entraîné est relativement grande, la formation du modèle peut être accélérée grâce au parallélisme des données. Le parallélisme des données peut segmenter les données de formation et utiliser plusieurs instances de modèle pour former plusieurs morceaux de données en même temps. Dans la mise en œuvre du parallélisme des données, puisque le même modèle et des données différentes sont utilisées pour la formation, le goulot d'étranglement affectant les performances du modèle réside dans l'échange de paramètres entre plusieurs CPU ou plusieurs GPU. Selon la formule de mise à jour des paramètres, les gradients calculés par tous les modèles doivent être soumis au serveur de paramètres et mis à jour avec les paramètres correspondants. Par conséquent, la division des tranches de données et la bande passante du serveur de paramètres peuvent devenir des goulots d'étranglement qui limitent l'efficacité de. parallélisme des données.

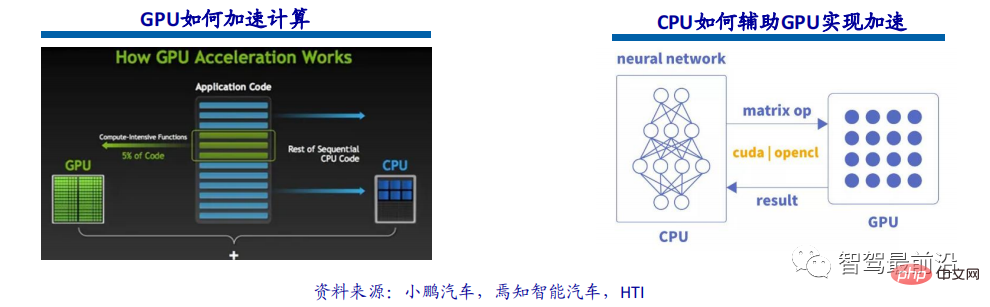

En plus du parallélisme des données, le parallélisme des modèles peut également être utilisé pour accélérer la formation des modèles. Le parallélisme du modèle fait référence à la division d'un grand modèle en plusieurs fragments, qui sont détenus respectivement par plusieurs unités de formation. Chaque unité de formation coopère les unes avec les autres pour compléter la formation du grand modèle. Le calcul accéléré par GPU fait référence à l'utilisation simultanée d'unités de traitement graphique (GPU) et de processeurs pour accélérer les applications scientifiques, analytiques, d'ingénierie, grand public et d'entreprise. Introduits pour la première fois par NVIDIA en 2007, les accélérateurs GPU sont désormais utilisés dans le monde entier pour prendre en charge les centres de données économes en énergie dans les laboratoires gouvernementaux, les universités, les entreprises et les petites et moyennes entreprises. Les GPU accélèrent les applications sur des plates-formes allant des voitures, téléphones et tablettes aux drones et robots.

Le calcul accéléré par GPU peut fournir des performances d'application extraordinaires en déchargeant la charge de travail de la partie intensive en calcul de l'application vers le GPU, tout en laissant le CPU exécuter le reste du code du programme. Du point de vue de l'utilisateur, les applications s'exécutent beaucoup plus rapidement.

Le GPU n'effectue actuellement que de simples opérations de multiplication et d'addition de matrices parallèles. La construction de modèles de réseaux neuronaux et la transmission de flux de données sont toujours effectuées sur le CPU. Le processus d'interaction entre le CPU et le GPU : obtenir des informations sur le GPU, configurer l'identifiant du GPU, charger les paramètres des neurones sur le GPU, le GPU accélère le calcul du réseau neuronal et recevoir les résultats du calcul du GPU.

Pourquoi le GPU est si important dans le domaine de la conduite autonome

L'une des catégories techniques les plus importantes de la technologie de conduite autonome est l'apprentissage profond. L'intelligence artificielle basée sur une architecture d'apprentissage profond a été. largement utilisé aujourd'hui Dans divers domaines de l'industrie automobile tels que la vision par ordinateur, le traitement du langage naturel, la fusion de capteurs, la reconnaissance de cibles et la conduite autonome, des start-ups de conduite autonome aux sociétés Internet en passant par les grands équipementiers, ils explorent activement l'utilisation des GPU construire des réseaux de neurones pour atteindre l’objectif ultime : la conduite autonome.

Après la naissance du calcul accéléré par GPU, il fournit une architecture de calcul parallèle multicœur pour les données d'entreprise, prenant en charge des sources de données que les architectures CPU précédentes ne pouvaient pas gérer. À titre de comparaison, pour accomplir la même tâche de formation en deep learning, le coût d'utilisation d'un cluster de calcul GPU n'est que de 1/200 de celui d'un cluster de calcul CPU.

Le GPU est la clé de la conduite autonome et de l'apprentissage profond

Qu'il permette à la voiture de percevoir l'environnement en temps réel ou de planifier rapidement des itinéraires de conduite et des actions, tout cela nécessite le Le cerveau de la voiture doit réagir rapidement, il est donc très important pour l'ordinateur. Les fabricants de matériel informatique ont posé d'énormes défis dans le processus de conduite autonome, des algorithmes d'apprentissage profond ou d'intelligence artificielle sont toujours nécessaires pour faire face à une infinité de situations possibles. , l'apprentissage profond et la conduite sans conducteur ont donné naissance à un âge d'or dans le développement du calcul GPU.

Un autre paramètre important du GPU est la capacité de calcul en virgule flottante. Le comptage à virgule flottante utilise des virgules décimales flottantes pour représenter un nombre à l'aide de nombres binaires de différentes longueurs, correspondant à des nombres à virgule fixe. Lors de l'itération de l'algorithme de conduite autonome, les exigences de précision sont élevées et la prise en charge des opérations en virgule flottante est requise.

Solution FPGA

Définition et structure de la puce FPGA

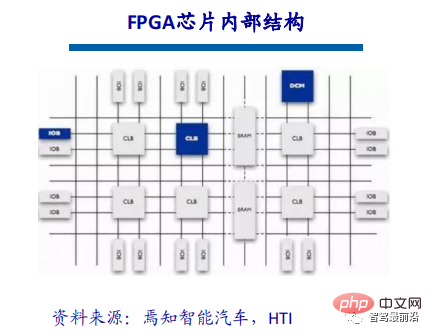

FPGA (Field-Programmable Gate Array), qui est un réseau de portes programmable sur site, est un produit de développement ultérieur basé sur des dispositifs programmables tels que PAL, GAL et CPLD. Il apparaît comme un circuit semi-personnalisé dans le domaine des circuits intégrés spécifiques à une application, qui non seulement résout les défauts des circuits personnalisés, mais surmonte également les défauts du nombre limité de circuits de porte des dispositifs programmables d'origine. La puce FPGA est principalement complétée par 6 parties, à savoir : unité d'entrée et de sortie programmable, unité logique programmable de base, gestion complète de l'horloge, bloc RAM intégré, ressources de câblage riches, unités fonctionnelles sous-jacentes intégrées et module matériel spécial intégré interne. Le FPGA grand public actuel est toujours basé sur la technologie des tables de recherche, qui a largement dépassé les performances de base des versions précédentes, et intègre des modules durs (de type ASIC) avec des fonctions communes (telles que la RAM, la gestion de l'horloge et le DSP). .

Principe de fonctionnement du FPGA

Étant donné que le FPGA doit être programmé à plusieurs reprises, la structure de base de sa logique combinatoire ne peut pas être complétée par des portes NAND fixes comme l'ASIC, mais ne peut adopter qu'une structure qui est facile à configurer encore et encore. Les tables de recherche peuvent très bien répondre à cette exigence. Actuellement, les FPGA traditionnels utilisent des structures de table de recherche basées sur la technologie SRAM. Il existe également des FPGA de qualité militaire et aérospatiale qui utilisent des structures de table de recherche basées sur la technologie Flash ou fusible et antifusible. La configuration répétée du FPGA est obtenue en gravant des fichiers pour modifier le contenu de la table de recherche.

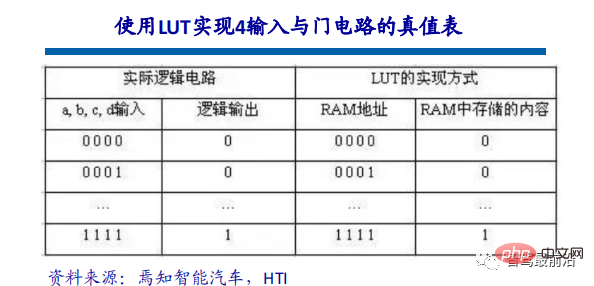

Look-Up-Table est appelée LUT, et LUT est essentiellement une RAM. Actuellement, les LUT à 4 entrées sont principalement utilisées dans les FPGA, chaque LUT peut donc être considérée comme une RAM avec des lignes d'adresse de 4 bits. Lorsque l'utilisateur décrit un circuit logique via un diagramme schématique ou un langage HDL, le logiciel de développement PLD/FPGA calcule automatiquement tous les résultats possibles du circuit logique et écrit la table de vérité (c'est-à-dire le résultat) dans la RAM à l'avance. chaque fois qu'un signal est entré Effectuer des opérations logiques équivaut à saisir une adresse, consulter la table, découvrir le contenu correspondant à l'adresse, puis la sortir.

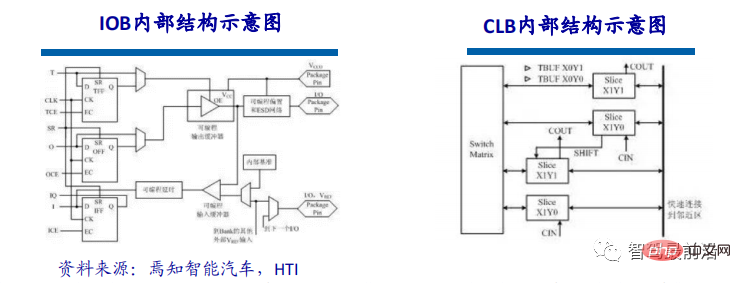

L'unité d'entrée/sortie programmable, appelée unité d'E/S, est la partie d'interface entre la puce et le circuit externe, complétant les exigences de pilotage et de correspondance pour les signaux d'entrée/sortie sous différents caractéristiques électriques. Les E/S au sein du FPGA sont classées en groupes, et chaque groupe peut prendre en charge indépendamment différentes normes d'E/S. Grâce à une configuration flexible du logiciel, il peut être adapté à différentes normes électriques et caractéristiques physiques d'E/S, le courant d'entraînement peut être ajusté et les résistances pull-up et pull-down peuvent être modifiées. À l'heure actuelle, la fréquence des ports d'E/S est de plus en plus élevée, et certains FPGA haut de gamme peuvent prendre en charge des débits de données allant jusqu'à 2 Gbit/s grâce à la technologie de registre DDR.

CLB est l'unité logique de base du FPGA. Le nombre réel et les caractéristiques des CLB varient d'un appareil à l'autre, mais chaque CLB contient une matrice de commutation configurable composée de 4 ou 6 entrées, des circuits de sélection (multiplexeurs, etc.) et une composition de bascules. La matrice de commutation est très flexible et peut être configurée pour gérer la logique combinatoire, les registres à décalage ou la RAM. Dans les dispositifs FPGA de Xilinx, CLB se compose de plusieurs tranches identiques (généralement 4 ou 2) et d'une logique supplémentaire. Chaque module CLB peut non seulement être utilisé pour mettre en œuvre une logique combinatoire et une logique séquentielle, mais peut également être configuré en tant que RAM distribuée et ROM distribuée.

Le principal tueur de la conduite autonome

Les segments de marché de la conduite autonome et des systèmes avancés d'aide à la conduite (ADAS) subissent une transformation, posant des exigences nouvelles et complexes en matière d'informatique et de capteurs capacités. Le FPGA présente des avantages uniques que les autres solutions de puces ne peuvent égaler et constitue un excellent choix pour répondre au développement et aux changements continus du secteur de la conduite autonome. Le FPGA est une technologie spéciale dans le domaine des puces. D'une part, il peut être configuré à plusieurs reprises via des outils logiciels. D'autre part, il dispose d'interfaces IO et d'unités de calcul riches. Par conséquent, le FPGA peut traiter simultanément le parallélisme des pipelines et le parallélisme des données en fonction des besoins spécifiques du scénario d'application et présente les avantages inhérents d'une performance de calcul élevée, d'une faible latence et d'une faible consommation d'énergie.

Le FPGA présente de nombreux avantages tels qu'un débit élevé, une efficacité énergétique élevée et un traitement en temps réel, ce qui est très adapté aux exigences techniques de la conduite autonome. Les normes et exigences relatives aux applications de systèmes avancés d'assistance à la conduite (ADAS) et d'expérience embarquée (IVE) évoluent rapidement. Les principales préoccupations des concepteurs de systèmes incluent une excellente flexibilité et des cycles de développement plus rapides tout en maintenant un rapport performance/puissance plus élevé. La combinaison de FPGA reprogrammables et d'un portefeuille croissant de produits de qualité automobile permet aux concepteurs automobiles de répondre aux exigences de conception et de garder une longueur d'avance sur une industrie automobile en constante évolution.

Une plateforme plus adaptable

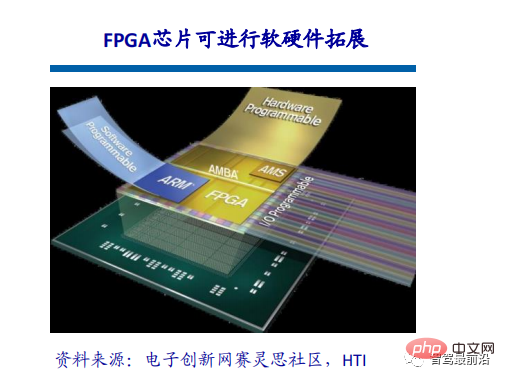

La vraie valeur des puces de conduite autonome réside dans l'utilisation du moteur de calcul, c'est-à-dire la différence entre les performances théoriques et les performances réelles. Les FPGA contiennent un grand nombre de liens de routage ainsi qu'une grande quantité de petit stockage. La combinaison de ces ressources permet aux concepteurs de créer des réseaux de flux de données personnalisés pour leurs moteurs de calcul pour des niveaux d'utilisation plus élevés. La logique programmable offre aux clients un haut degré de flexibilité pour s'adapter aux besoins changeants des domaines d'application émergents tels que l'ADAS et la conduite autonome. Tirer parti des normes d'interface améliorées, de l'innovation en matière d'algorithmes et des nouvelles technologies de capteurs nécessite une plate-forme adaptable capable de prendre en charge non seulement les modifications logicielles mais également les modifications matérielles, domaine dans lequel les puces FPGA excellent.

Les puces FPGA sont évolutives. Les puces évolutives modifient la quantité de logique programmable, principalement dans des boîtiers compatibles avec les broches. Cela signifie que les développeurs peuvent créer une plate-forme ECU unique pour héberger les versions faible, moyenne et élevée des packages de fonctionnalités ADAS et adapter les coûts selon les besoins en sélectionnant la puce de densité minimale requise.

Solutions différenciées

Les puces FPGA permettent aux développeurs de créer des solutions de traitement différenciées uniques qui peuvent être optimisées pour des applications ou des capteurs spécifiques. Cela n'est pas possible avec les puces ASSP, et même celles qui proposent des accélérateurs dédiés sont limités dans la manière dont ils peuvent être utilisés et sont disponibles pour pratiquement tous les concurrents. Les clients de longue date de Xilinx, par exemple, ont créé des bibliothèques de propriété intellectuelle de grande valeur auxquelles eux seuls peuvent accéder, et ces capacités peuvent être utilisées dans les différents produits de l'entreprise. À partir du nœud 90 nm, les puces Xilinx se sont révélées extrêmement rentables pour les applications automobiles à grand volume, avec plus de 160 millions de puces Xilinx utilisées dans l'industrie.

Solution ASIC

Définition et caractéristiques ASIC

Les puces ASIC peuvent être divisées en puces TPU, puces DPU et puces NPU selon différentes fonctions du terminal. Parmi eux, TPU est un processeur tensoriel dédié au machine learning. Par exemple, Google a développé un accélérateur d'IA programmable pour la plate-forme Tensorflow en mai 2016. Son jeu d'instructions interne peut s'exécuter lorsque le programme Tensorflow change ou que l'algorithme est mis à jour. DPU est Data Processing Unit, qui peut fournir des moteurs pour des scénarios informatiques tels que les centres de données. NPU est un processeur de réseau neuronal qui simule les neurones et les synapses humains au niveau du circuit et utilise des jeux d'instructions d'apprentissage profond pour traiter directement les données électroniques des neurones et des synapses à grande échelle.

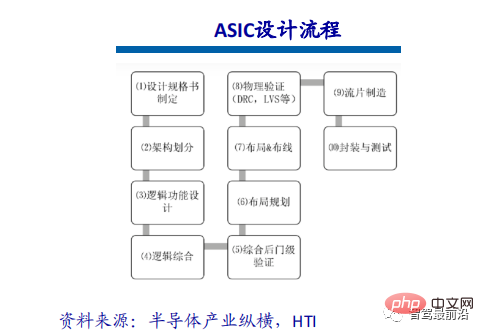

ASIC dispose de deux méthodes de conception : la personnalisation complète et la semi-personnalisation. La personnalisation complète nécessite d'énormes coûts de main-d'œuvre et de temps pour terminer l'ensemble du processus de conception de circuits intégrés de manière totalement indépendante. Bien qu'il soit plus flexible et meilleur que l'ASIC semi-personnalisé, son efficacité de développement est très faible par rapport à l'ASIC semi-personnalisé.

Amélioration évidente des performances

Les puces ASIC sont très adaptées aux scénarios d'application de l'intelligence artificielle. Par exemple, la première puce de NVIDIA, Tesla P100, conçue de toutes pièces pour l'apprentissage profond, a une vitesse de traitement des données 12 fois supérieure à celle de sa série de GPU lancée en 2014. La puce TPU personnalisée de Google pour l'apprentissage automatique améliore les performances matérielles à un niveau équivalent à celui des puces actuelles sept ans après le développement de la loi de Moore. Tout comme les processeurs ont changé les énormes ordinateurs du passé, les puces ASIC d’intelligence artificielle changeront également considérablement le visage des dispositifs matériels d’IA d’aujourd’hui. Par exemple, le célèbre AlphaGo utilise environ 170 unités de traitement graphique (GPU) et 1 200 unités centrales de traitement (CPU). Ces appareils nécessitent une salle informatique, une climatisation haute puissance et plusieurs experts pour la maintenance du système. Et si toutes les puces dédiées sont utilisées, cela ne nécessitera probablement qu'un espace de la taille d'un boîtier de stockage ordinaire, et la consommation électrique sera considérablement réduite.

La voie technologique ASIC est limitée et ouverte, et les fabricants de puces doivent se développer pour les réseaux, modèles et opérateurs grand public liés à la conduite. Avec les mêmes performances, la surface de la puce est plus petite, le coût est inférieur et la consommation d'énergie est inférieure. La voie technologique ASIC aura un grand potentiel à l'avenir. Choisir la voie ASIC ne signifie pas développer différents ASIC pour différents modèles ou effectuer différentes vérifications. Étant donné que les fonctions que les différents modèles doivent implémenter sont à peu près les mêmes et que la puce a un accès limité aux modèles et aux opérateurs, une itération rapide de l'algorithme n'affectera pas la prise en charge par la puce des fonctions de couche supérieure. Les constructeurs automobiles coopèrent avec des sociétés de conception de puces pour réaliser une personnalisation différenciée ou un meilleur choix. Car même avec une personnalisation différenciée, 50 % des parties internes de la puce sont universelles. Les sociétés de conception de puces peuvent réaliser des conceptions différenciées basées sur la version originale pour réaliser certaines fonctions différenciées.

Comparaison des solutions d'architecture grand public : trois architectures grand public

FPGA est un produit développé sur la base de dispositifs programmables tels que PAL et GAL. Il apparaît comme un circuit semi-personnalisé dans le domaine des circuits intégrés spécifiques à une application, qui non seulement résout les défauts des circuits personnalisés, mais surmonte également les défauts du nombre limité de circuits de porte des dispositifs programmables d'origine. Avantages : programmation illimitée, faible latence, parallélisme des pipelines et des données, performances en temps réel les plus élevées et flexibilité la plus élevée. Inconvénients : Il est difficile à développer, adapté uniquement aux opérations en virgule fixe et relativement coûteux.

L'unité de traitement graphique (GPU), également connue sous le nom de noyau d'affichage, processeur visuel, puce d'affichage, est une sorte d'unité de traitement graphique spécialisée dans l'image et le traitement sur les ordinateurs personnels, les postes de travail, les consoles de jeux et certains appareils mobiles (tels que (tablettes, téléphones portables, etc.) Un microprocesseur qui effectue des opérations liées aux graphiques. Avantages : Il fournit la structure de base du calcul parallèle multicœur et possède un très grand nombre de cœurs, qui peuvent prendre en charge le calcul parallèle de grandes quantités de données et dispose de capacités de calcul à virgule flottante plus élevées. Inconvénients : capacité de contrôle de gestion (la plus faible), consommation électrique (la plus élevée).

ASIC, ou circuit intégré spécifique à une application, fait référence à un circuit intégré conçu et fabriqué en réponse aux exigences spécifiques des utilisateurs et aux besoins de systèmes électroniques spécifiques. Actuellement, l'un des moyens les plus populaires de concevoir des ASIC consiste à utiliser le CPLD (Complex Programmable Logic Device) et le FPGA (Field Programmable Logic Array). Avantages : en tant que produit de la technologie des circuits intégrés et de la technologie complète de la machine ou du système d'un utilisateur spécifique, il a une taille plus petite, un poids plus léger, une consommation d'énergie inférieure, une fiabilité améliorée, des performances et une confidentialité améliorées par rapport aux circuits intégrés à usage général. réduction des coûts et autres avantages. Inconvénients : Flexibilité insuffisante et plus cher que FPGA.

Limitations de la théorie de la puissance de calcul : la puissance de calcul TOPS n'est pas tout à fait égale aux performances réelles

Avec l'essor de l'ADAS, de la technologie de conduite autonome et l'approfondissement progressif des voitures définies par logiciel , voitures intelligentes La demande de puissance de calcul et de capacités de traitement de données massives est montée en flèche, et la solution « d'empilage » de puces des automobiles traditionnelles ne peut plus répondre aux besoins de puissance de calcul de la conduite autonome. La puce sert en fin de compte la plate-forme informatique embarquée du constructeur automobile. Dans le cas des « voitures définies par logiciel », la résolution du problème de support de la plate-forme informatique du système de conduite intelligent ne peut être obtenue uniquement en empilant la puissance de calcul des puces.

La puce est la scène du logiciel. La norme pour mesurer la qualité de la puce dépend de la capacité du logiciel sur la puce à maximiser sa fonction. Il doit y avoir une adéquation efficace entre la puissance de calcul et le logiciel. Lorsque l’on compare deux puces ayant la même puissance de calcul, la puce qui permet au logiciel de fonctionner le plus efficacement est la « bonne puce ». Les facteurs les plus importants qui déterminent la véritable valeur de la puissance de calcul sont la bande passante de la mémoire (SRAM et DRAM), ainsi que la fréquence de fonctionnement réelle (c'est-à-dire la tension d'alimentation ou la température) et la taille du lot de l'algorithme.

La puissance de calcul TOPS d'une seule puce est un indicateur clé, mais ce n'est pas le seul. La conduite autonome est un système complexe qui nécessite une collaboration véhicule-route à la périphérie du cloud. Ainsi, en plus du noyau, sa concurrence comprend également les synergies logicielles et matérielles, les plateformes, les chaînes d'outils, etc. L'expansion infinie de la puissance de calcul des puces et du matériel embarqué ne sera pas une tendance future, et le matériel doit également correspondre à la situation réelle. Derrière ce phénomène se cache le problème d’une consommation d’énergie élevée et d’une faible utilisation.

Introduction à la caméra événementielle

Introduction et mécanisme de fonctionnement

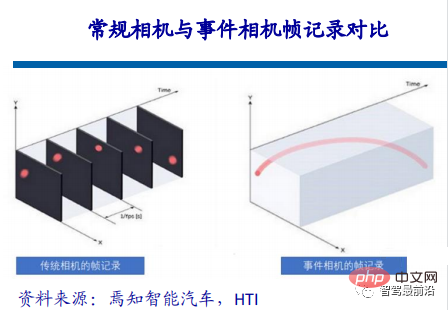

La caméra événementielle est inspirée de la vision des yeux humains et des animaux, et certaines personnes l'appellent la rétine de silicium. La vision biologique n'est sensible qu'aux zones présentant des changements, et les caméras événementielles capturent l'apparition d'événements ou de changements. ,

Dans le champ visuel traditionnel, les informations renvoyées par la caméra sont synchrones. La soi-disant synchronisation signifie qu'à un certain instant t, la caméra effectuera une exposition et remplira tous les pixels à ce moment-là d'une manière. matrice et la renvoyer. Produire une photo. Tous les pixels d'une photo correspondent au même moment. Quant à la vidéo, il s'agit simplement d'une image composée de plusieurs images. L'intervalle de temps entre les images adjacentes peut être grand ou petit. Il s'agit de la fréquence d'images, également appelée latence temporelle. Les caméras événementielles sont similaires au cerveau et aux yeux humains, ignorant l’arrière-plan non pertinent et détectant directement le cœur d’une scène, créant ainsi des événements purs plutôt que des données.

Le mécanisme de fonctionnement de la caméra d'événement est que lorsque la luminosité d'un certain pixel passe à un certain seuil, la caméra renvoie un événement dans le format ci-dessus, où les deux premiers éléments sont les coordonnées en pixels de l'événement, et le troisième L'élément est l'horodatage de l'événement, et le dernier élément est la polarité (polarité) 0, 1 (ou -1, 1), qui représente si la luminosité est de faible à élevée ou de élevée à faible.

De cette façon, tant qu'il y a un changement dans la valeur du pixel dans tout le champ de vision de la caméra, un événement sera renvoyé de manière asynchrone (peu importe la taille de l'intervalle de temps, ils ne peuvent pas). être complètement simultané), donc les horodatages des événements sont différents. En raison du simple retour, il a une faible latence par rapport aux caméras traditionnelles et peut capturer les changements de pixels dans un court intervalle de temps.

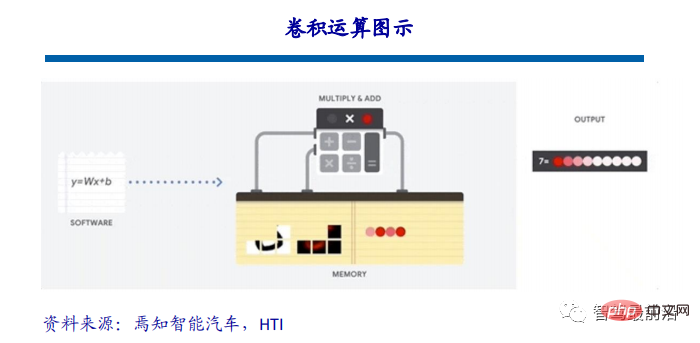

Application dans le domaine de la conduite autonome

Les algorithmes de reconnaissance visuelle utilisés aujourd'hui dans le domaine de la conduite autonome sont essentiellement basés sur des réseaux de neurones convolutifs, et le fonctionnement de l'algorithme visuel est opération de convolution essentiellement répétée. Ce type de calcul n'est pas compliqué. En substance, il implique uniquement l'addition, la soustraction, la multiplication et la division, qui sont une sorte d'opérations de multiplication, d'accumulation et d'accumulation. Cependant, de telles opérations simples existent en grand nombre dans les réseaux de neurones convolutifs, ce qui impose des exigences élevées en matière de performances du processeur.

Prenons ResNet-152 comme exemple. Il s'agit d'un réseau neuronal convolutionnel à 152 couches. La quantité de calcul requise pour traiter une image de taille 224*224 est d'environ 22,6 milliards de fois. Pour une caméra de 30 images, la puissance de calcul requise peut atteindre 33 000 milliards de fois par seconde, ce qui est très énorme.

Économisez de la puissance de calcul en réduisant les calculs invalides

99% des données visuelles dans le domaine de la conduite autonome constituent un arrière-plan inutile dans le traitement de l'IA. Par exemple, lors de la détection de sondes fantômes, la zone modifiée représente une très petite partie, mais le traitement visuel traditionnel doit toujours traiter 99 % des zones d'arrière-plan qui ne changent pas, ce qui non seulement gaspille beaucoup de puissance de calcul, mais aussi du temps. . Ou s'il y a un diamant dans le gravier, la puce IA et les caméras traditionnelles doivent identifier chaque grain de sable et filtrer les diamants, mais les humains peuvent détecter les diamants en les regardant simplement. les caméras prennent plus de temps que les humains, 100 fois ou 1000 fois.

En plus des avantages d'informations redondantes réduites et de presque aucun retard, les avantages des caméras événementielles sont également dus à une faible latence lors de la prise de vue d'objets à grande vitesse, les caméras traditionnelles souffriront de flou en raison d'une période de temps d'exposition, tandis que les caméras événementielles n'ont presque pas de flou de réunion. De plus, la caméra événementielle a une plage dynamique vraiment élevée. En raison des caractéristiques de la caméra événementielle, les caméras traditionnelles seront « aveugles » dans des environnements à forte ou faible intensité lumineuse, mais les changements de pixels existent toujours, de sorte que la caméra événementielle peut le faire. je vois encore clairement quelque chose.

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!

Outils d'IA chauds

Undresser.AI Undress

Application basée sur l'IA pour créer des photos de nu réalistes

AI Clothes Remover

Outil d'IA en ligne pour supprimer les vêtements des photos.

Undress AI Tool

Images de déshabillage gratuites

Clothoff.io

Dissolvant de vêtements AI

AI Hentai Generator

Générez AI Hentai gratuitement.

Article chaud

Outils chauds

Bloc-notes++7.3.1

Éditeur de code facile à utiliser et gratuit

SublimeText3 version chinoise

Version chinoise, très simple à utiliser

Envoyer Studio 13.0.1

Puissant environnement de développement intégré PHP

Dreamweaver CS6

Outils de développement Web visuel

SublimeText3 version Mac

Logiciel d'édition de code au niveau de Dieu (SublimeText3)

Sujets chauds

1359

1359

52

52

Pourquoi le Gaussian Splatting est-il si populaire dans la conduite autonome que le NeRF commence à être abandonné ?

Jan 17, 2024 pm 02:57 PM

Pourquoi le Gaussian Splatting est-il si populaire dans la conduite autonome que le NeRF commence à être abandonné ?

Jan 17, 2024 pm 02:57 PM

Écrit ci-dessus et compréhension personnelle de l'auteur Le Gaussiansplatting tridimensionnel (3DGS) est une technologie transformatrice qui a émergé dans les domaines des champs de rayonnement explicites et de l'infographie ces dernières années. Cette méthode innovante se caractérise par l’utilisation de millions de gaussiennes 3D, ce qui est très différent de la méthode du champ de rayonnement neuronal (NeRF), qui utilise principalement un modèle implicite basé sur les coordonnées pour mapper les coordonnées spatiales aux valeurs des pixels. Avec sa représentation explicite de scènes et ses algorithmes de rendu différenciables, 3DGS garantit non seulement des capacités de rendu en temps réel, mais introduit également un niveau de contrôle et d'édition de scène sans précédent. Cela positionne 3DGS comme un révolutionnaire potentiel pour la reconstruction et la représentation 3D de nouvelle génération. À cette fin, nous fournissons pour la première fois un aperçu systématique des derniers développements et préoccupations dans le domaine du 3DGS.

Comment résoudre le problème de la longue traîne dans les scénarios de conduite autonome ?

Jun 02, 2024 pm 02:44 PM

Comment résoudre le problème de la longue traîne dans les scénarios de conduite autonome ?

Jun 02, 2024 pm 02:44 PM

Hier, lors de l'entretien, on m'a demandé si j'avais posé des questions à longue traîne, j'ai donc pensé faire un bref résumé. Le problème à longue traîne de la conduite autonome fait référence aux cas extrêmes dans les véhicules autonomes, c'est-à-dire à des scénarios possibles avec une faible probabilité d'occurrence. Le problème perçu de la longue traîne est l’une des principales raisons limitant actuellement le domaine de conception opérationnelle des véhicules autonomes intelligents à véhicule unique. L'architecture sous-jacente et la plupart des problèmes techniques de la conduite autonome ont été résolus, et les 5 % restants des problèmes à longue traîne sont progressivement devenus la clé pour restreindre le développement de la conduite autonome. Ces problèmes incluent une variété de scénarios fragmentés, de situations extrêmes et de comportements humains imprévisibles. La « longue traîne » des scénarios limites dans la conduite autonome fait référence aux cas limites dans les véhicules autonomes (VA). Les cas limites sont des scénarios possibles avec une faible probabilité d'occurrence. ces événements rares

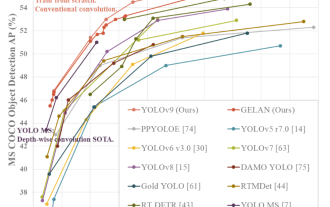

YOLO est immortel ! YOLOv9 est sorti : performances et vitesse SOTA~

Feb 26, 2024 am 11:31 AM

YOLO est immortel ! YOLOv9 est sorti : performances et vitesse SOTA~

Feb 26, 2024 am 11:31 AM

Les méthodes d'apprentissage profond d'aujourd'hui se concentrent sur la conception de la fonction objectif la plus appropriée afin que les résultats de prédiction du modèle soient les plus proches de la situation réelle. Dans le même temps, une architecture adaptée doit être conçue pour obtenir suffisamment d’informations pour la prédiction. Les méthodes existantes ignorent le fait que lorsque les données d’entrée subissent une extraction de caractéristiques couche par couche et une transformation spatiale, une grande quantité d’informations sera perdue. Cet article abordera des problèmes importants lors de la transmission de données via des réseaux profonds, à savoir les goulots d'étranglement de l'information et les fonctions réversibles. Sur cette base, le concept d'information de gradient programmable (PGI) est proposé pour faire face aux différents changements requis par les réseaux profonds pour atteindre des objectifs multiples. PGI peut fournir des informations d'entrée complètes pour la tâche cible afin de calculer la fonction objectif, obtenant ainsi des informations de gradient fiables pour mettre à jour les pondérations du réseau. De plus, un nouveau cadre de réseau léger est conçu

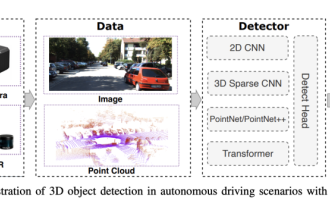

Choisir une caméra ou un lidar ? Une étude récente sur la détection robuste d'objets 3D

Jan 26, 2024 am 11:18 AM

Choisir une caméra ou un lidar ? Une étude récente sur la détection robuste d'objets 3D

Jan 26, 2024 am 11:18 AM

0. Écrit à l'avant&& Compréhension personnelle que les systèmes de conduite autonome s'appuient sur des technologies avancées de perception, de prise de décision et de contrôle, en utilisant divers capteurs (tels que caméras, lidar, radar, etc.) pour percevoir l'environnement et en utilisant des algorithmes et des modèles pour une analyse et une prise de décision en temps réel. Cela permet aux véhicules de reconnaître les panneaux de signalisation, de détecter et de suivre d'autres véhicules, de prédire le comportement des piétons, etc., permettant ainsi de fonctionner en toute sécurité et de s'adapter à des environnements de circulation complexes. Cette technologie attire actuellement une grande attention et est considérée comme un domaine de développement important pour l'avenir des transports. . un. Mais ce qui rend la conduite autonome difficile, c'est de trouver comment faire comprendre à la voiture ce qui se passe autour d'elle. Cela nécessite que l'algorithme de détection d'objets tridimensionnels du système de conduite autonome puisse percevoir et décrire avec précision les objets dans l'environnement, y compris leur emplacement,

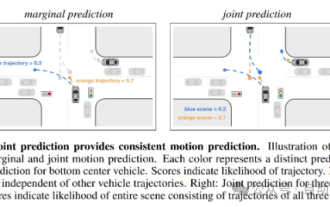

Cet article vous suffit pour en savoir plus sur la conduite autonome et la prédiction de trajectoire !

Feb 28, 2024 pm 07:20 PM

Cet article vous suffit pour en savoir plus sur la conduite autonome et la prédiction de trajectoire !

Feb 28, 2024 pm 07:20 PM

La prédiction de trajectoire joue un rôle important dans la conduite autonome. La prédiction de trajectoire de conduite autonome fait référence à la prédiction de la trajectoire de conduite future du véhicule en analysant diverses données pendant le processus de conduite du véhicule. En tant que module central de la conduite autonome, la qualité de la prédiction de trajectoire est cruciale pour le contrôle de la planification en aval. La tâche de prédiction de trajectoire dispose d'une riche pile technologique et nécessite une connaissance de la perception dynamique/statique de la conduite autonome, des cartes de haute précision, des lignes de voie, des compétences en architecture de réseau neuronal (CNN&GNN&Transformer), etc. Il est très difficile de démarrer ! De nombreux fans espèrent se lancer dans la prédiction de trajectoire le plus tôt possible et éviter les pièges. Aujourd'hui, je vais faire le point sur quelques problèmes courants et des méthodes d'apprentissage introductives pour la prédiction de trajectoire ! Connaissances introductives 1. Existe-t-il un ordre d'entrée pour les épreuves de prévisualisation ? R : Regardez d’abord l’enquête, p

SIMPL : un benchmark de prédiction de mouvement multi-agents simple et efficace pour la conduite autonome

Feb 20, 2024 am 11:48 AM

SIMPL : un benchmark de prédiction de mouvement multi-agents simple et efficace pour la conduite autonome

Feb 20, 2024 am 11:48 AM

Titre original : SIMPL : ASimpleandEfficientMulti-agentMotionPredictionBaselineforAutonomousDriving Lien article : https://arxiv.org/pdf/2402.02519.pdf Lien code : https://github.com/HKUST-Aerial-Robotics/SIMPL Affiliation de l'auteur : Université des sciences de Hong Kong et technologie Idée DJI Paper : cet article propose une base de référence de prédiction de mouvement (SIMPL) simple et efficace pour les véhicules autonomes. Par rapport au cent agent traditionnel

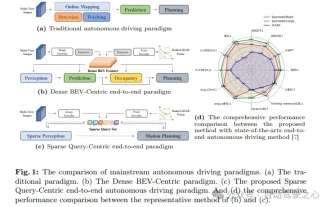

NuScenes dernier SOTA SparseAD : les requêtes clairsemées contribuent à une conduite autonome efficace de bout en bout !

Apr 17, 2024 pm 06:22 PM

NuScenes dernier SOTA SparseAD : les requêtes clairsemées contribuent à une conduite autonome efficace de bout en bout !

Apr 17, 2024 pm 06:22 PM

Écrit à l'avant et point de départ Le paradigme de bout en bout utilise un cadre unifié pour réaliser plusieurs tâches dans les systèmes de conduite autonome. Malgré la simplicité et la clarté de ce paradigme, les performances des méthodes de conduite autonome de bout en bout sur les sous-tâches sont encore loin derrière les méthodes à tâche unique. Dans le même temps, les fonctionnalités de vue à vol d'oiseau (BEV) denses, largement utilisées dans les méthodes de bout en bout précédentes, rendent difficile l'adaptation à davantage de modalités ou de tâches. Un paradigme de conduite autonome de bout en bout (SparseAD) centré sur la recherche clairsemée est proposé ici, dans lequel la recherche clairsemée représente entièrement l'ensemble du scénario de conduite, y compris l'espace, le temps et les tâches, sans aucune représentation BEV dense. Plus précisément, une architecture clairsemée unifiée est conçue pour la connaissance des tâches, notamment la détection, le suivi et la cartographie en ligne. De plus, lourd

Parlons des systèmes de conduite autonome de bout en bout et de nouvelle génération, ainsi que de quelques malentendus sur la conduite autonome de bout en bout ?

Apr 15, 2024 pm 04:13 PM

Parlons des systèmes de conduite autonome de bout en bout et de nouvelle génération, ainsi que de quelques malentendus sur la conduite autonome de bout en bout ?

Apr 15, 2024 pm 04:13 PM

Au cours du mois dernier, pour des raisons bien connues, j'ai eu des échanges très intensifs avec divers professeurs et camarades de classe du secteur. Un sujet inévitable dans l'échange est naturellement le populaire Tesla FSDV12 de bout en bout. Je voudrais profiter de cette occasion pour trier certaines de mes pensées et opinions en ce moment pour votre référence et votre discussion. Comment définir un système de conduite autonome de bout en bout et quels problèmes devraient être résolus de bout en bout ? Selon la définition la plus traditionnelle, un système de bout en bout fait référence à un système qui saisit les informations brutes des capteurs et génère directement les variables pertinentes pour la tâche. Par exemple, en reconnaissance d'images, CNN peut être appelé de bout en bout par rapport à la méthode traditionnelle d'extraction de caractéristiques + classificateur. Dans les tâches de conduite autonome, saisir les données de divers capteurs (caméra/LiDAR