Périphériques technologiques

Périphériques technologiques

IA

IA

Scientifique en chef de NVIDIA : Le passé, le présent et l'avenir du matériel d'apprentissage profond

Scientifique en chef de NVIDIA : Le passé, le présent et l'avenir du matériel d'apprentissage profond

Scientifique en chef de NVIDIA : Le passé, le présent et l'avenir du matériel d'apprentissage profond

Les dix dernières années ont été la « décennie dorée » de l'apprentissage profond. Il a complètement changé la façon dont les humains travaillent et jouent, et a été largement utilisé dans diverses industries telles que les soins médicaux, l'éducation et la conception de produits, etc. cela est indissociable du progrès du matériel informatique, notamment de l’innovation dans les GPU.

La mise en œuvre réussie d'une technologie de deep learning dépend de trois éléments majeurs : Le premier est l'algorithme. La plupart des algorithmes d'apprentissage profond tels que les réseaux de neurones profonds, les réseaux de neurones convolutifs, les algorithmes de rétropropagation et la descente de gradient stochastique ont été proposés dans les années 1980 ou même avant.

Le deuxième est l'ensemble de données. L'ensemble de données utilisé pour entraîner un réseau neuronal doit être suffisamment volumineux pour que le réseau neuronal surpasse les autres techniques. Ce n’est qu’au début du 21e siècle que de grands ensembles de données tels que Pascal et ImageNet sont devenus disponibles. Le troisième est le matériel. Ce n'est qu'avec un développement matériel mature que le temps nécessaire à la formation de grands réseaux neuronaux avec de grands ensembles de données pourra être contrôlé dans une plage raisonnable. L'industrie estime généralement qu'une durée de formation plus « raisonnable » est d'environ deux semaines.

À ce stade, un feu de prairie s'est allumé dans le domaine du deep learning. Si les algorithmes et les ensembles de données sont considérés comme le carburant mixte du deep learning, alors le GPU est l’étincelle qui les allume. Lorsque de puissants GPU peuvent être utilisés pour former des réseaux, la technologie du deep learning devient pratique.

Depuis lors, l'apprentissage profond a remplacé d'autres algorithmes et a été largement utilisé dans la classification d'images, la détection d'images, la reconnaissance vocale, le traitement du langage naturel, l'analyse du timing et d'autres domaines. Il peut même être vu dans le Go et les échecs. À mesure que l’apprentissage profond pénètre tous les aspects de la vie humaine, la formation et l’inférence de modèles nécessitent un matériel de plus en plus exigeant.

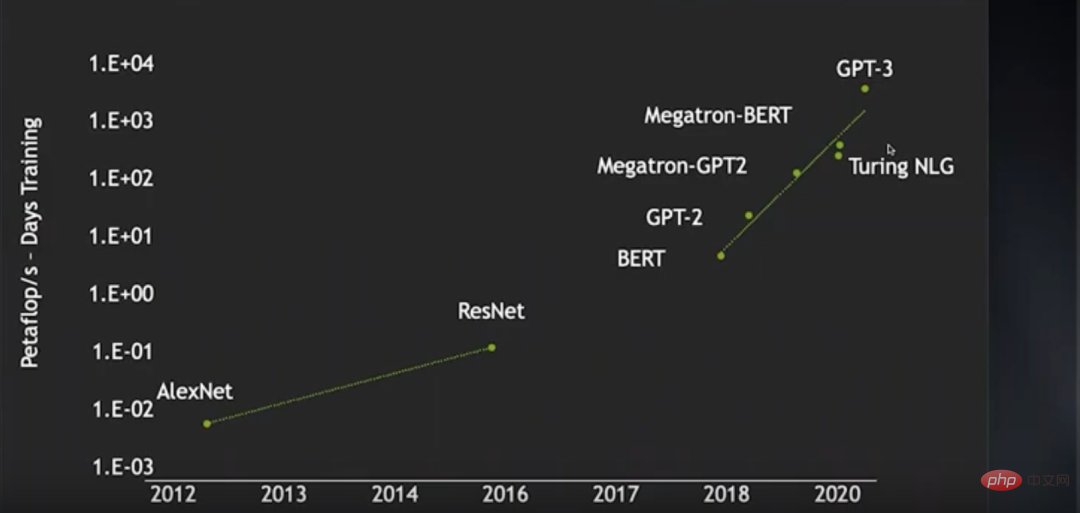

De l'émergence d'AlexNet en 2012 à l'avènement de ResNet en 2016, la consommation de puissance de calcul de formation des réseaux de neurones d'images (en pétaflop/s-jour) a augmenté de près de 2 ordres de ampleur, et depuis 2018 Du BERT en 2016 au GPT-3 ces dernières années, la consommation d'énergie de calcul de la formation a augmenté de près de 4 ordres de grandeur. Au cours de cette période, grâce aux progrès de certaines technologies, l'efficacité de la formation des réseaux de neurones a été considérablement améliorée, économisant ainsi beaucoup de puissance de calcul, sinon l'augmentation de la consommation de puissance de calcul sera encore plus exagérée.

Les chercheurs souhaitent utiliser un plus grand ensemble de données linguistiques non supervisées pour former un modèle de langage plus large. Cependant, bien qu'ils disposent déjà d'un cluster GPU de 4 000 nœuds, les opérations pouvant être traitées dans un temps de formation raisonnable sont encore très limitées. . Cela signifie que la rapidité avec laquelle la technologie d’apprentissage profond se développe dépend de la rapidité avec laquelle le matériel se développe.

De nos jours, les modèles d'apprentissage profond sont non seulement de plus en plus complexes, mais ont également une gamme d'applications de plus en plus large. Il est donc nécessaire de continuer à améliorer les performances du deep learning. Alors, comment le matériel d’apprentissage profond peut-il continuer à s’améliorer ? Bill Dally, scientifique en chef de NVIDIA, est sans aucun doute l'autorité pour répondre à cette question Avant la sortie du GPU H100, il a passé en revue l'état actuel du matériel d'apprentissage profond dans un discours et a discuté de plusieurs directions pour l'amélioration continue de l'expansion des performances lorsque la loi de Moore échoue. . La communauté OneFlow a compilé ceci.

1 Historique de l'évolution de l'architecture GPU

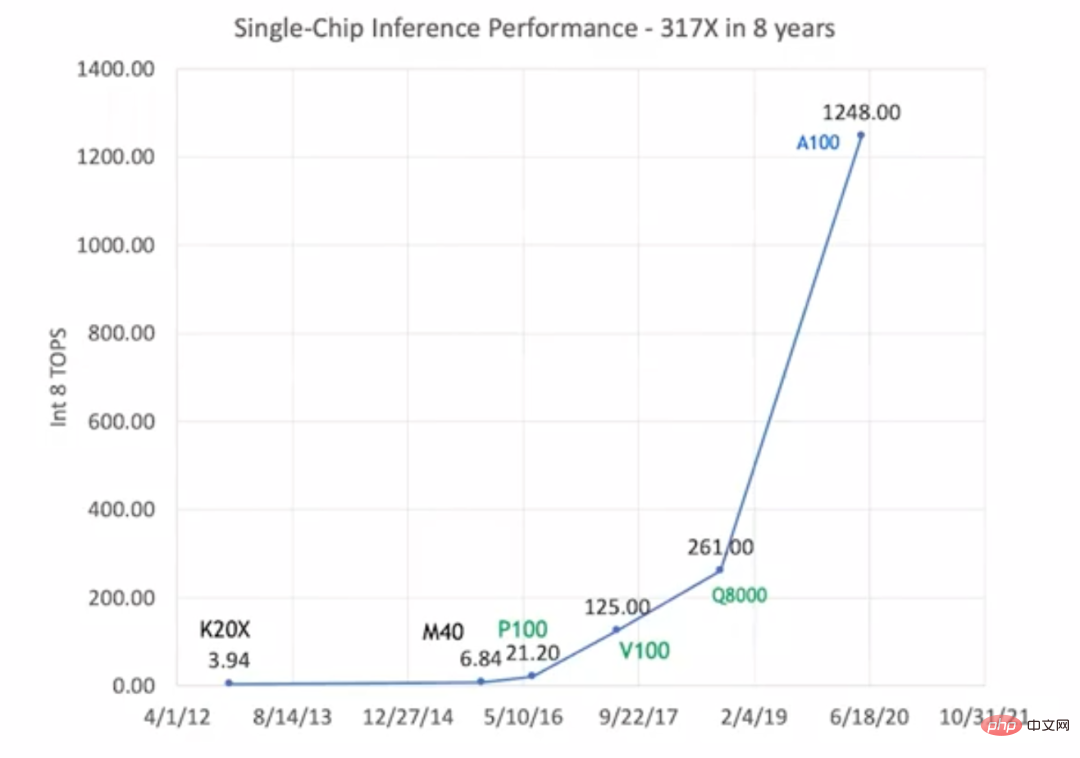

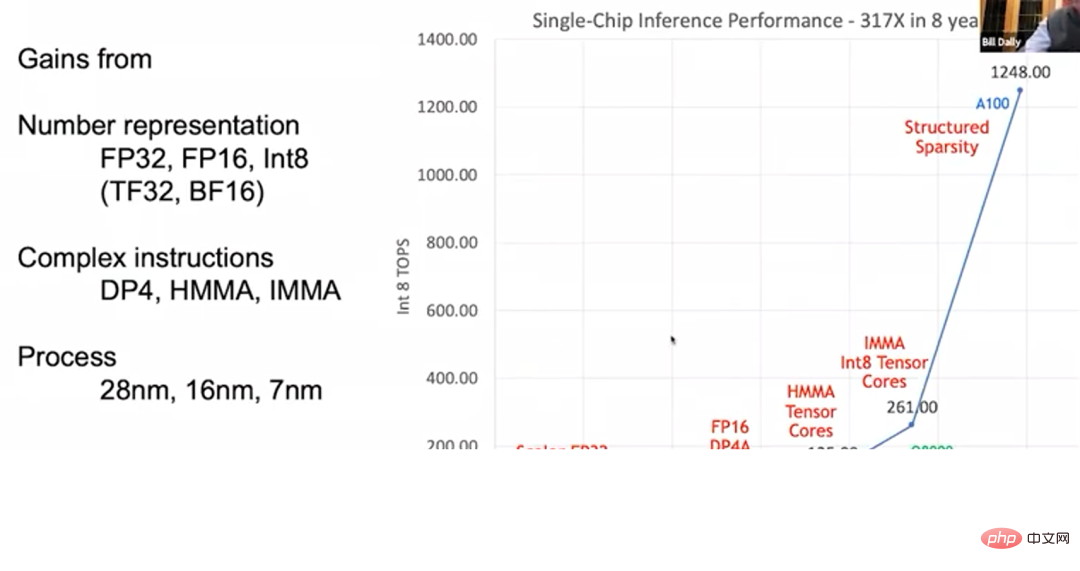

Du K20X en 2012 à l'A100 en 2020, les performances d'inférence du GPU ont augmenté jusqu'à 317 fois. C'est ce que nous appelons la « loi de Huang », et ce taux de développement est beaucoup plus rapide que la « loi de Moore ».

Les performances d'inférence du GPU se sont améliorées Mais contrairement à la « loi de Moore », dans la « loi de Huang », l'amélioration des performances du GPU ne repose pas entièrement sur les progrès de la technologie des processus. L'image ci-dessus marque ces types de GPU en noir, vert et bleu, ce qui signifie qu'ils utilisent trois technologies de processus différentes. Les premiers K20X et M40 utilisaient le processus 28 nm ; les P100, V100 et Q8000 utilisaient le processus 16 nm et l'A100 utilisait le processus 7 nm ; Les progrès de la technologie des processus ne peuvent augmenter les performances du GPU qu'à 1,5 ou 2 fois leur niveau d'origine. L'amélioration globale des performances, multipliée par 317, est principalement attribuée à l'amélioration de l'architecture du GPU et de la conception des circuits.

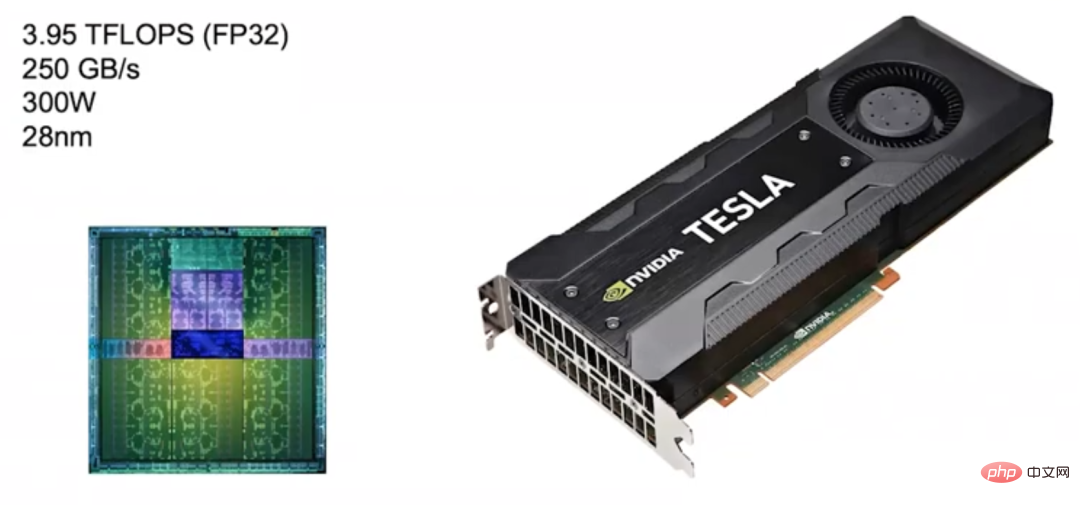

En 2012, NVIDIA a lancé un GPU à architecture Kepler, mais il n'a pas été conçu spécifiquement pour le deep learning. Nvidia n’a commencé à s’impliquer dans le deep learning qu’en 2010, et à cette époque, elle n’avait pas encore envisagé de personnaliser les produits GPU pour le deep learning.

Kepler (2012) Le scénario d'utilisation cible de Kepler est le traitement d'images et le calcul haute performance, mais il est principalement utilisé pour le traitement d'images. Par conséquent, il se caractérise par une puissance de calcul en virgule flottante élevée, avec sa vitesse de calcul FP32 (calcul à virgule flottante en simple précision) atteignant près de 4 TFLOPS et sa bande passante mémoire atteignant 250 Go/s. S'appuyant sur les excellentes performances de Kepler, NVIDIA le considère également comme la base de ses propres produits.

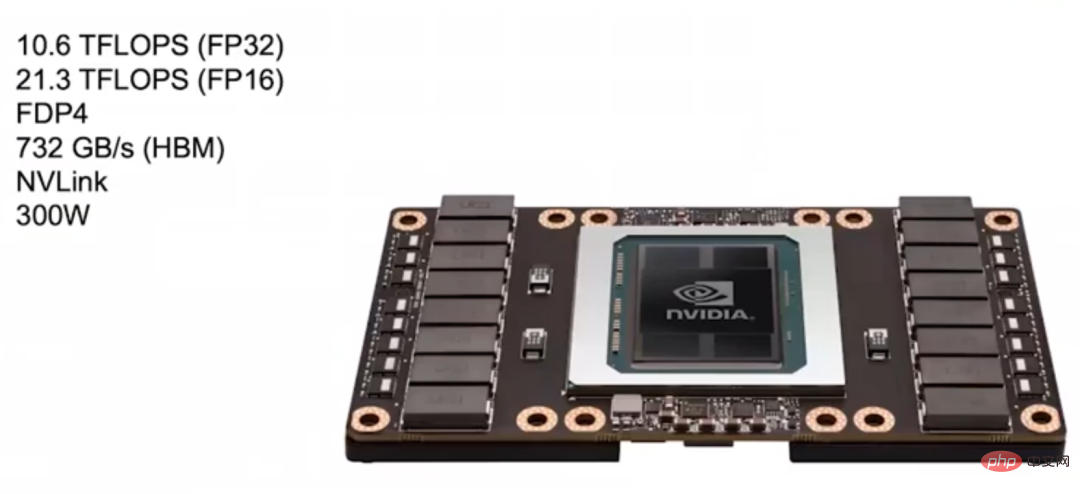

Pascal (2016) Plus tard, NVIDIA a lancé l'architecture Pascal en 2016, et sa conception est plus adaptée à l'apprentissage profond. Après quelques recherches, NVIDIA a découvert que de nombreux réseaux de neurones peuvent être entraînés avec FP16 (calcul à virgule flottante demi-précision), de sorte que la plupart des modèles de l'architecture Pascal prennent en charge les calculs FP16.

La vitesse de calcul FP32 de ce GPU Pascal dans l'image ci-dessous peut atteindre 10,6 TFLOPS, ce qui est beaucoup plus élevé que le GPU Kepler précédent, et son calcul FP16 est plus rapide, deux fois plus rapide que le FP32.

L'architecture Pascal prend également en charge des instructions plus complexes, telles que FDP4, de sorte que la surcharge liée à la récupération des instructions, au décodage et à la récupération des opérandes puisse être amortie en 8 opérations arithmétiques. Par rapport à l'instruction fusionnée précédente de multiplication-ajout (Fuse Multiply-Add) qui ne peut allouer la surcharge qu'à deux opérations arithmétiques, l'architecture Pascal peut réduire la consommation d'énergie causée par la surcharge supplémentaire et l'utiliser à la place pour des opérations mathématiques.

L'architecture Pascal utilise également la mémoire vidéo HBM, avec une bande passante de 732 Go/s, soit 3 fois celle de Kepler. La raison de l’augmentation de la bande passante est que la bande passante mémoire constitue le principal goulot d’étranglement dans l’amélioration des performances du deep learning. De plus, Pascal utilise NVLink pour connecter davantage de machines et de clusters GPU afin de mieux réaliser une formation à grande échelle.

Le système DGX-1 lancé par NVIDIA pour le deep learning utilise 8 GPU basés sur l'architecture Pascal.

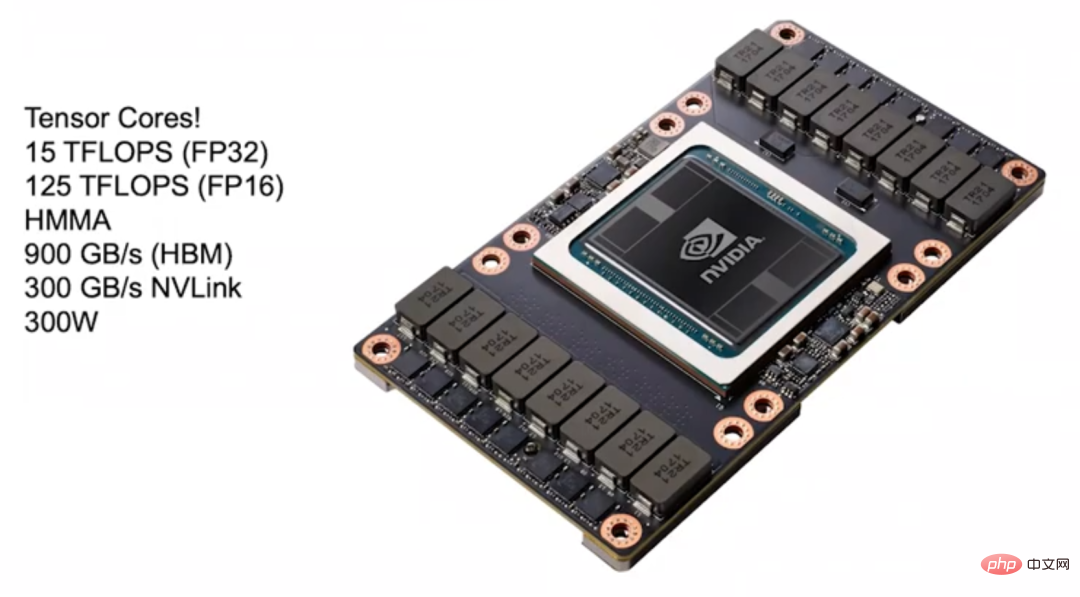

Volta (2017) En 2017, NVIDIA a lancé l'architecture Volta adaptée au deep learning. L'un de ses objectifs de conception est de mieux amortir les frais généraux d'instruction. Tensor Core est introduit dans l'architecture Volta pour l'accélération du deep learning. Tensor Core peut être connecté au GPU sous forme d'instructions. L'instruction clé est HMMA (Half Precision Matrix Multiply Accumulate), qui multiplie deux matrices 4×4 FP16 puis ajoute les résultats à une seule. Dans les matrices FP32, ce type d'opération est effectué. est très courant dans l’apprentissage profond. Grâce à l'instruction HMMA, les frais généraux liés à la récupération des instructions et au décodage peuvent être réduits aux 10 à 20 % d'origine grâce à l'amortissement.

Le reste est une question de charge. Si vous souhaitez surpasser les performances de Tensor Core, vous devez travailler dur sur la charge. Dans l'architecture Volta, une grande quantité de consommation d'énergie et d'espace est utilisée pour l'accélération de l'apprentissage profond, donc même si la programmabilité est sacrifiée, elle ne peut pas apporter beaucoup d'amélioration des performances.

Volta a également mis à niveau la mémoire vidéo HBM, avec une bande passante mémoire atteignant 900 Go/s, et utilise également une nouvelle version de NVLink, qui peut doubler la bande passante lors de la création d'un cluster. De plus, l'architecture Volta introduit également NVSwitch, qui peut connecter plusieurs GPU. En théorie, NVSwitch peut connecter jusqu'à 1 024 GPU pour créer une grande machine à mémoire partagée.

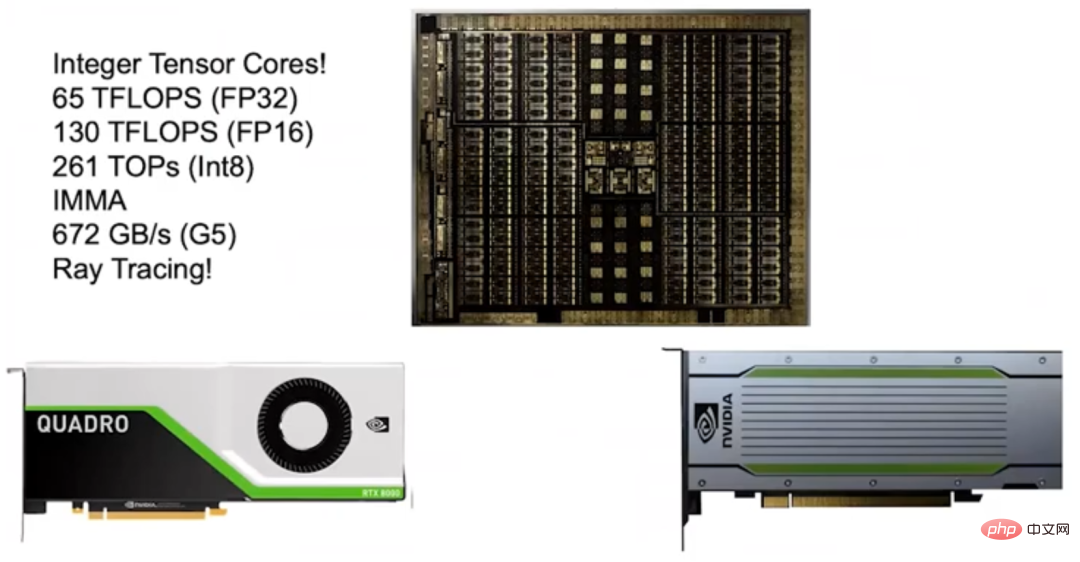

Turing (2018) En 2018, NVIDIA a lancé l'architecture Turing. En raison du grand succès du précédent Tensor Core, NVIDIA a lancé l'Integer Tensor Core. Étant donné que la plupart des réseaux de neurones peuvent être entraînés avec FP16 et que l'inférence ne nécessite pas une trop grande précision ni une grande plage dynamique, utilisez simplement Int8. Par conséquent, NVIDIA a introduit Integer Tensor Core dans l'architecture Turing, ce qui a doublé les performances.

L'architecture Turing utilise également la mémoire GDDR pour prendre en charge les modèles NLP et les systèmes de recommandation qui ont des exigences de bande passante élevées. À l’époque, certains mettaient en doute le fait que l’efficacité énergétique de l’architecture de Turing n’était pas aussi bonne que celle des autres accélérateurs du marché. Mais si vous calculez soigneusement, vous constaterez que l'architecture de Turing est en réalité plus économe en énergie, car Turing utilise la mémoire vidéo G5, tandis que d'autres accélérateurs utilisent la mémoire LPDDR. À mon avis, choisir la mémoire G5 est la bonne décision car elle peut prendre en charge des modèles ayant des exigences de bande passante élevées que des produits similaires ne peuvent pas prendre en charge.

Ce dont je suis très fier de l'architecture Turing, c'est qu'elle est également équipée d'un RT Core qui supporte le Ray Tracing. Nvidia n'a commencé ses recherches sur RT Core qu'en 2013 et a officiellement lancé RT Core cinq ans plus tard.

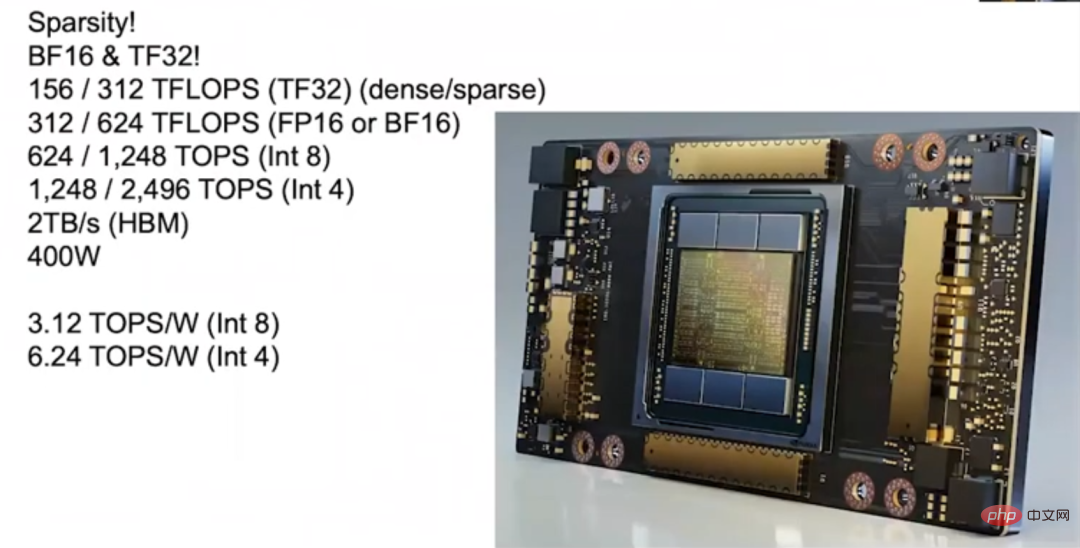

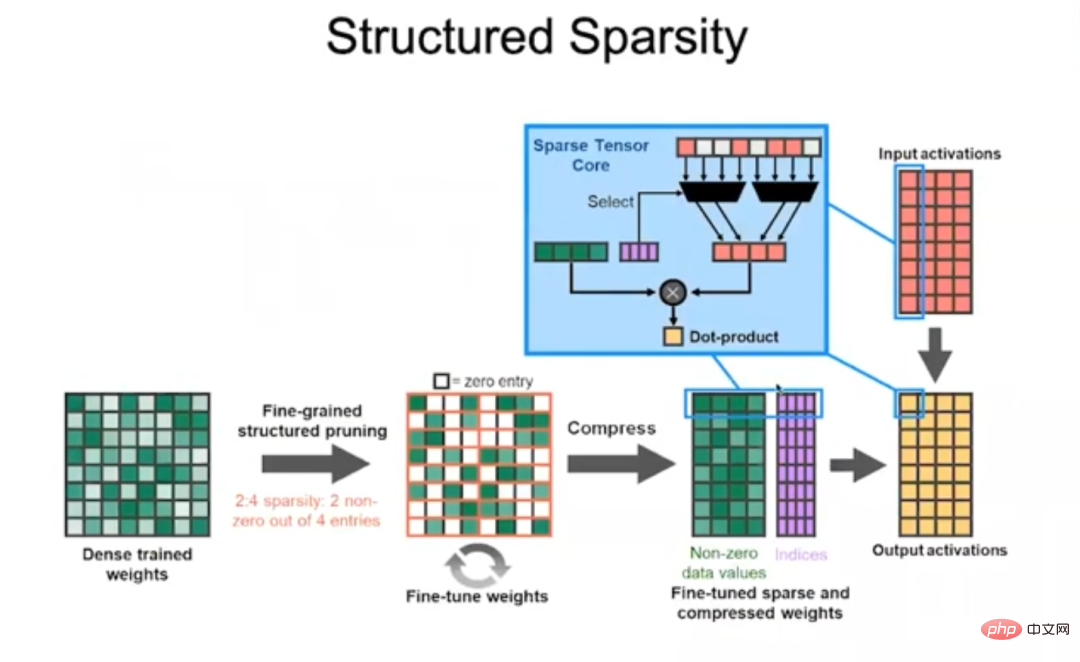

Ampere (2020) En 2020, NVIDIA a lancé l'architecture Ampere, qui a permis à l'A100 sorti cette année-là de réaliser un bond en performances, avec une vitesse d'inférence de plus de 1 200 Téraflops. L'un des grands avantages de l'architecture Ampere est qu'elle prend en charge la parcimonie. Nous avons constaté que la plupart des réseaux de neurones peuvent être fragmentés, c'est-à-dire que le réseau de neurones peut être « élagué » et qu'un grand nombre de poids peuvent être mis à 0 sans affecter sa précision. Mais différents réseaux de neurones peuvent être fragmentés à différents degrés, ce qui est un peu délicat. Par exemple, sans perdre en précision, la densité des réseaux de neurones convolutifs peut être réduite de 30 à 40 %, tandis que celle des réseaux de neurones entièrement connectés peut être réduite de 10 à 20 %.

Le point de vue traditionnel est qu'en raison du coût élevé d'exploitation des packages à matrice clairsemée, si la densité ne peut pas être réduite en dessous de 10 %, le compromis n'est pas aussi bon que l'exploitation de packages à matrice dense. Nous avons d'abord collaboré avec l'Université de Stanford pour étudier la parcimonie, puis avons construit de très bonnes machines qui peuvent fonctionner efficacement lorsque la densité de la matrice atteint 50 %, mais nous voulons rendre la matrice clairsemée plus efficace que la matrice dense en termes de puissance. Il reste encore difficile de rendre la matrice supérieure, et c'est là que nous voulons toujours percer.

Enfin, nous avons surmonté le problème et développé Ampère, et le secret est la parcimonie structurée.

Structured Sparse L'architecture Ampère stipule que pour 4 valeurs de la matrice, il ne peut y avoir plus de 2 valeurs non nulles, c'est-à-dire que les poids sont compressés par supprimer les valeurs non nulles. Déterminez quels poids doivent être conservés en saisissant le mot de code (mot de code), et utilisez le mot de code pour déterminer par quelles activations d'entrée ces poids non nuls doivent être multipliés, puis additionnez-les pour terminer l'opération de multiplication de points. Cette approche est très efficace, permettant à l'architecture Ampere de doubler les performances de la plupart des réseaux de neurones.

De plus, l'architecture Ampere présente de nombreuses innovations. Par exemple, Ampere intègre le format TF32 (TensorFloat-32), qui combine le bit exposant 8 bits du FP32 et le bit mantisse 10 bits du FP16. Ampere prend également en charge le format BFLOAT. Les bits d'exposant de BFLOAT sont les mêmes que ceux de FP32, et les bits de mantisse sont inférieurs à ceux de FP32, il peut donc être considéré comme une version réduite de FP32. Tous les formats de données ci-dessus prennent en charge le parcage structuré, donc que vous utilisiez FP16 et TF32 pour la formation, ou que vous utilisiez Int8 et Int4 pour l'inférence, vous pouvez obtenir les hautes performances apportées par le parcage structuré.

À mesure que l'Ampère s'améliore en quantification, il peut être appliqué à de nombreux réseaux de neurones et garantir des performances élevées. Ampere dispose de 6 piles HBM et la bande passante de la mémoire HBM a également été améliorée, atteignant 2 To/s. Lors de l'inférence de bout en bout, les capacités informatiques d'Ampère peuvent atteindre 3,12 TOPS/W (Int8) et 6,24 TOPS/W (Int4).

2 L'augmentation de 317 fois au cours de l'année est principalement attribuée à trois facteurs majeurs :

Le premier et le plus important est le développement de la représentation des nombres.

Deuxièmement, le GPU prend en charge les instructions complexes.

L'architecture Pascal a ajouté des instructions de multiplication de points, puis les architectures Volta, Turing et Ampère ont ajouté des instructions de produit matriciel pour répartir les frais généraux. Conserver un moteur programmable dans le GPU peut apporter de nombreux avantages. Il peut être aussi efficace qu'un accélérateur car chaque instruction effectue tellement de tâches que l'amortissement des frais généraux par instruction est presque négligeable.Enfin, les progrès de la technologie des procédés.

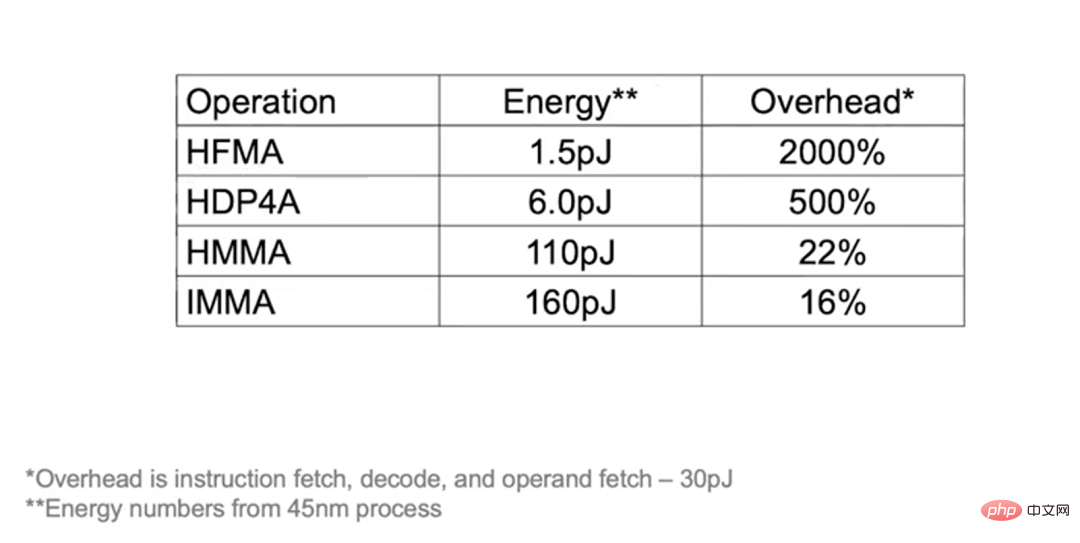

Le processus de fabrication des puces est passé de 28 nanomètres aux 7 nanomètres actuels, ce qui a apporté une certaine contribution à l'amélioration des performances du GPU. L'exemple suivant peut vous aider à mieux comprendre l'effet du partage des coûts : si vous effectuez une opération HFMA, les opérations "multiplier" et "ajouter" ne totalisent que 1,5pJ (Picojoules, Picojoules), lors de la récupération des instructions, du décodage et de l'obtention des opérandes. des frais généraux de 30pJ, et le coût atteindra 2 000 % une fois amorti.

Et si vous effectuez des opérations HDP4A, vous pouvez allouer la surcharge à 8 opérations, réduisant ainsi la surcharge à 500 %. Pour le fonctionnement du HMMA, puisque la majeure partie de la consommation d'énergie est utilisée pour la charge, les frais généraux ne sont que de 22 %, et l'IMMA est encore plus faible, de 16 %. Par conséquent, même si la recherche de la programmabilité ajoute une petite quantité de frais généraux, les améliorations de performances pouvant être obtenues en adoptant une conception différente sont plus importantes.

3 Comment les GPU sont connectés. Nous avons introduit NVLink dans l'architecture Pascal, puis l'architecture Volta a adopté NVLink 2 et l'architecture Ampere a adopté NVLink 3. La bande passante de chaque génération d'architecture a doublé. De plus, nous avons lancé la première génération de NVSwitch sur l'architecture Volta et la deuxième génération sur l'architecture Ampere. Grâce à NVLink et NVSwitch, de très grands clusters GPU peuvent être créés. De plus, nous avons également lancé la box DGX.

Boîte DGX

Boîte DGX

En 2020, NVIDIA a acquis Mellanox, elle peut donc désormais fournir un ensemble complet de solutions de centre de données, notamment des commutateurs et des interconnexions, pour créer de grands clusters GPU. De plus, nous sommes équipés du DGX SuperPOD, qui se classe dans le top 20 de la liste AI Performance Record 500. Dans le passé, les utilisateurs devaient personnaliser les machines, mais il leur suffit désormais d'acheter une machine préconfigurée capable de déployer DGX SuperPOD pour obtenir les hautes performances apportées par DGX SuperPOD. De plus, ces machines sont bien adaptées au calcul scientifique.

Dans le passé, il fallait plusieurs mois pour former un seul grand modèle de langage avec une seule machine, mais l'efficacité de la formation peut être considérablement améliorée en créant un cluster GPU. Par conséquent, en optimisant les connexions du cluster GPU et en améliorant les performances d'un seul GPU. sont tout aussi importants.

4 Deep Learning Accelerator : un terrain d'essai pour les nouvelles technologies

Parlons ensuite du travail de recherche et développement de l'accélérateur de NVIDIA. Nvidia considère les accélérateurs comme un moyen de tester de nouvelles technologies, et les technologies performantes seront éventuellement appliquées aux GPU grand public. L'accélérateur peut être compris de cette façon : il dispose d'une unité de multiplication matricielle entrée par la hiérarchie de la mémoire, et la prochaine chose à faire est d'utiliser la majeure partie de la consommation d'énergie pour les calculs de multiplication matricielle au lieu de la gestion des données.

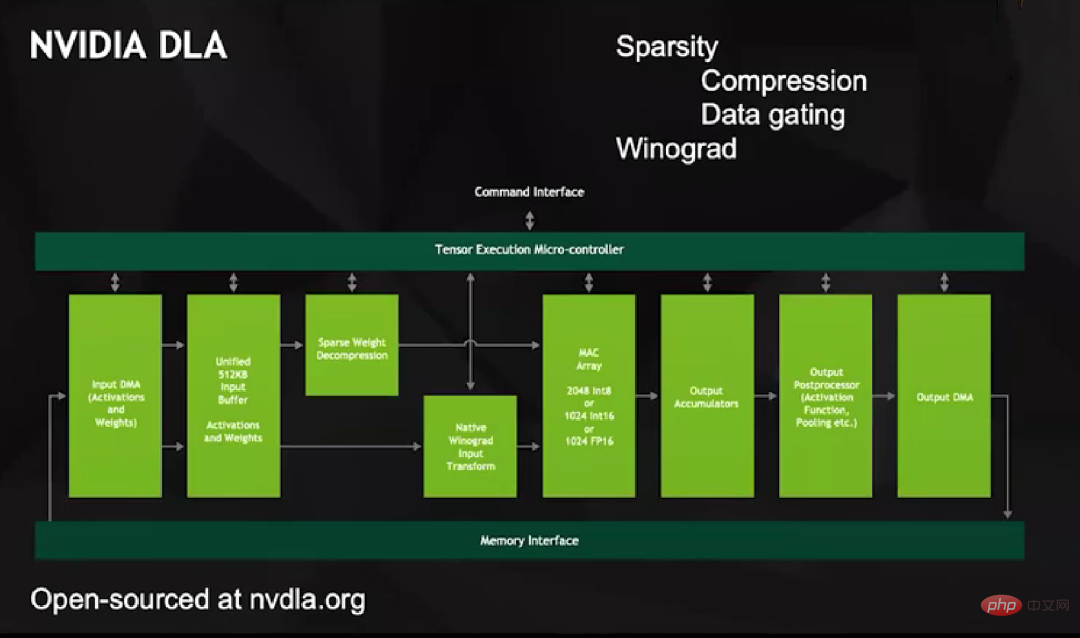

Pour atteindre cet objectif, nous avons lancé le projet NVIDIA DLA vers 2013. Il s'agit d'un produit open source doté de fonctionnalités de support très complètes, qui ne diffère pas des autres accélérateurs d'apprentissage profond. Mais DLA dispose d'une large baie MAC qui prend en charge 2 048 opérations Int8, 1 024 Int16 ou 1 024 FP16.

DLA a deux fonctionnalités uniques : Premièrement, il prend en charge la sparsification. Nous partons du fruit le plus simple. Tous les transferts de données, y compris du DMA vers Unified Buffer et du Unified Buffer vers le tableau MAC, impliquent uniquement des valeurs non nulles. Nous décidons quels éléments sont laissés lors du codage, puis résolvons ces éléments. puis entrez dans le tableau MAC pour le calcul.

La méthode de décompression DLA est plus intelligente. Elle n'entre pas de valeurs nulles dans le tableau MAC, car cela transformerait une série de données en zéros. Au lieu de cela, il crée une ligne distincte pour représenter la valeur zéro, et lorsque le multiplicateur reçoit cette ligne sur l'une ou l'autre des entrées, il se verrouille sur les données contenues dans le multiplicateur, puis envoie la sortie, qui n'augmente d'aucune valeur numérique. Le portail est très économe en énergie.

La seconde est de soutenir la transformation de Winograd au niveau matériel. Vous savez, si vous voulez faire une convolution, par exemple, un noyau de convolution m×n, vous avez besoin de n 2 multiplicateurs et additionneurs dans le domaine spatial, mais si vous le faites dans le domaine fréquentiel, vous n'avez besoin que de point par point. multiplication. Par conséquent, les opérations à grand noyau de convolution sont plus efficaces dans le domaine fréquentiel que dans le domaine spatial. En fonction de la taille du noyau de convolution, la transformation Winograd peut améliorer les performances de certains réseaux d'images par 4.

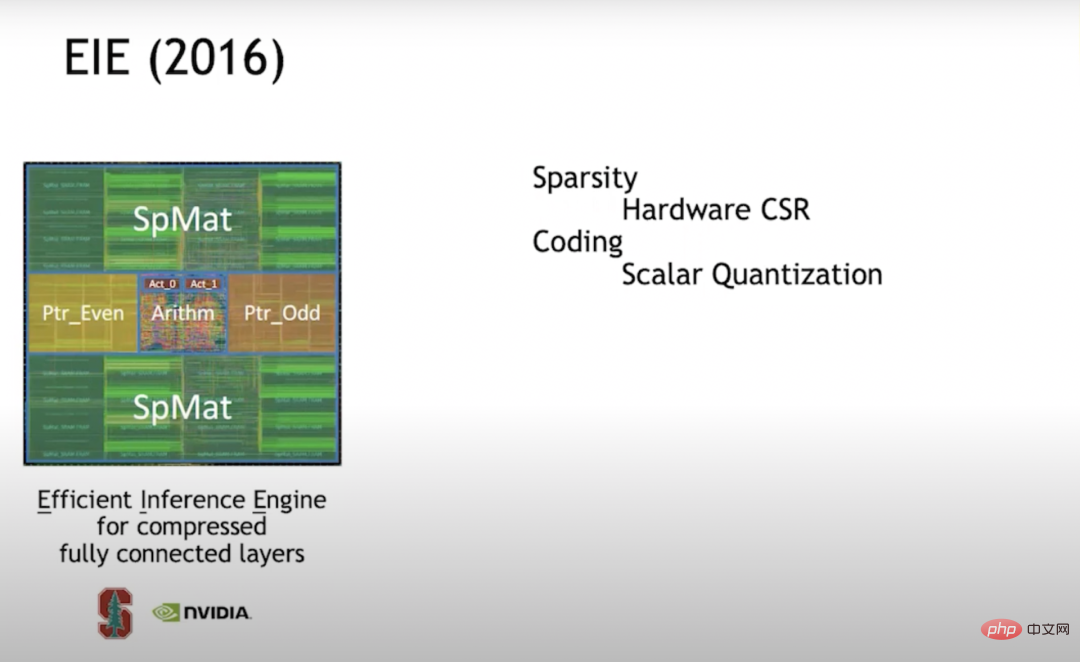

EIE (2016) En 2016, j'ai étudié l'EIE (Efficient Inference) à Stanford avec mon étudiant d'alors Han Song (professeur adjoint MIT EECS, ancien co-fondateur de Shenjian Technology) Engine ). Ce fut l’une des premières explorations de la sparsification. Nous prenons en charge la représentation matricielle CSR (Compressed Sparse Row) au niveau matériel. Cette approche est très efficace lorsque la densité est de 50 %, elle est encore plus économe en énergie que le calcul pleine densité.

Plus tard, j'ai découvert que si vous souhaitez rendre l'accélérateur plus efficace, vous devez construire un tableau d'unités vectorielles afin que chaque moteur effectue non seulement une seule multiplication-accumulation, mais que chaque PE (élément de traitement) effectue 16 × 16 = 256 par cycle de multiplication et d'addition. Mais lorsque nous avons commencé à construire des réseaux de cellules vectorielles, nous avons eu du mal à atteindre efficacement la parcimonie, nous nous sommes donc tournés vers la parcimonie structurée.

Lorsque EIE traite l'unité scalaire, il stocke la structure du pointeur dans une mémoire séparée, puis traite la structure du pointeur via l'étape pipeline pour déterminer quelles données peuvent être multipliées, puis effectue la multiplication et place le résultat de l'opération dans l'emplacement approprié. L’ensemble de ce processus fonctionne de manière très efficace. Nous avons également constaté qu'en plus de « l'élagage » pour atteindre la parcimonie, la méthode visant à améliorer l'efficacité informatique des réseaux neuronaux implique également la quantification. Par conséquent, nous avons décidé d’utiliser la quantification par codebook. La quantification du codebook est le meilleur moyen d'améliorer l'efficacité des données exprimées en bits. Nous nous sommes donc entraînés sur le livre de codes.

Il s'avère que si vous pouvez utiliser la rétropropagation pour capturer la descente de gradient, vous pouvez appliquer la rétropropagation à n'importe quoi. Nous avons donc utilisé la rétropropagation dans le livre de codes pour former l'ensemble optimal de mots de code pour une précision donnée. En supposant que le livre de codes comporte 7 bits, vous obtiendrez alors 128 mots de code. Nous trouverons les 128 mots de code optimaux dans le réseau neuronal pour la formation.

La quantification Codebook est confrontée à un problème : la surcharge des opérations mathématiques est élevée. Car quelle que soit la taille du livre de codes et sa valeur réelle, vous devez le rechercher dans la RAM (mémoire vive). Les valeurs réelles doivent être représentées avec une grande précision et vous ne pouvez pas représenter exactement ces mots de passe. Nous consacrons donc beaucoup d’efforts aux mathématiques de haute précision. D'un point de vue compression, cela fonctionne très bien, mais d'un point de vue mathématique énergétique, ce n'est pas très rentable, nous avons donc abandonné cette technologie dans les travaux ultérieurs.

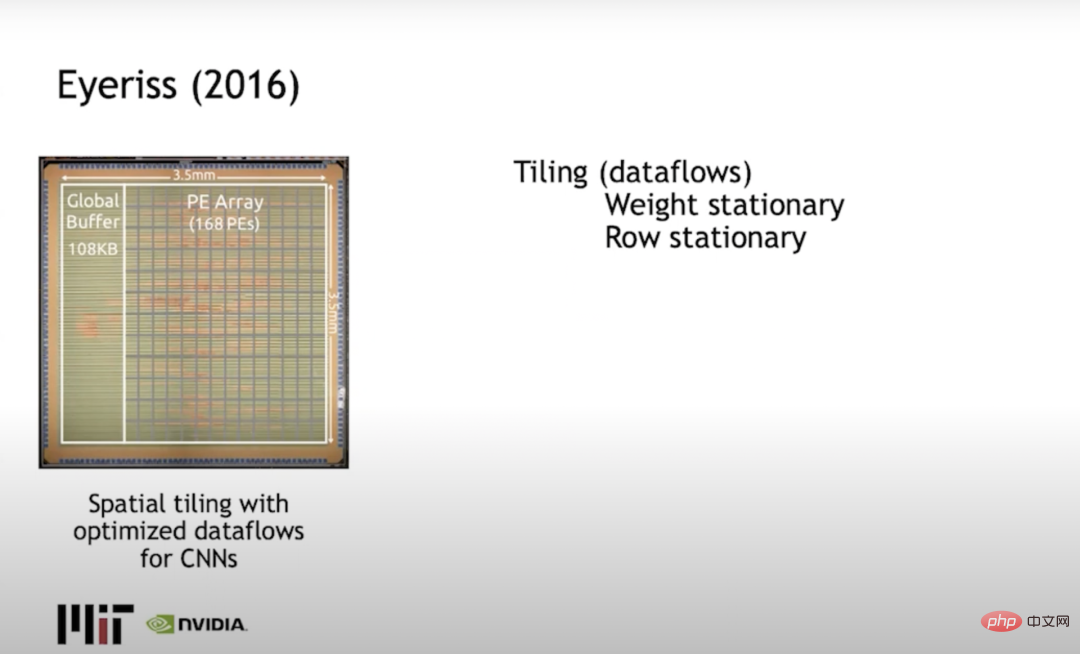

Eyeriss (2016) Joel Emer (tous deux chez NVIDIA et MIT) et Vivienne Sze au MIT ont construit Eyeriss, qui résout principalement le carrelage. Le problème, ou comment limiter le calcul, est pour minimiser le mouvement des données. Une approche typique consiste à utiliser des lignes stationnaires, en répartissant les poids en lignes et les activations de sortie en colonnes, et en minimisant l'énergie consommée par le mouvement des données.

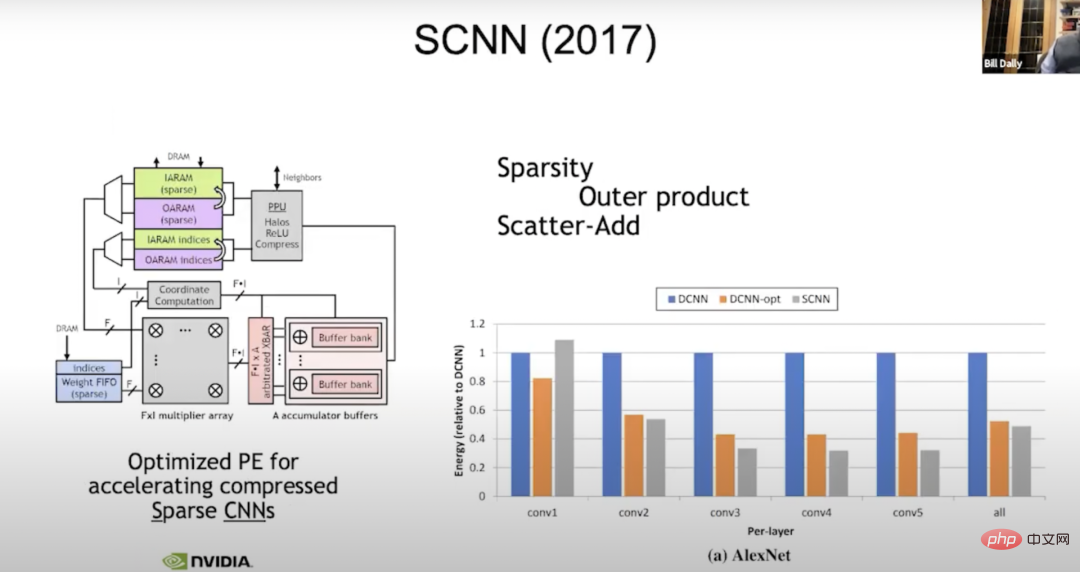

SCNN (2017) Nous menons toujours des recherches sur la rareté. En 2017, nous avons construit une machine appelée SCNN (Sparse CNNs) pour la compilation clairsemée (une évolution des réseaux de neurones). Nous avons déplacé tous les problèmes complexes liés à la gestion de la parcimonie vers la sortie. Lisez toutes les activations d'entrée et déterminez où elles doivent aller, donc le "vecteur f-wide" ici est une activation d'entrée vectorielle typique.

Nous lirons quatre activations d'entrée à la fois, quatre poids, et chaque poids doit être multiplié par chaque activation d'entrée. C'est juste une question de savoir où mettre le résultat, donc on multiplie f par f.

Dans le calcul des coordonnées, nous prenons l'exposant de l'activation d'entrée et le poids, et calculons la position où le résultat additionné doit être dans l'activation de sortie. Ensuite, un calcul de dispersion des données (scatter_add) est effectué sur ces tampons accumulateurs. Avant cela, tout fonctionnait parfaitement. Mais il s’avère que transférer les irrégularités vers la sortie n’est pas une bonne idée, car dans la sortie, la précision est en réalité la plus large. Lorsque vous avez tendance à accumuler, vous effectuez huit bits de pondération, huit bits d'activation, et le total est de 24 bits. Ici, nous utilisons de larges accumulateurs pour effectuer de nombreux mouvements de données, ce qui est préférable à un déplacement de données plus intensif. Cependant, l'amélioration n'est pas aussi grande qu'on l'imaginait, peut-être 50 % de l'énergie de l'unité de densité.

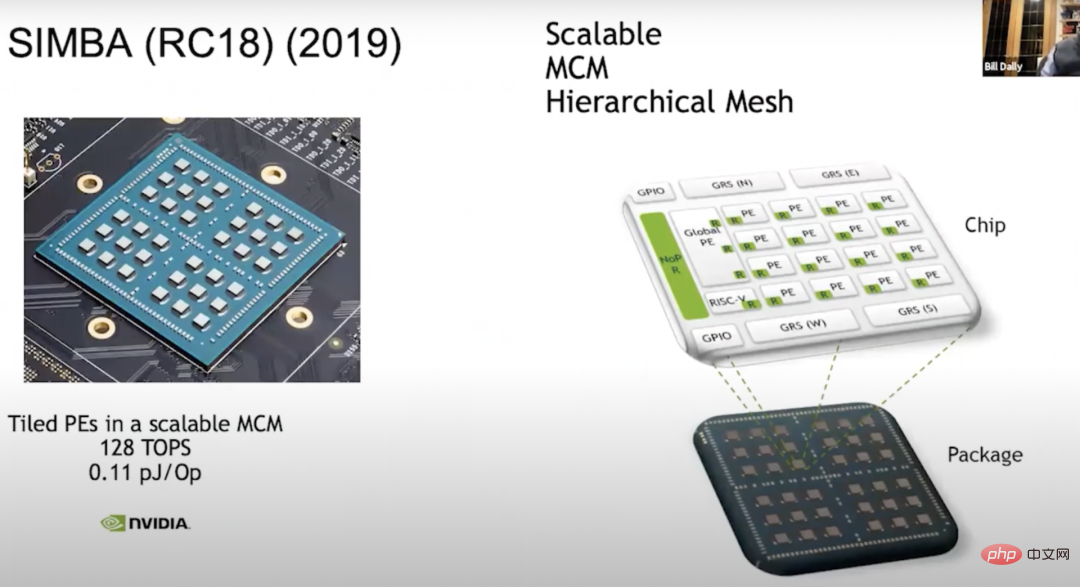

SIMBA (RC18) (2019) Une autre chose que nous ferons est de construire un module multi-puces - SIMBA (RC18) avec les accélérateurs existants, en 2018. L'idée de Cette recherche a eu lieu en 2008, et cette puce a également démontré de nombreuses technologies ingénieuses. Il possède une bonne architecture PE et la puce fournit une technologie de signalisation très efficace au milieu. Désormais, l'architecture s'étend jusqu'à 36 puces complètes, dont chacune a une matrice PE 4x4, et au sein de cette unité, chaque PE a 8 unités vectorielles larges, nous pouvons donc obtenir 128 TOPS de puissance de calcul, chaque Op a 0,1 pJ, ce qui est approximativement équivalent à 10 TOPS/W.

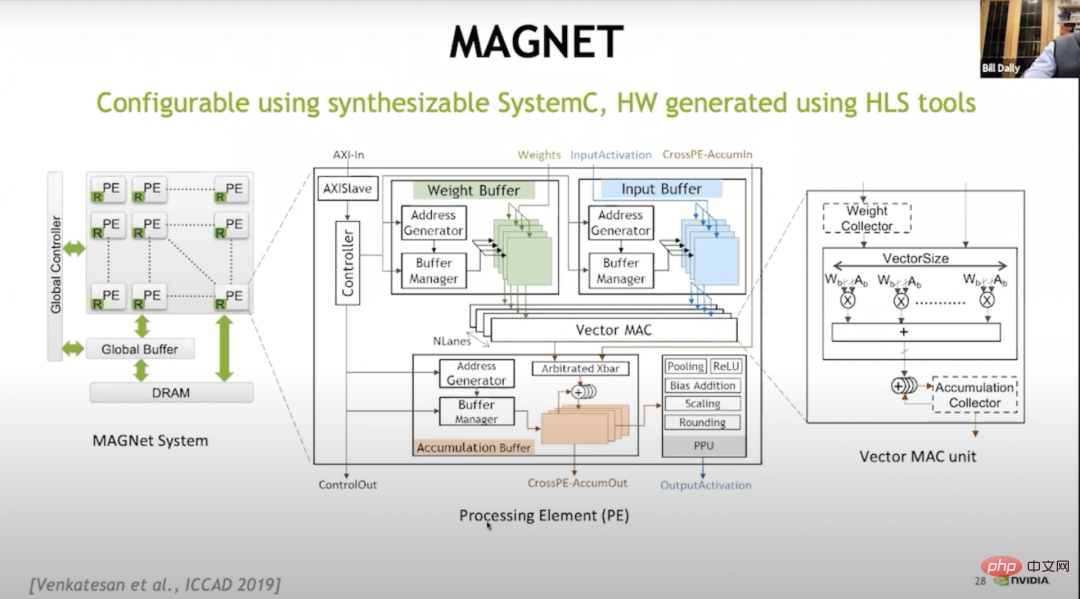

Nous avons beaucoup appris sur les compromis. Nous avons réalisé que construire ces tableaux PE revenait à construire un très grand espace de conception, sur la façon de construire la hiérarchie de la mémoire, de planifier les données, etc., nous avons donc construit un système appelé MAGNET.

MAGNET L'image ci-dessus est un système d'exploration de l'espace de conception publié à l'ICCAD (Conférence internationale sur la conception assistée par ordinateur) en 2019. Il est principalement utilisé pour énumérer son espace de conception, tel que : chaque unité vectorielle doit have Quelle est la largeur, combien d'unités vectorielles y a-t-il par PE, quelle est la taille du tampon de poids, quelle est la taille du tampon accumulateur, quelle est la taille du tampon d'activation, etc. Plus tard, nous avons découvert que nous devions effectuer un autre niveau de mise en cache, nous avons donc ajouté un collecteur de poids et un collecteur d'accumulateurs.

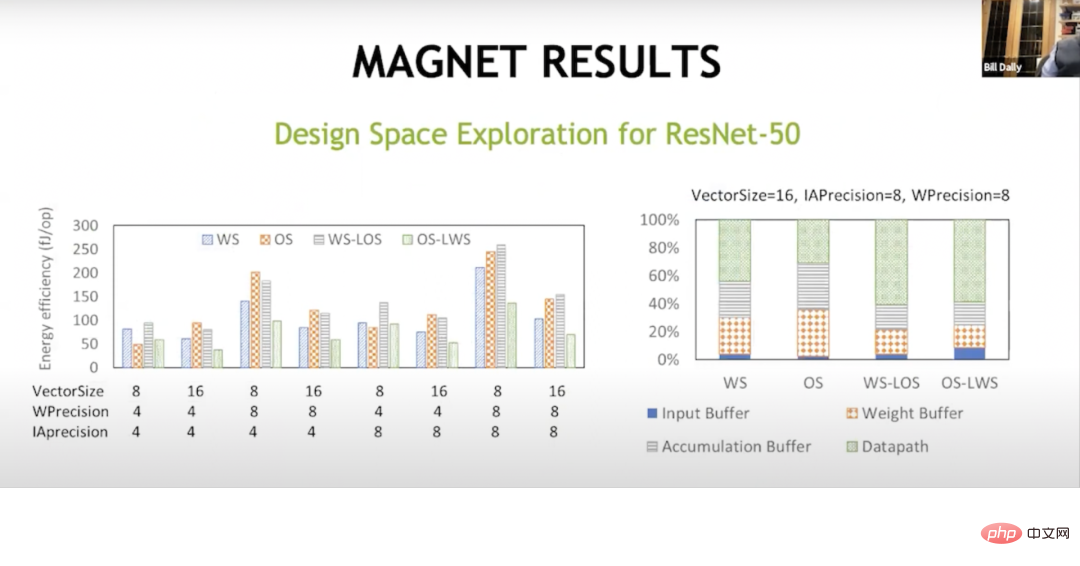

RÉSULTATS MAGNET Avec ce niveau supplémentaire de mise en cache, nous avons finalement réussi. Cela montre que le flux de données ici est différent et que le flux de données à poids fixe a été initialement réalisé par Sze et Joel. Vous consacrez la majeure partie de votre énergie à des choses en dehors du chemin de données, comme dans les tampons d'accumulation, les tampons de poids et les tampons d'entrée. Mais avec ces flux de données hybrides, les poids sont fixes, les sorties locales sont fixes, les sorties sont fixes, les poids locaux sont fixes, vous pouvez obtenir près des deux tiers de l'énergie dans les opérations mathématiques et vous pouvez réduire l'énergie dépensée dans ces matrices de mémoire. , donc dans le traitement de la mémoire à un autre niveau de la hiérarchie. Cela porte désormais la performance par watt à environ 20 TOPS.

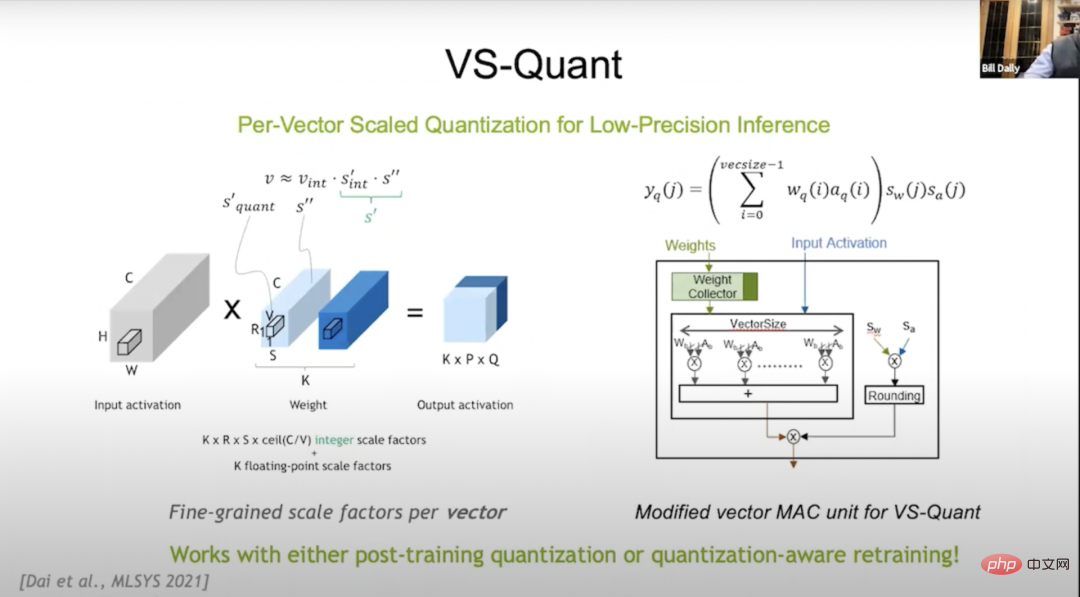

VS-Quant En 2021, lors de la conférence MLSYS (The Conference on Machine Learning and Systems, Machine Learning and Systems Conference), nous avons présenté VS-Quant comme moyen de Explorer une méthode de quantification rentable en termes de bits de compression (où la quantification du livre de codes fonctionne bien) et de surcharge mathématique. Nous utilisons une représentation entière mais souhaitons la mettre à l'échelle afin que la plage dynamique des entiers puisse être représentée.

Mais il s'avère que si vous appliquez cela à l'ensemble du réseau neuronal maintenant, cela ne fonctionne pas très bien car il y a beaucoup de plages dynamiques différentes sur le réseau neuronal, donc la clé de VS-Quant est : nous avons un petit vecteur relativement petit qui impose un facteur d'échelle séparé, approximativement en effectuant l'opération ci-dessus sur 32 poids, la plage dynamique sera beaucoup plus petite. Nous pouvons mettre ces entiers au-dessus, et nous pouvons également les ajuster et les optimiser.

Peut-être que nous n’avons pas représenté les valeurs aberrantes avec précision, mais le reste des chiffres était mieux représenté. De cette manière, nous pouvons échanger des poids et des activations de précision relativement faible contre une plus grande précision. Nous avons donc maintenant plusieurs facteurs d’échelle : l’un est le facteur de poids et l’autre est le facteur d’activation.

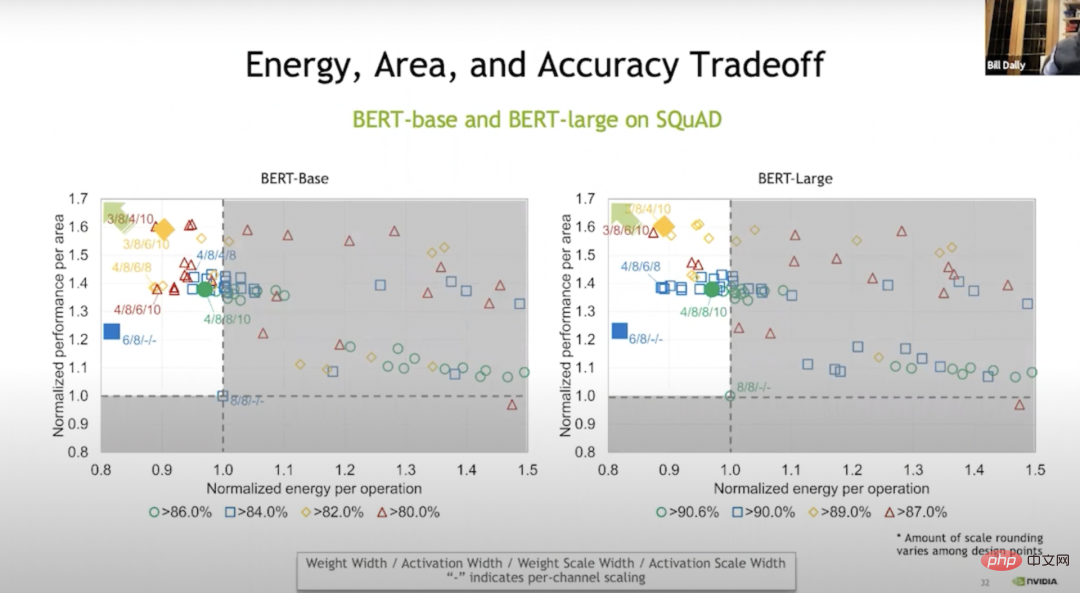

Compromis entre l'énergie, la surface et la précision Nous effectuons essentiellement ces opérations au niveau vectoriel, et les résultats sont tels qu'indiqués dans Bert-base. Par rapport à l'entraînement sans poids, nous pouvons économiser 20 % d'énergie et 70 % d'espace dans certains cas grâce à l'entraînement. La couleur verte dans la figure ci-dessus indique qu'il n'y a pratiquement aucune perte de précision ; . Haut ou bas. Mais même au niveau bleu, la précision est assez élevée.

Avec VS-Quant et quelques autres ajustements, nous avons fait un essai sur ces modèles de langage. Exécuter sur un modèle de langage est beaucoup plus difficile que d'exécuter sur un modèle d'image d'environ 120 TOPS/W.

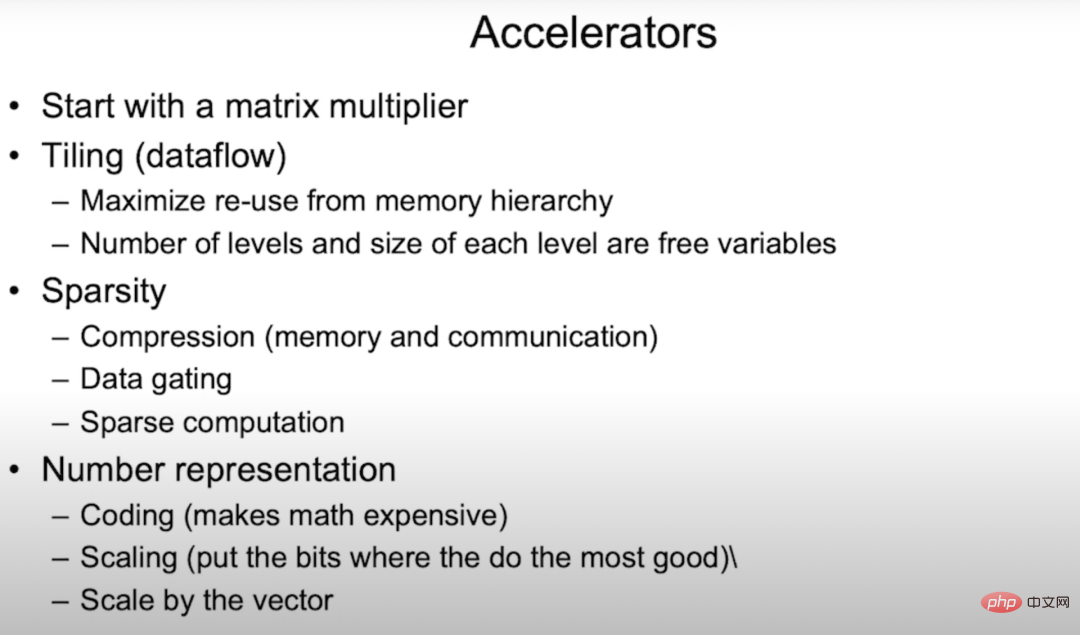

AccélérateursDonc pour l'accélérateur, vous devez d'abord faire un multiplicateur matriciel. Nous devons proposer une méthode de carrelage, une méthode de calcul à sept boucles imbriquées utilisant des réseaux de neurones. Il s'agit essentiellement de copier certaines de ces boucles sur différentes couches du système de mémoire pour maximiser la réutilisation de la hiérarchie de mémoire de chaque couche et minimiser la gestion des données.

Nous avons également étudié la parcimonie, qui est plutôt bonne en compression. Cela augmente essentiellement la bande passante de la mémoire et la bande passante de communication et réduit l'énergie de la mémoire et de la communication. Le prochain niveau de développement de parcimonie est le suivant : lorsque vous avez une valeur nulle, envoyez simplement une ligne distincte représentant la valeur zéro sans avoir à passer à 8 ou 16 bits à chaque boucle.

L'architecture Ampere peut réutiliser les multiplicateurs en utilisant la parcimonie structurée, ce qui est une méthode très efficace et ne nécessite que la surcharge de quelques multiplexeurs (fondamentalement négligeable). Nous pouvons également réutiliser le multiplicateur lors d'opérations de pointeur, ce qui nous permet d'obtenir 2 fois plus de performances. La représentation des nombres est très importante. Nous avons commencé avec EIE (Note du traducteur : Efficient Inference Engine, article du Dr Han Song à l'ISCA 2016. Accélération matérielle réalisée de réseaux neuronaux clairsemés compressés. ESE avec sa méthode approximative a remporté le meilleur article du FPGA2017.), en essayant de créer un livre de codes, mais cela rend la mise à l'échelle mathématiquement coûteuse.

Enfin, la technologie testée avec succès dans l'accélérateur sera éventuellement appliquée au GPU. C'est un bon moyen de tester. Nous pensons que le GPU est une plate-forme pour le matériel spécifique à un domaine. Son système de mémoire est très bon et le réseau est fluide, permettant aux applications d'apprentissage en profondeur de s'exécuter très rapidement.

5 L'avenir du matériel d'apprentissage profond

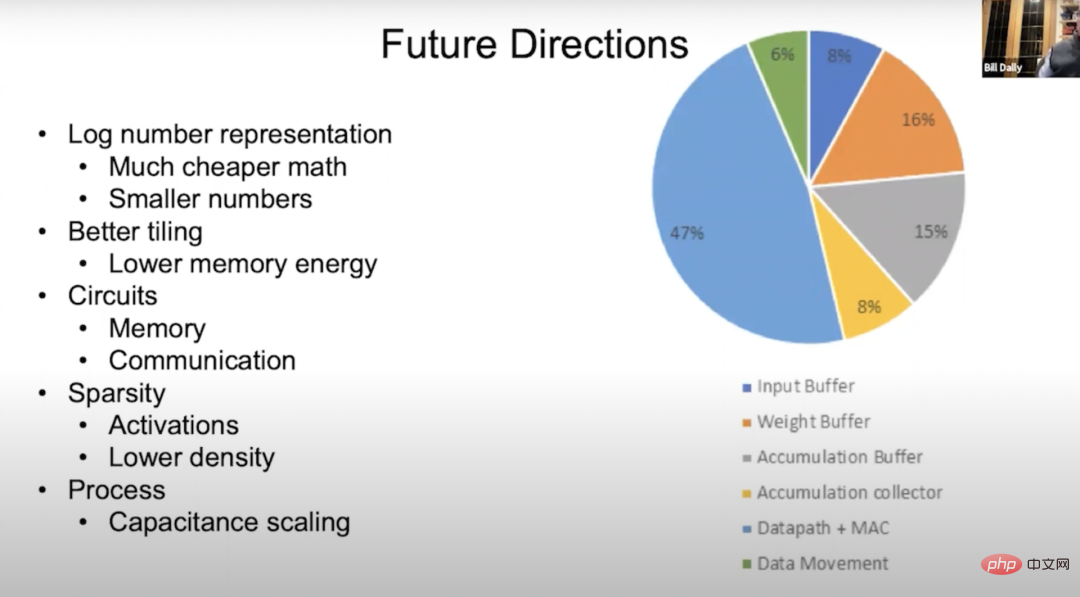

Orientations futures Parlons de l'avenir du matériel d'apprentissage profond. L'image ci-dessus est un diagramme circulaire de flux d'énergie. Vous pouvez voir que la majeure partie de l'énergie circule vers le chemin des données. Environ 50 % concernent des opérations mathématiques, nous voulons donc que les opérations mathématiques consomment moins d'énergie ; .et le mouvement des données. Les verts sont des transferts de données, et les autres sont des tampons d'entrée, des tampons de poids, des tampons d'accumulation et des collecteurs d'accumulation, avec des proportions différentes. Nous cherchons à réduire la consommation d'énergie des opérations mathématiques, et l'un des meilleurs moyens est de la déplacer vers un système logarithmique. Parce que dans un système logarithmique, la multiplication devient une addition, et l’addition est généralement beaucoup moins gourmande en énergie. Une autre façon consiste à convertir en une valeur plus petite, ce qui peut être obtenu via VS-Quant. En quantifiant plus précisément, nous pouvons obtenir une précision équivalente à partir de réseaux neuronaux avec des nombres de précision inférieure.

Nous espérons faire mieux avec le carrelage, comme peut-être en ajoutant plus de couches dans la hiérarchie de la mémoire dans certains cas, ce qui peut réduire l'énergie de la mémoire et également rendre les circuits de mémoire et les circuits de communication plus efficaces. L'effet est meilleur. Sur l'architecture Ampere, le travail que nous effectuons déjà sur la parcimonie structurée est un bon début, mais je pense que nous pouvons faire mieux en réduisant la densité ou en choisissant plusieurs densités pour ajuster les activations et les poids. Avec l’approfondissement de la recherche, la technologie des procédés apportera également certains progrès en matière de mise à l’échelle de la capacité.

6 Résumé

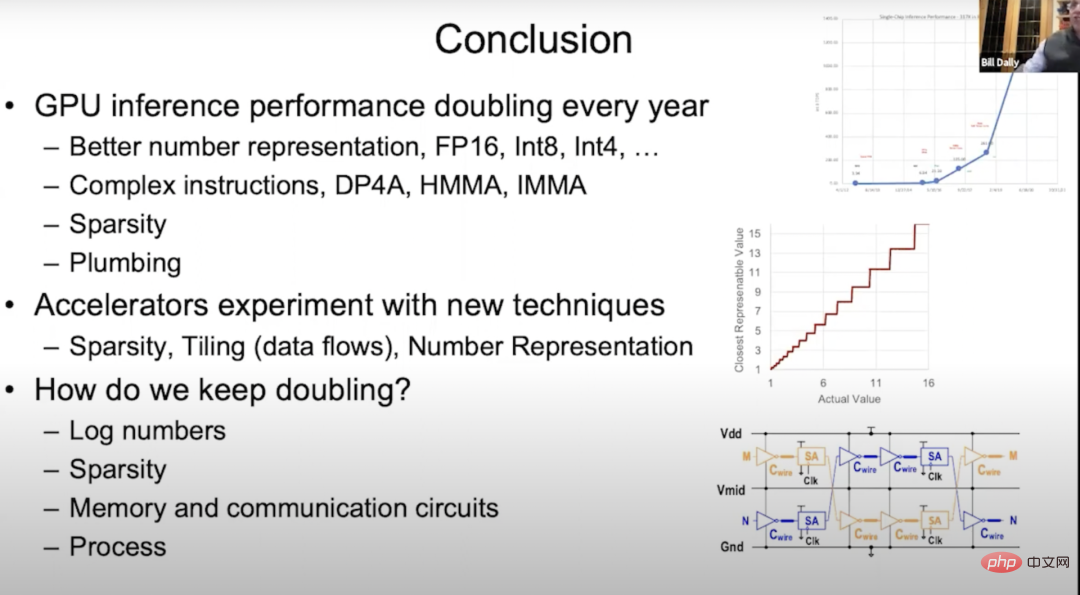

Depuis la sortie de l'architecture Kepler en 2012, les performances d'inférence du GPU ont doublé chaque année. Cette évolution est en grande partie due à une représentation numérique toujours meilleure. Cette fois, nous avons parlé de beaucoup de contenu, comme du FP32 au FP16 en passant par Int8 puis Int4 de l'architecture Kepler ; nous avons parlé de l'utilisation de produits scalaires plus complexes en allouant une surcharge d'instructions, nous avons parlé de l'architecture Pascal, de la multiplication matricielle semi-précision ; et s'accumulent dans l'architecture Volta, multiplication et accumulation de matrices entières dans l'architecture Turing, et dans l'architecture Ampère et la parcimonie structurelle.

J'ai très peu parlé de Plomberie, mais la Plomberie est très importante. La plomberie est utilisée pour aménager le système de mémoire et le réseau sur puce, afin que les puissants cœurs Tensor puissent être pleinement utilisés. Pour que les cœurs Tensor effectuent un gigabit d'opérations par seconde dans l'architecture Turing et alimentent les données pour exécuter des benchmarks communs, l'organisation de la mémoire de branche, de la mémoire sur puce et de l'interconnexion entre eux et le fonctionnement normal est très importante.

En regardant vers l'avenir, nous sommes prêts à essayer d'appliquer diverses nouvelles technologies à l'accélérateur. Comme mentionné précédemment, nous avons mené de nombreuses expériences sur les techniques de parcimonie et de carrelage, et expérimenté différentes techniques de carrelage, représentations numériques, etc. dans le projet MAGNet. Mais nous ressentons encore beaucoup de pression, car les progrès du deep learning dépendent en réalité de l’amélioration continue des performances matérielles. Doubler les performances d’inférence du GPU chaque année est un défi de taille.

En fait, les cartes en main sont presque jouées, ce qui signifie que nous devons commencer à développer de nouvelles technologies. Voici les quatre directions qui, à mon avis, méritent notre attention :

Tout d'abord, étudier de nouvelles. représentations numériques, par exemple, le numéro de journal et un schéma de quantification plus intelligent qu'EasyQuant

Ensuite, continuez à étudier la rareté en profondeur

Ensuite, étudiez les circuits de stockage et les circuits de communication ;

Enfin, améliorer la technologie des processus existante. 7

Répondre aux questions du public

Dejan Milojicic : Quelle taille de convolution matricielle est nécessaire pour convertir l'algorithme de Winograd en une implémentation de convolution plus efficace ?

Bill Dally : Je pense que la convolution matricielle 3×3 est très efficace. Bien entendu, plus la convolution est grande, plus l’efficacité est élevée.

Dejan Milojicic : Comment est calculée la bande passante mémoire de la mémoire à haute bande passante (HBM) ? La mémoire est-elle accessible via tous les cœurs GPU en même temps ?

Bill Dally : Chaque pile HBM a un tampon de trame séparé, comme l'architecture Ampere a six piles. Notre bande passante mémoire est calculée avec chaque contrôleur de mémoire fonctionnant à pleine bande passante. Il y a une couche de cache entre chaque cœur GPU, et la bande passante de notre réseau sur puce est plusieurs fois supérieure à la bande passante du HBM, donc fondamentalement, nous n'avons besoin que d'exécuter une petite partie du multiprocesseur de streaming pour saturer le HBM.

Dejan Milojicic : Comment fonctionne l'informatique distribuée avec NVLink ? Qui décide quel calcul effectuer ? Où et quelle surcharge est encourue lors de la collecte de données dispersées sur plusieurs GPU ?

Bill Dally : Le programmeur décidera où placer les données et les threads, et il vous suffit de démarrer les threads et les données sur le GPU et de déterminer où ils s'exécutent. Un avantage majeur des systèmes connectés via NVLink est qu'il s'agit d'un espace d'adressage partagé et que la surcharge liée à la transmission de données relativement petites est également assez faible, nous utilisons donc la communication en cluster dans le réseau.

Normalement, si vous faites du parallélisme de données en apprentissage profond, chaque GPU exécutera le même réseau, mais traitera différentes parties du même ensemble de données, et ils accumuleront chacun des gradients de poids, que vous partagerez ensuite. Dégradé sur chaque GPU et accumulez tous les dégradés, puis ajoutez-les aux poids. La communication de cluster est très efficace pour gérer ce type de travail.

Dejan Milojicic : Faut-il créer un accélérateur universel de deep learning pour toutes les applications, ou créer des accélérateurs spécialisés, comme des accélérateurs de vision ou des accélérateurs de traitement du langage naturel ?

Bill Dally : Sans affecter l'efficacité, je pense que plus l'accélérateur est général, mieux le GPU de Nvidia est comparable à un accélérateur dédié en termes d'accélération de l'efficacité du deep learning. Ce qui est vraiment important, c'est que le domaine de l'apprentissage automatique progresse à un rythme incroyable.

Il y a quelques années, tout le monde utilisait encore des réseaux de neurones récurrents pour traiter le langage, puis Transformer est apparu et a remplacé RNN à une vitesse fulgurante. En un clin d'œil, tout le monde a commencé à utiliser Transformer pour le traitement du langage naturel. De même, il y a quelques années à peine, tout le monde utilisait les CNN pour traiter les images. Même si de nombreuses personnes utilisent encore des réseaux neuronaux convolutifs, de plus en plus de personnes commencent à utiliser des Transformers pour traiter des images. Par conséquent, je ne suis pas favorable à une spécialisation excessive du produit ou à la création d'un accélérateur dédié à un certain réseau, car le cycle de conception du produit prend généralement plusieurs années, et pendant ce temps, les gens sont susceptibles de ne plus utiliser le réseau. Nous devons être vigilants pour détecter à temps les changements dans ce secteur, car celui-ci se développe à un rythme alarmant.

Dejan Milojicic : Quel impact la loi de Moore a-t-elle sur les performances du GPU et l'utilisation de la mémoire ?

Bill Dally : La loi de Moore stipule que le coût des transistors diminuera d'année en année. Aujourd'hui, le nombre de transistors pouvant être logés sur des circuits intégrés augmente en effet, et le processus de fabrication des puces a également fait un bond de 16 nanomètres à 7 nanomètres. La densité des transistors sur les circuits intégrés est de plus en plus grande, mais le prix. d'un seul transistor n'a pas diminué. Je pense donc que la loi de Moore est un peu dépassée.

Pourtant, c’est bien d’avoir plus de transistors sur un circuit intégré pour pouvoir construire des GPU plus gros. Les gros GPU consomment également plus d'énergie et sont plus chers, mais c'est toujours une bonne chose car nous pouvons construire des choses que nous ne pouvions pas construire auparavant.

Dejan Milojicic : Si les développeurs accordent plus d'attention aux frameworks comme PyTorch, que devraient-ils apprendre des progrès du matériel pour que leurs modèles d'apprentissage profond fonctionnent plus efficacement ?

Bill Dally : Il est difficile de répondre à cette question. Le framework fait un bon travail d'abstraction du matériel, mais il existe encore certains facteurs qui affectent la vitesse d'exécution de votre modèle et qui méritent d'être étudiés. Ce que nous pouvons essayer de faire, c'est que lorsque nous proposons une meilleure technique, comme une meilleure représentation numérique, nous pouvons essayer de combiner différentes techniques avec le cadre et voir laquelle est la plus efficace, ce qui est une partie indispensable du travail de R&D.

Dejan Milojicic : Nvidia expérimente-t-il de nouvelles méthodes de packaging ?

Bill Dally : Nous avons mené diverses expériences avec diverses technologies d'emballage pour déterminer ce qu'elles peuvent et ne peuvent pas faire afin que nous puissions les déployer dans des produits au bon moment. Par exemple, certains de ces projets étudient des modules multipuces, utilisant des plots de soudure et des liaisons hybrides pour l'empilement de puces. En fait, il existe de nombreuses technologies de conditionnement simples.

Dejan Milojicic : Comparé au Tensor Core de Nvidia et au TPU de Google, qui est le meilleur ? Bill Dally : Nous ne savons pas grand-chose du dernier TPU de Google, mais les TPU qu'ils ont lancés auparavant étaient tous des moteurs dédiés, essentiellement intégrés à de grands réseaux multiplicateurs-accumulateurs.

Unités indépendantes du TPU pour gérer des choses telles que les fonctions non linéaires et la norme par lots, mais notre approche consiste à construire une unité de calcul multiprocesseur (SM) de streaming très générale qui peut simplement lui faire faire n'importe quoi avec des instructions très générales, puis utiliser des cœurs Tensor pour accélérer la partie multiplication matricielle. Ainsi, Tensor Core et le TPU de Google ont des tableaux multiplicateurs-accumulateurs similaires, c'est juste que le tableau que nous utilisons est relativement plus petit.

Dejan Milojicic : Qui est le plus grand rival de Nvidia ? Bill Dally : NVIDIA ne se compare jamais aux autres sociétés. Notre plus grand adversaire est nous-mêmes, et nous nous remettons constamment en question. Je pense que c'est la bonne attitude. Si nous considérons aveuglément les autres comme des concurrents, cela ralentira notre progression. Au lieu de nous concentrer autant sur ce que font les autres, nous devrions vraiment nous concentrer sur ce qui est possible. Ce que nous faisons, c'est comme poursuivre la vitesse de la lumière. Nous accordons plus d'attention à la manière de faire de notre mieux et à la distance qui nous sépare de la vitesse de la lumière. C'est le véritable défi.

Dejan Milojicic : Que pensez-vous de l'informatique quantique ? Les simulations quantiques sont-elles une extension naturelle des défis du deep learning ?

Bill Dally : En mars 2021, nous avons publié un kit de développement logiciel appelé « cuQuantum ». Google a également déjà développé un ordinateur doté de 53 qubits et affirmé avoir atteint une « supériorité quantique ». Certains calculs qui ne peuvent pas être effectués par des ordinateurs traditionnels peuvent être effectués en cinq minutes à l'aide de cuQuantum. Par conséquent, si vous souhaitez obtenir des algorithmes quantiques vraiment précis, plutôt que les calculs NIST (Noisy Intermediate-Scale Quantum) actuels, le GPU devrait être le meilleur choix.

L'ordinateur GPU traditionnel de NVIDIA est actuellement l'un des ordinateurs quantiques les plus rapides, et Alibaba a également obtenu de bons résultats dans des calculs classiques similaires, ce qui ne fait que confirmer notre conclusion. Notre point de vue sur l'informatique quantique : Nvidia ne sera surpris par aucune évolution dans ce domaine technologique.

En fait, nous avons également mis en place un groupe de recherche pour suivre les développements de pointe dans le domaine de l'informatique quantique. Par exemple, IBM a annoncé le développement d'une puce à 127 qubits. Nous avons également suivi les progrès sur des aspects tels que le nombre de qubits et le temps de cohérence.

Compte tenu du nombre de qubits requis, de la précision des qubits, de l'interférence du bruit sur le quantum et des frais généraux requis pour la correction des erreurs quantiques, je ne pense pas que l'informatique quantique sera disponible dans le commerce dans les cinq prochaines années. dix ans. Mon point de vue le plus optimiste est que dans environ cinq ans, les gens commenceront à faire des simulations de chimie quantique, ce qui devrait être la chose la plus probable. Mais avant que cela n’arrive, il reste encore de nombreuses énigmes physiques à résoudre. Ce que beaucoup de gens ne réalisent pas, c’est que les ordinateurs quantiques sont des ordinateurs analogiques, et que les ordinateurs analogiques doivent être très précis et faciles à isoler, sinon tout couplage avec l’environnement conduira à des résultats incohérents.

Dejan Milojicic : Selon vous, quand les machines atteindront-elles le niveau de l'intelligence générale artificielle (AGI) ?

Bill Dally : J'ai un avis négatif sur cette question. Jetez un œil à certains des cas d’utilisation de l’intelligence artificielle les plus réussis, tels que les réseaux de neurones, qui sont essentiellement des ajusteurs de fonctions universels. Les réseaux de neurones peuvent apprendre une fonction grâce à l’observation, de sorte que leur valeur se reflète toujours dans la perception artificielle plutôt que dans l’intelligence artificielle.

Bien que nous ayons obtenu de bons résultats jusqu'à présent, nous pouvons continuer à étudier comment utiliser l'intelligence artificielle et l'apprentissage profond pour améliorer la productivité, améliorant ainsi les soins médicaux et l'éducation et offrant aux gens une vie meilleure. En fait, nous n'avons pas besoin d'AGI pour ce faire, mais nous devrions nous concentrer sur la façon de maximiser l'utilisation de la technologie existante. Il y a encore un long chemin à parcourir avant l’AGI, et nous devons aussi comprendre ce qu’est l’AGI.

Par conséquent, je ne suis pas favorable à une spécialisation excessive du produit ou à la création d'un accélérateur dédié à un certain réseau, car le cycle de conception du produit prend généralement plusieurs années, et pendant ce temps, les gens sont susceptibles de ne plus utiliser le réseau. Nous devons être vigilants pour détecter à temps les changements dans ce secteur, car celui-ci se développe à un rythme alarmant.

Dejan Milojicic : Quel impact la loi de Moore a-t-elle sur les performances du GPU et l'utilisation de la mémoire ?

Bill Dally : La loi de Moore stipule que le coût des transistors diminuera d'année en année. Aujourd'hui, le nombre de transistors pouvant être logés sur des circuits intégrés augmente en effet, et le processus de fabrication des puces a également fait un bond de 16 nanomètres à 7 nanomètres. La densité des transistors sur les circuits intégrés est de plus en plus grande, mais le prix. d'un seul transistor n'a pas diminué. Je pense donc que la loi de Moore est un peu dépassée.

Pourtant, c’est bien d’avoir plus de transistors sur un circuit intégré pour pouvoir construire des GPU plus gros. Les gros GPU consomment également plus d'énergie et sont plus chers, mais c'est toujours une bonne chose car nous pouvons construire des choses que nous ne pouvions pas construire auparavant.

Dejan Milojicic : Si les développeurs accordent plus d'attention aux frameworks comme PyTorch, que devraient-ils apprendre des progrès du matériel pour que leurs modèles d'apprentissage profond fonctionnent plus efficacement ?

Bill Dally : Il est difficile de répondre à cette question. Le framework fait un bon travail d'abstraction du matériel, mais il existe encore certains facteurs qui affectent la vitesse d'exécution de votre modèle et qui méritent d'être étudiés. Ce que nous pouvons essayer de faire, c'est que lorsque nous proposons une meilleure technique, comme une meilleure représentation numérique, nous pouvons essayer de combiner différentes techniques avec le cadre et voir laquelle est la plus efficace, ce qui est une partie indispensable du travail de R&D.

Dejan Milojicic : Nvidia expérimente-t-il de nouvelles méthodes de packaging ?

Bill Dally : Nous avons mené diverses expériences avec diverses technologies d'emballage pour déterminer ce qu'elles peuvent et ne peuvent pas faire afin que nous puissions les déployer dans des produits au bon moment. Par exemple, certains de ces projets étudient des modules multipuces, utilisant des plots de soudure et des liaisons hybrides pour l'empilement de puces. En fait, il existe de nombreuses technologies de conditionnement simples.

Dejan Milojicic : Comparé au Tensor Core de Nvidia et au TPU de Google, qui est le meilleur ? Bill Dally : Nous ne savons pas grand-chose du dernier TPU de Google, mais les TPU qu'ils ont lancés auparavant étaient tous des moteurs dédiés, essentiellement intégrés à de grands réseaux multiplicateurs-accumulateurs.

Unités indépendantes du TPU pour gérer des choses telles que les fonctions non linéaires et la norme par lots, mais notre approche consiste à construire une unité de calcul multiprocesseur (SM) de streaming très générale qui peut simplement lui faire faire n'importe quoi avec des instructions très générales, puis utiliser des cœurs Tensor pour accélérer la partie multiplication matricielle. Ainsi, Tensor Core et le TPU de Google ont des tableaux multiplicateurs-accumulateurs similaires, c'est juste que le tableau que nous utilisons est relativement plus petit.

Dejan Milojicic : Qui est le plus grand rival de Nvidia ? Bill Dally : NVIDIA ne se compare jamais aux autres sociétés. Notre plus grand adversaire est nous-mêmes, et nous nous remettons constamment en question. Je pense que c'est la bonne attitude. Si nous considérons aveuglément les autres comme des concurrents, cela ralentira notre progression. Au lieu de nous concentrer autant sur ce que font les autres, nous devrions vraiment nous concentrer sur ce qui est possible. Ce que nous faisons, c'est comme poursuivre la vitesse de la lumière. Nous accordons plus d'attention à la manière de faire de notre mieux et à la distance qui nous sépare de la vitesse de la lumière. C'est le véritable défi.

Dejan Milojicic : Que pensez-vous de l'informatique quantique ? Les simulations quantiques sont-elles une extension naturelle des défis du deep learning ?

Bill Dally : En mars 2021, nous avons publié un kit de développement logiciel appelé « cuQuantum ». Google a également déjà développé un ordinateur doté de 53 qubits et affirmé avoir atteint une « supériorité quantique ». Certains calculs qui ne peuvent pas être effectués par des ordinateurs traditionnels peuvent être effectués en cinq minutes à l'aide de cuQuantum. Par conséquent, si vous souhaitez obtenir des algorithmes quantiques vraiment précis, plutôt que les calculs NIST (Noisy Intermediate-Scale Quantum) actuels, le GPU devrait être le meilleur choix.

L'ordinateur GPU traditionnel de NVIDIA est actuellement l'un des ordinateurs quantiques les plus rapides, et Alibaba a également obtenu de bons résultats dans des calculs classiques similaires, ce qui ne fait que confirmer notre conclusion. Notre point de vue sur l'informatique quantique : Nvidia ne sera surpris par aucune évolution dans ce domaine technologique.

En fait, nous avons également mis en place un groupe de recherche pour suivre les développements de pointe dans le domaine de l'informatique quantique. Par exemple, IBM a annoncé le développement d'une puce à 127 qubits. Nous avons également suivi les progrès sur des aspects tels que le nombre de qubits et le temps de cohérence.

Compte tenu du nombre de qubits requis, de la précision des qubits, de l'interférence du bruit sur le quantum et des frais généraux requis pour la correction des erreurs quantiques, je ne pense pas que l'informatique quantique sera disponible dans le commerce dans les cinq prochaines années. dix ans. Mon point de vue le plus optimiste est que dans environ cinq ans, les gens commenceront à faire des simulations de chimie quantique, ce qui devrait être la chose la plus probable. Mais avant que cela n’arrive, il reste encore de nombreuses énigmes physiques à résoudre. Ce que beaucoup de gens ne réalisent pas, c’est que les ordinateurs quantiques sont des ordinateurs analogiques, et que les ordinateurs analogiques doivent être très précis et faciles à isoler, sinon tout couplage avec l’environnement conduira à des résultats incohérents.

Dejan Milojicic : Selon vous, quand les machines atteindront-elles le niveau de l'intelligence générale artificielle (AGI) ?

Bill Dally : J'ai un avis négatif sur cette question. Jetez un œil à certains des cas d’utilisation de l’intelligence artificielle les plus réussis, tels que les réseaux de neurones, qui sont essentiellement des ajusteurs de fonctions universels. Les réseaux de neurones peuvent apprendre une fonction grâce à l’observation, de sorte que leur valeur se reflète toujours dans la perception artificielle plutôt que dans l’intelligence artificielle.

Bien que nous ayons obtenu de bons résultats jusqu'à présent, nous pouvons continuer à étudier comment utiliser l'intelligence artificielle et l'apprentissage profond pour améliorer la productivité, améliorant ainsi les soins médicaux et l'éducation et offrant aux gens une vie meilleure. En fait, nous n'avons pas besoin d'AGI pour ce faire, mais nous devrions nous concentrer sur la façon de maximiser l'utilisation de la technologie existante. Il y a encore un long chemin à parcourir avant l’AGI, et nous devons aussi comprendre ce qu’est l’AGI.

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!

Outils d'IA chauds

Undresser.AI Undress

Application basée sur l'IA pour créer des photos de nu réalistes

AI Clothes Remover

Outil d'IA en ligne pour supprimer les vêtements des photos.

Undress AI Tool

Images de déshabillage gratuites

Clothoff.io

Dissolvant de vêtements AI

AI Hentai Generator

Générez AI Hentai gratuitement.

Article chaud

Outils chauds

Bloc-notes++7.3.1

Éditeur de code facile à utiliser et gratuit

SublimeText3 version chinoise

Version chinoise, très simple à utiliser

Envoyer Studio 13.0.1

Puissant environnement de développement intégré PHP

Dreamweaver CS6

Outils de développement Web visuel

SublimeText3 version Mac

Logiciel d'édition de code au niveau de Dieu (SublimeText3)

Bytedance Cutting lance le super abonnement SVIP : 499 yuans pour un abonnement annuel continu, offrant une variété de fonctions d'IA

Jun 28, 2024 am 03:51 AM

Bytedance Cutting lance le super abonnement SVIP : 499 yuans pour un abonnement annuel continu, offrant une variété de fonctions d'IA

Jun 28, 2024 am 03:51 AM

Ce site a rapporté le 27 juin que Jianying est un logiciel de montage vidéo développé par FaceMeng Technology, une filiale de ByteDance. Il s'appuie sur la plateforme Douyin et produit essentiellement du contenu vidéo court pour les utilisateurs de la plateforme. Il est compatible avec iOS, Android et. Windows, MacOS et autres systèmes d'exploitation. Jianying a officiellement annoncé la mise à niveau de son système d'adhésion et a lancé un nouveau SVIP, qui comprend une variété de technologies noires d'IA, telles que la traduction intelligente, la mise en évidence intelligente, l'emballage intelligent, la synthèse humaine numérique, etc. En termes de prix, les frais mensuels pour le clipping SVIP sont de 79 yuans, les frais annuels sont de 599 yuans (attention sur ce site : équivalent à 49,9 yuans par mois), l'abonnement mensuel continu est de 59 yuans par mois et l'abonnement annuel continu est de 59 yuans par mois. est de 499 yuans par an (équivalent à 41,6 yuans par mois) . En outre, le responsable de Cut a également déclaré que afin d'améliorer l'expérience utilisateur, ceux qui se sont abonnés au VIP d'origine

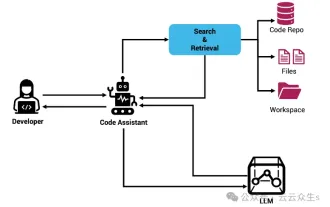

Assistant de codage d'IA augmenté par le contexte utilisant Rag et Sem-Rag

Jun 10, 2024 am 11:08 AM

Assistant de codage d'IA augmenté par le contexte utilisant Rag et Sem-Rag

Jun 10, 2024 am 11:08 AM

Améliorez la productivité, l’efficacité et la précision des développeurs en intégrant une génération et une mémoire sémantique améliorées par la récupération dans les assistants de codage IA. Traduit de EnhancingAICodingAssistantswithContextUsingRAGandSEM-RAG, auteur JanakiramMSV. Bien que les assistants de programmation d'IA de base soient naturellement utiles, ils ne parviennent souvent pas à fournir les suggestions de code les plus pertinentes et les plus correctes, car ils s'appuient sur une compréhension générale du langage logiciel et des modèles d'écriture de logiciels les plus courants. Le code généré par ces assistants de codage est adapté à la résolution des problèmes qu’ils sont chargés de résoudre, mais n’est souvent pas conforme aux normes, conventions et styles de codage des équipes individuelles. Cela aboutit souvent à des suggestions qui doivent être modifiées ou affinées pour que le code soit accepté dans l'application.

Sept questions d'entretien technique Cool GenAI et LLM

Jun 07, 2024 am 10:06 AM

Sept questions d'entretien technique Cool GenAI et LLM

Jun 07, 2024 am 10:06 AM

Pour en savoir plus sur l'AIGC, veuillez visiter : 51CTOAI.x Community https://www.51cto.com/aigc/Translator|Jingyan Reviewer|Chonglou est différent de la banque de questions traditionnelle que l'on peut voir partout sur Internet. nécessite de sortir des sentiers battus. Les grands modèles linguistiques (LLM) sont de plus en plus importants dans les domaines de la science des données, de l'intelligence artificielle générative (GenAI) et de l'intelligence artificielle. Ces algorithmes complexes améliorent les compétences humaines et stimulent l’efficacité et l’innovation dans de nombreux secteurs, devenant ainsi la clé permettant aux entreprises de rester compétitives. LLM a un large éventail d'applications. Il peut être utilisé dans des domaines tels que le traitement du langage naturel, la génération de texte, la reconnaissance vocale et les systèmes de recommandation. En apprenant de grandes quantités de données, LLM est capable de générer du texte

Le réglage fin peut-il vraiment permettre au LLM d'apprendre de nouvelles choses : l'introduction de nouvelles connaissances peut amener le modèle à produire davantage d'hallucinations

Jun 11, 2024 pm 03:57 PM

Le réglage fin peut-il vraiment permettre au LLM d'apprendre de nouvelles choses : l'introduction de nouvelles connaissances peut amener le modèle à produire davantage d'hallucinations

Jun 11, 2024 pm 03:57 PM

Les grands modèles linguistiques (LLM) sont formés sur d'énormes bases de données textuelles, où ils acquièrent de grandes quantités de connaissances du monde réel. Ces connaissances sont intégrées à leurs paramètres et peuvent ensuite être utilisées en cas de besoin. La connaissance de ces modèles est « réifiée » en fin de formation. À la fin de la pré-formation, le modèle arrête effectivement d’apprendre. Alignez ou affinez le modèle pour apprendre à exploiter ces connaissances et répondre plus naturellement aux questions des utilisateurs. Mais parfois, la connaissance du modèle ne suffit pas, et bien que le modèle puisse accéder à du contenu externe via RAG, il est considéré comme bénéfique de l'adapter à de nouveaux domaines grâce à un réglage fin. Ce réglage fin est effectué à l'aide de la contribution d'annotateurs humains ou d'autres créations LLM, où le modèle rencontre des connaissances supplémentaires du monde réel et les intègre.

Afin de fournir un nouveau système de référence et d'évaluation de questions-réponses scientifiques et complexes pour les grands modèles, l'UNSW, Argonne, l'Université de Chicago et d'autres institutions ont lancé conjointement le cadre SciQAG.

Jul 25, 2024 am 06:42 AM

Afin de fournir un nouveau système de référence et d'évaluation de questions-réponses scientifiques et complexes pour les grands modèles, l'UNSW, Argonne, l'Université de Chicago et d'autres institutions ont lancé conjointement le cadre SciQAG.

Jul 25, 2024 am 06:42 AM

L'ensemble de données ScienceAI Question Answering (QA) joue un rôle essentiel dans la promotion de la recherche sur le traitement du langage naturel (NLP). Des ensembles de données d'assurance qualité de haute qualité peuvent non seulement être utilisés pour affiner les modèles, mais également évaluer efficacement les capacités des grands modèles linguistiques (LLM), en particulier la capacité à comprendre et à raisonner sur les connaissances scientifiques. Bien qu’il existe actuellement de nombreux ensembles de données scientifiques d’assurance qualité couvrant la médecine, la chimie, la biologie et d’autres domaines, ces ensembles de données présentent encore certaines lacunes. Premièrement, le formulaire de données est relativement simple, et la plupart sont des questions à choix multiples. Elles sont faciles à évaluer, mais limitent la plage de sélection des réponses du modèle et ne peuvent pas tester pleinement la capacité du modèle à répondre aux questions scientifiques. En revanche, les questions et réponses ouvertes

Cinq écoles d'apprentissage automatique que vous ne connaissez pas

Jun 05, 2024 pm 08:51 PM

Cinq écoles d'apprentissage automatique que vous ne connaissez pas

Jun 05, 2024 pm 08:51 PM

L'apprentissage automatique est une branche importante de l'intelligence artificielle qui donne aux ordinateurs la possibilité d'apprendre à partir de données et d'améliorer leurs capacités sans être explicitement programmés. L'apprentissage automatique a un large éventail d'applications dans divers domaines, de la reconnaissance d'images et du traitement du langage naturel aux systèmes de recommandation et à la détection des fraudes, et il change notre façon de vivre. Il existe de nombreuses méthodes et théories différentes dans le domaine de l'apprentissage automatique, parmi lesquelles les cinq méthodes les plus influentes sont appelées les « Cinq écoles d'apprentissage automatique ». Les cinq grandes écoles sont l’école symbolique, l’école connexionniste, l’école évolutionniste, l’école bayésienne et l’école analogique. 1. Le symbolisme, également connu sous le nom de symbolisme, met l'accent sur l'utilisation de symboles pour le raisonnement logique et l'expression des connaissances. Cette école de pensée estime que l'apprentissage est un processus de déduction inversée, à travers les connaissances existantes.

Les performances de SOTA, la méthode d'IA de prédiction d'affinité protéine-ligand multimodale de Xiamen, combinent pour la première fois des informations sur la surface moléculaire

Jul 17, 2024 pm 06:37 PM

Les performances de SOTA, la méthode d'IA de prédiction d'affinité protéine-ligand multimodale de Xiamen, combinent pour la première fois des informations sur la surface moléculaire

Jul 17, 2024 pm 06:37 PM

Editeur | KX Dans le domaine de la recherche et du développement de médicaments, il est crucial de prédire avec précision et efficacité l'affinité de liaison des protéines et des ligands pour le criblage et l'optimisation des médicaments. Cependant, les études actuelles ne prennent pas en compte le rôle important des informations sur la surface moléculaire dans les interactions protéine-ligand. Sur cette base, des chercheurs de l'Université de Xiamen ont proposé un nouveau cadre d'extraction de caractéristiques multimodales (MFE), qui combine pour la première fois des informations sur la surface des protéines, la structure et la séquence 3D, et utilise un mécanisme d'attention croisée pour comparer différentes modalités. alignement. Les résultats expérimentaux démontrent que cette méthode atteint des performances de pointe dans la prédiction des affinités de liaison protéine-ligand. De plus, les études d’ablation démontrent l’efficacité et la nécessité des informations sur la surface des protéines et de l’alignement des caractéristiques multimodales dans ce cadre. Les recherches connexes commencent par "S

AlphaFold 3 est lancé, prédisant de manière exhaustive les interactions et les structures des protéines et de toutes les molécules de la vie, avec une précision bien plus grande que jamais

Jul 16, 2024 am 12:08 AM

AlphaFold 3 est lancé, prédisant de manière exhaustive les interactions et les structures des protéines et de toutes les molécules de la vie, avec une précision bien plus grande que jamais

Jul 16, 2024 am 12:08 AM

Editeur | Radis Skin Depuis la sortie du puissant AlphaFold2 en 2021, les scientifiques utilisent des modèles de prédiction de la structure des protéines pour cartographier diverses structures protéiques dans les cellules, découvrir des médicaments et dresser une « carte cosmique » de chaque interaction protéique connue. Tout à l'heure, Google DeepMind a publié le modèle AlphaFold3, capable d'effectuer des prédictions de structure conjointe pour des complexes comprenant des protéines, des acides nucléiques, de petites molécules, des ions et des résidus modifiés. La précision d’AlphaFold3 a été considérablement améliorée par rapport à de nombreux outils dédiés dans le passé (interaction protéine-ligand, interaction protéine-acide nucléique, prédiction anticorps-antigène). Cela montre qu’au sein d’un cadre unique et unifié d’apprentissage profond, il est possible de réaliser