Périphériques technologiques

Périphériques technologiques

IA

IA

Voici la bouée de sauvetage des transistors : CMOS empilé 3D, la loi de Moore va-t-elle perdurer encore 10 ans ?

Voici la bouée de sauvetage des transistors : CMOS empilé 3D, la loi de Moore va-t-elle perdurer encore 10 ans ?

Voici la bouée de sauvetage des transistors : CMOS empilé 3D, la loi de Moore va-t-elle perdurer encore 10 ans ?

Le transistor est connu comme « la plus grande invention du 20ème siècle ».

Son émergence a jeté les bases de la production de circuits intégrés, de microprocesseurs et de mémoire informatique.

En 1965, la « loi de Moore » a été proposée et est devenue la règle d'or de l'industrie des semi-conducteurs pendant des décennies.

Cela montre que tous les 18 à 24 mois, le nombre de transistors emballés sur une puce doublera, et les performances de la puce doubleront également.

Cependant, avec l'introduction continue de nouveaux nœuds de processus, le nombre d'atomes dans les transistors est devenu de moins en moins et diverses limites physiques limitent le développement ultérieur de la loi de Moore.

Certaines personnes pensent même que la loi de Moore est révolue.

Par conséquent, afin de « sauver » la loi de Moore, les ingénieurs doivent modifier la structure du transistor, continuer à réduire la surface et la consommation d'énergie et améliorer ses performances.

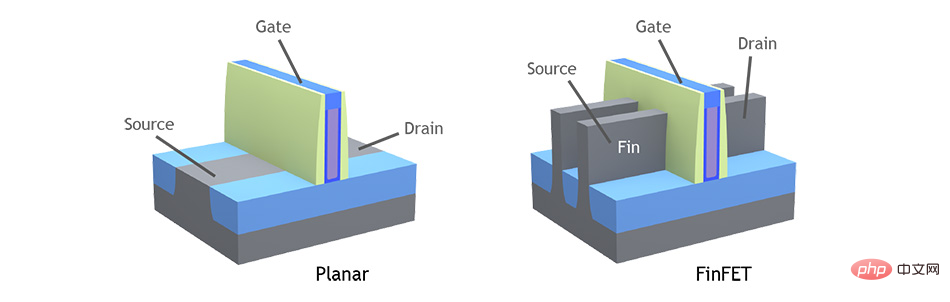

Dans la seconde moitié du 20e siècle, la conception de transistors planaires (Planar Transistor) était principalement populaire. À partir des années 2010, les appareils 3D en forme d’aileron ont progressivement remplacé les modèles plats.

Maintenant, une toute nouvelle structure de conception de transistor, le Gate All Around Transistor (GAA), est le successeur du FinFET et est sur le point d'entrer en production.

Mais, il faut regarder plus loin. Car même avec cette nouvelle architecture de transistor RibbonFET proposée par Intel, notre capacité à réduire la taille a des limites.

Croyez que les semi-conducteurs à oxyde métallique complémentaire (CMOS) ou CFET (transistors à effet de champ complémentaires) empilés en 3D seront la clé pour étendre la loi de Moore au cours de la prochaine décennie.

L'évolution des transistors

Chaque transistor à effet de champ à semi-conducteur à oxyde métallique (MOSFET) possède le même ensemble de composants de base :

pile de grille, région de canal (région de canal), source, drain

La source et le drain sont dopés chimiquement de sorte qu'ils soient soit riches en électrons mobiles (type n), soit dépourvus d'électrons (type p). La région du canal a le dopage opposé à celui de la source et du drain.

Dans la version planaire du transistor dans les microprocesseurs avancés avant 2011, la pile de grille du MOSFET se trouvait juste au-dessus de la zone du canal et était utilisée pour projeter le champ électrique dans la zone du canal.

L'application d'une tension suffisamment importante à la grille (par rapport à la source) formera une couche de porteurs de charge mobiles dans la zone du canal, permettant au courant de circuler entre la source et le drain.

Afin de réduire la taille des conceptions de transistors planaires, un "effet canal court" est devenu le centre d'intérêt des physiciens.

Étant donné que la technologie des processus continue de s'améliorer, la largeur de l'électrode de grille dans le transistor est de plus en plus réduite. Vous savez, lorsque la porte est inférieure à 20 nm, le courant sera hors de contrôle et le courant source pénétrera dans la porte et atteindra directement le drain.

À ce moment-là, une « fuite » se produira, ce qui entraînera une forte augmentation de la consommation d'énergie de la puce.

Afin de résoudre ce problème, une nouvelle technologie de transistor FinFET est proposée. Il enroule le portail autour d'un canal sur trois côtés pour offrir un meilleur contrôle statique.

FinFET réduit la consommation d'énergie d'environ 50 % au même niveau de performances que l'architecture planaire de la génération précédente. Les FinFET commutent également plus rapidement, offrant une amélioration des performances de 37 %.

En 2011, Intel a introduit FinFET sur le nœud 22 nm qu'il a lancé et l'a utilisé dans la production de ses processeurs Core de troisième génération.

Depuis lors, FinFET est devenu le cheval de bataille de la loi de Moore.

Cependant, nous avons également perdu quelque chose lorsque nous sommes passés à FinFET.

Dans les dispositifs planaires, la largeur du transistor est définie par photolithographie, c'est donc un paramètre très flexible.

Mais dans FinFET, la largeur du transistor se présente par incréments discrets, en ajoutant une ailette à la fois. Cette propriété est souvent appelée quantification des ailerons.

Malgré la flexibilité des FinFET, la quantification des ailettes reste une contrainte de conception importante. Les règles de conception qui l'entourent et le désir d'ajouter plus d'ailettes pour améliorer les performances, augmentent la surface globale de la cellule logique et compliquent la pile d'interconnexion qui transforme un seul transistor en un circuit logique complet.

Il augmente également la capacité du transistor, réduisant ainsi sa vitesse de commutation. Ainsi, même si FinFET nous a bien servi en tant que bête de somme de l’industrie, une nouvelle approche plus raffinée est nécessaire.

C'est cette approche qui a conduit les physiciens à inventer le prochain transistor 3D - RibbonFET.

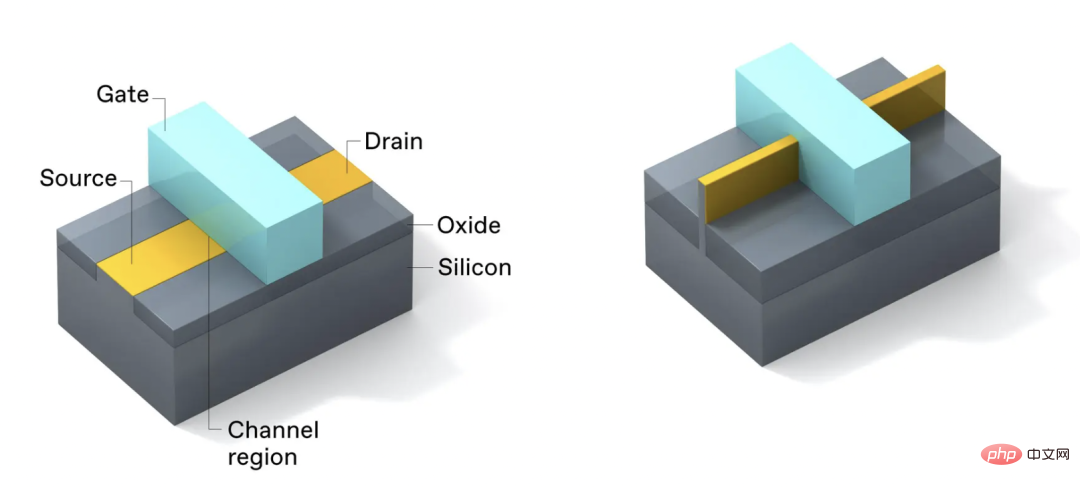

Dans RibbonFET, la grille entoure la zone du canal du transistor pour améliorer le contrôle des porteurs de charge. La nouvelle structure permet également de meilleures performances et une optimisation plus raffinée.

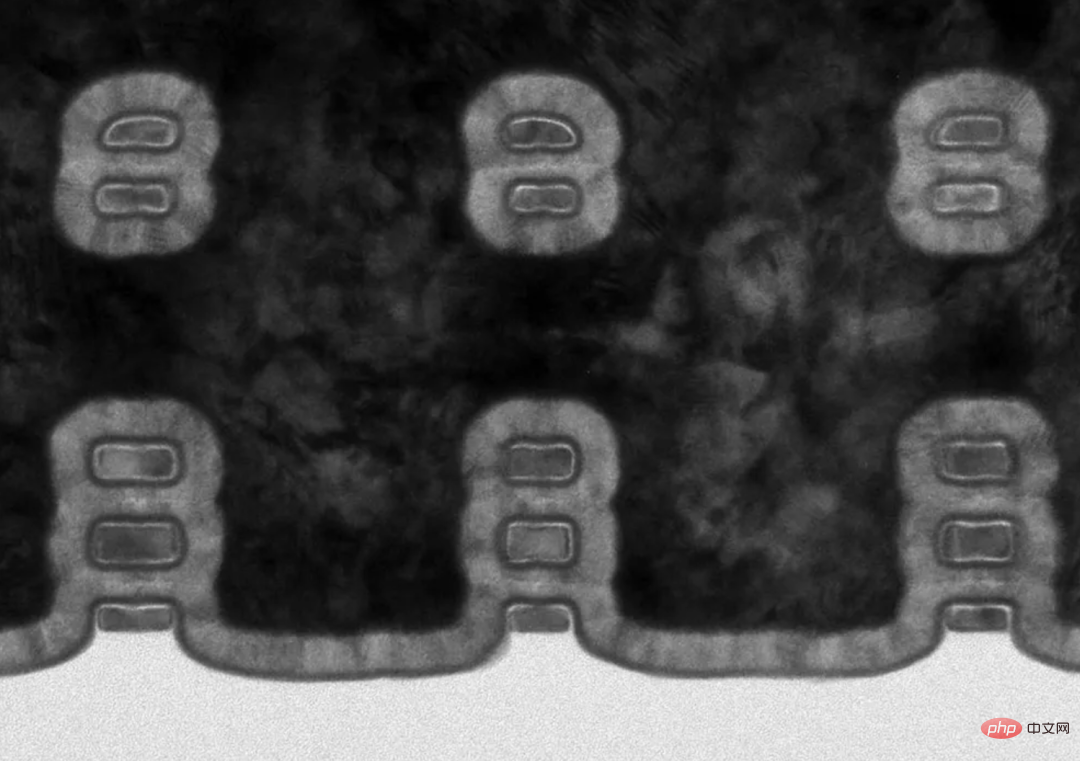

Plus précisément, la grille entoure complètement les canaux, permettant un contrôle plus strict des porteurs de charge dans les canaux, qui sont désormais formés de rubans de silicium à l'échelle nanométrique.

Grâce à ces nanorubans (nanosheets), il est possible de modifier la largeur du transistor à volonté en utilisant à nouveau la photolithographie.

Après avoir supprimé les contraintes de quantification, il est possible de générer une largeur de taille appropriée pour l'application. Cela nous permet d’équilibrer puissance, performances et coût.

Plus important encore, en s'empilant et en fonctionnant en parallèle, les appareils peuvent générer plus de courant et améliorer les performances sans augmenter la surface.

Par conséquent, Intel estime que RibbonFET est le meilleur choix pour obtenir des performances plus élevées à une puissance raisonnable.

Ils introduiront la structure RibbonFET sur le processus Intel 20A en 2024.

CMOS empilé 3D

Une chose que les transistors planaires, FinFET et RibbonFET ont en commun est qu'ils utilisent tous la technologie CMOS Comme mentionné précédemment, le CMOS est composé de transistors de type n et de type p. . Cette technologie est devenue courante dans les années 1980 car elle consomme beaucoup moins de courant que les autres alternatives. Moins de courant signifie des fréquences de fonctionnement plus élevées et une densité de transistors plus élevée.

À ce jour, toutes les technologies CMOS ont placé côte à côte des paires standards de transistors NMOS et PMOS. Cependant, dans le discours d'ouverture de la Conférence internationale sur les composants électroniques (IEDM) de l'IEEE 2019, un concept de transistors « empilés en 3D » a été proposé, plaçant des transistors NMOS au-dessus des transistors PMOS.

Lors de l'IEDM 2020, le premier onduleur conçu à partir de circuits logiques utilisant cette technologie 3D a été présenté. Le CMOS empilé 3D réduit efficacement de moitié l'encombrement de l'onduleur, doublant la densité de la surface du transistor et repoussant encore les limites de la loi de Moore.

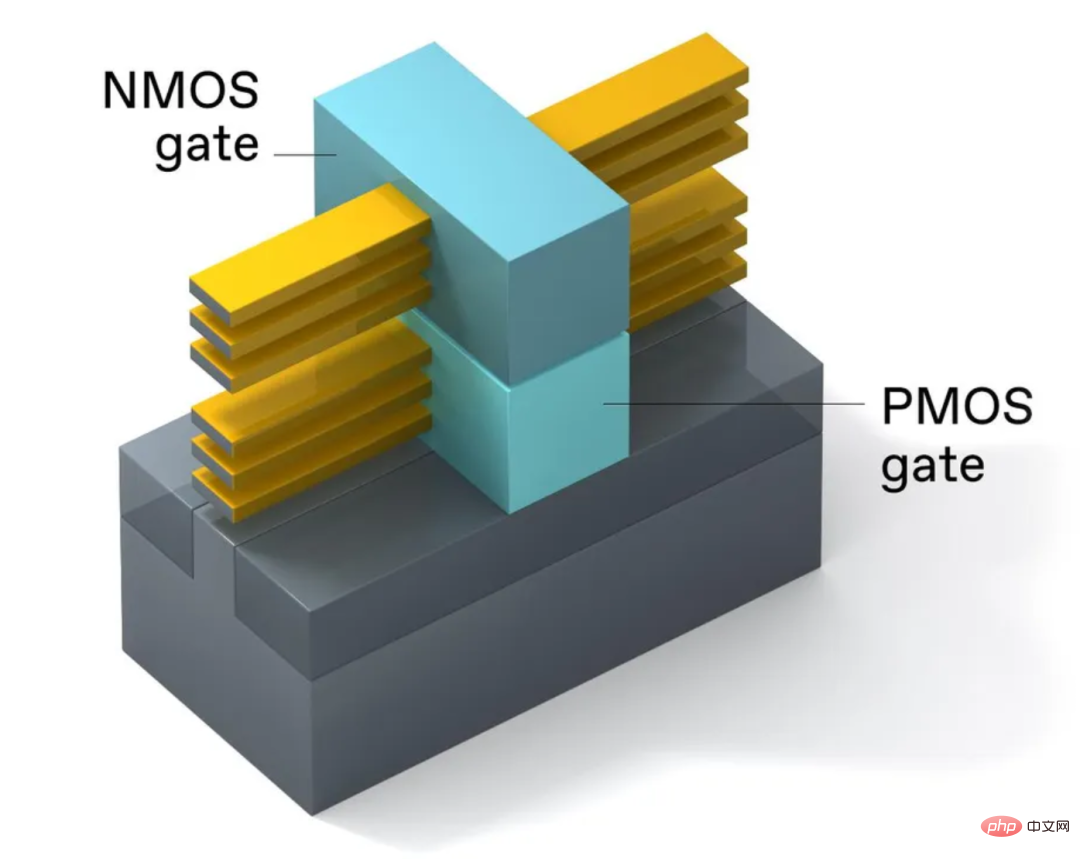

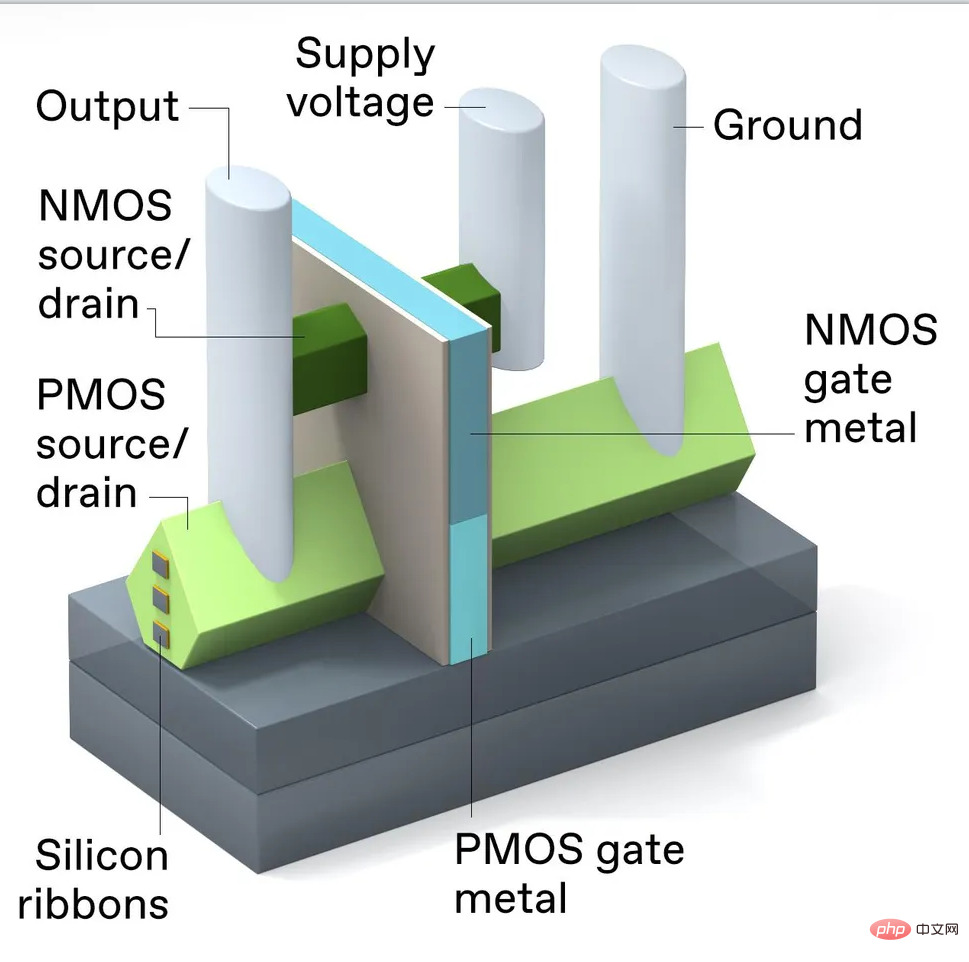

Structure CMOS empilée 3D, plaçant le périphérique PMOS au-dessus du périphérique NMOS, avec une zone totale identique à une zone RibbonFET. Les portes NMOS et PMOS utilisent différents matériaux métalliques

Pour utiliser le CMOS empilé en 3D, il existe de nombreux défis d'intégration de processus à résoudre, dont certains impliquent les limites du traitement et de la fabrication du CMOS.

Comment y parvenir ? La fabrication de CMOS 3D auto-alignés commence par des tranches de silicium. Sur la tranche, nous déposons couche après couche de silicium et de silicium germanium, une structure appelée « super-réseau ». Des motifs photolithographiques sont ensuite utilisés pour découper une partie du super-réseau, laissant une structure en forme d'aileron. Les cristaux de super-réseau fournissent une structure de support solide pour les processus de développement ultérieurs.

Ensuite, un "faux" polysilicium est placé sur le super-réseau pour protéger le premier de la prochaine opération. Cette étape, connue sous le nom de processus double source/drain empilé verticalement, fait croître du silicium dopé au phosphore aux deux extrémités du nanoruban supérieur (futur site NMOS) tout en faisant croître sélectivement du silicium dopé sur le nanoruban inférieur (futur site PMOS silicium-germanium). Ensuite, un diélectrique est placé autour des sources d’énergie pour les isoler les unes des autres par décharge électrique.

L'empilement 3D double efficacement la densité des transistors CMOS par millimètre carré, la densité réelle dépendant de la complexité des cellules logiques impliquées.

Vient enfin la construction de la porte. Retirez d’abord la fausse porte précédemment installée pour exposer les nanorubans de silicium. Ensuite, seul le silicium-germanium est gravé, libérant un empilement de nanorubans de silicium parallèles, qui constitue la région du canal du transistor.

Ensuite, une très fine couche isolante est recouverte sur les quatre côtés du nanoruban. Cette couche isolante a une constante diélectrique élevée. Les canaux des nanorubans sont si petits qu'ils ne peuvent pas être recouverts chimiquement aussi efficacement que les transistors planaires.

Utilisez un métal pour entourer le nanoruban inférieur afin de former un canal dopé p, et le nanoruban supérieur forme un canal dopé n avec un autre nanoruban. De cette façon, la pile de grilles est construite et les deux transistors sont installés.

Ce processus peut paraître compliqué, mais il est meilleur qu'une autre technique (Sequential 3D Stacking). Si ce dernier est utilisé, le dispositif NMOS et le dispositif PMOS sont montés sur des tranches séparées, puis les deux sont réunis et la couche PMOS est transférée sur la tranche NMOS. La méthode d’empilement 3D auto-alignée comporte moins d’étapes de traitement et permet de contrôler plus strictement les coûts de fabrication.

Et plus important encore, cette méthode d'auto-alignement évite également les erreurs d'alignement pouvant survenir lors de la connexion de deux wafers. Établir toutes les connexions requises au CMOS empilé 3D est très difficile. Des connexions électriques seront requises à partir de la pile de périphériques ci-dessous. De par leur conception, le dispositif NMOS [en haut] et le dispositif PMOS [en bas] ont des contacts source/drain séparés, mais les deux appareils partagent une porte commune.

Il est à noter que l'espacement vertical entre NMOS et PMOS est à optimiser : s'il est trop court, cela augmentera la capacité parasite, s'il est trop long, cela augmentera la résistance de l'interconnexion entre les deux appareils. L’une ou l’autre situation extrême entraînera un ralentissement du circuit et consommera plus d’énergie.

De nombreuses études de conception, comme celle présentée par le centre de recherche américain TEL lors de la conférence IEDM 2021, proposent de fournir toutes les interconnexions nécessaires dans l'espace limité du CMOS 3D, sans augmenter significativement les unités logiques qu'elles constituent. La recherche montre qu'il existe de nombreuses possibilités d'innovation pour trouver les meilleures options d'interconnexion.

L'avenir de la loi de Moore

Avec les transistors à effet de champ en bande et le CMOS 3D, nous avons une voie claire pour prolonger la durée de vie de la loi de Moore, au moins jusqu'en 2024 et au-delà.

Dans une interview en 2005, Gordon Moore, le proposant de la loi de Moore, a admis que « je suis surpris de temps en temps par les progrès qui ont été réalisés ».

Il a déclaré : "Il y a eu des moments en cours de route où je pensais que nous avions atteint la fin, mais nos ingénieurs créatifs ont trouvé des moyens de surmonter les difficultés." est passé par FinFET, et avec une optimisation continue, est arrivé à l'ère RibbonFET, et a finalement évolué vers le processus CMOS empilé 3D. Nous prévoyons que la surprise laissée à M. Gordon Moore viendra bientôt.

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!

Outils d'IA chauds

Undresser.AI Undress

Application basée sur l'IA pour créer des photos de nu réalistes

AI Clothes Remover

Outil d'IA en ligne pour supprimer les vêtements des photos.

Undress AI Tool

Images de déshabillage gratuites

Clothoff.io

Dissolvant de vêtements AI

Video Face Swap

Échangez les visages dans n'importe quelle vidéo sans effort grâce à notre outil d'échange de visage AI entièrement gratuit !

Article chaud

Outils chauds

Bloc-notes++7.3.1

Éditeur de code facile à utiliser et gratuit

SublimeText3 version chinoise

Version chinoise, très simple à utiliser

Envoyer Studio 13.0.1

Puissant environnement de développement intégré PHP

Dreamweaver CS6

Outils de développement Web visuel

SublimeText3 version Mac

Logiciel d'édition de code au niveau de Dieu (SublimeText3)

Sujets chauds

1393

1393

52

52

1207

1207

24

24

Pourquoi le Gaussian Splatting est-il si populaire dans la conduite autonome que le NeRF commence à être abandonné ?

Jan 17, 2024 pm 02:57 PM

Pourquoi le Gaussian Splatting est-il si populaire dans la conduite autonome que le NeRF commence à être abandonné ?

Jan 17, 2024 pm 02:57 PM

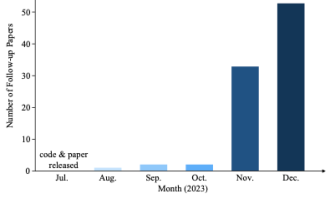

Écrit ci-dessus et compréhension personnelle de l'auteur Le Gaussiansplatting tridimensionnel (3DGS) est une technologie transformatrice qui a émergé dans les domaines des champs de rayonnement explicites et de l'infographie ces dernières années. Cette méthode innovante se caractérise par l’utilisation de millions de gaussiennes 3D, ce qui est très différent de la méthode du champ de rayonnement neuronal (NeRF), qui utilise principalement un modèle implicite basé sur les coordonnées pour mapper les coordonnées spatiales aux valeurs des pixels. Avec sa représentation explicite de scènes et ses algorithmes de rendu différenciables, 3DGS garantit non seulement des capacités de rendu en temps réel, mais introduit également un niveau de contrôle et d'édition de scène sans précédent. Cela positionne 3DGS comme un révolutionnaire potentiel pour la reconstruction et la représentation 3D de nouvelle génération. À cette fin, nous fournissons pour la première fois un aperçu systématique des derniers développements et préoccupations dans le domaine du 3DGS.

En savoir plus sur les emojis 3D Fluent dans Microsoft Teams

Apr 24, 2023 pm 10:28 PM

En savoir plus sur les emojis 3D Fluent dans Microsoft Teams

Apr 24, 2023 pm 10:28 PM

N'oubliez pas, surtout si vous êtes un utilisateur de Teams, que Microsoft a ajouté un nouveau lot d'émojis 3DFluent à son application de visioconférence axée sur le travail. Après que Microsoft a annoncé des emojis 3D pour Teams et Windows l'année dernière, le processus a en fait permis de mettre à jour plus de 1 800 emojis existants pour la plate-forme. Cette grande idée et le lancement de la mise à jour des emoji 3DFluent pour les équipes ont été promus pour la première fois via un article de blog officiel. La dernière mise à jour de Teams apporte FluentEmojis à l'application. Microsoft affirme que les 1 800 emojis mis à jour seront disponibles chaque jour.

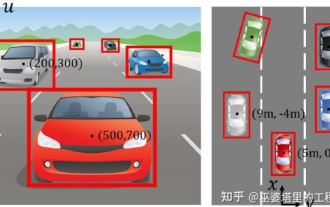

Choisir une caméra ou un lidar ? Une étude récente sur la détection robuste d'objets 3D

Jan 26, 2024 am 11:18 AM

Choisir une caméra ou un lidar ? Une étude récente sur la détection robuste d'objets 3D

Jan 26, 2024 am 11:18 AM

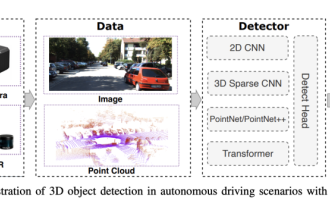

0. Écrit à l'avant&& Compréhension personnelle que les systèmes de conduite autonome s'appuient sur des technologies avancées de perception, de prise de décision et de contrôle, en utilisant divers capteurs (tels que caméras, lidar, radar, etc.) pour percevoir l'environnement et en utilisant des algorithmes et des modèles pour une analyse et une prise de décision en temps réel. Cela permet aux véhicules de reconnaître les panneaux de signalisation, de détecter et de suivre d'autres véhicules, de prédire le comportement des piétons, etc., permettant ainsi de fonctionner en toute sécurité et de s'adapter à des environnements de circulation complexes. Cette technologie attire actuellement une grande attention et est considérée comme un domaine de développement important pour l'avenir des transports. . un. Mais ce qui rend la conduite autonome difficile, c'est de trouver comment faire comprendre à la voiture ce qui se passe autour d'elle. Cela nécessite que l'algorithme de détection d'objets tridimensionnels du système de conduite autonome puisse percevoir et décrire avec précision les objets dans l'environnement, y compris leur emplacement,

CLIP-BEVFormer : superviser explicitement la structure BEVFormer pour améliorer les performances de détection à longue traîne

Mar 26, 2024 pm 12:41 PM

CLIP-BEVFormer : superviser explicitement la structure BEVFormer pour améliorer les performances de détection à longue traîne

Mar 26, 2024 pm 12:41 PM

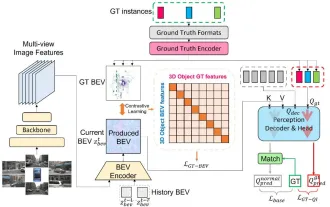

Écrit ci-dessus et compréhension personnelle de l'auteur : À l'heure actuelle, dans l'ensemble du système de conduite autonome, le module de perception joue un rôle essentiel. Le véhicule autonome roulant sur la route ne peut obtenir des résultats de perception précis que via le module de perception en aval. dans le système de conduite autonome, prend des jugements et des décisions comportementales opportuns et corrects. Actuellement, les voitures dotées de fonctions de conduite autonome sont généralement équipées d'une variété de capteurs d'informations de données, notamment des capteurs de caméra à vision panoramique, des capteurs lidar et des capteurs radar à ondes millimétriques pour collecter des informations selon différentes modalités afin d'accomplir des tâches de perception précises. L'algorithme de perception BEV basé sur la vision pure est privilégié par l'industrie en raison de son faible coût matériel et de sa facilité de déploiement, et ses résultats peuvent être facilement appliqués à diverses tâches en aval.

Paint 3D sous Windows 11 : guide de téléchargement, d'installation et d'utilisation

Apr 26, 2023 am 11:28 AM

Paint 3D sous Windows 11 : guide de téléchargement, d'installation et d'utilisation

Apr 26, 2023 am 11:28 AM

Lorsque les rumeurs ont commencé à se répandre selon lesquelles le nouveau Windows 11 était en développement, chaque utilisateur de Microsoft était curieux de savoir à quoi ressemblerait le nouveau système d'exploitation et ce qu'il apporterait. Après de nombreuses spéculations, Windows 11 est là. Le système d'exploitation est livré avec une nouvelle conception et des modifications fonctionnelles. En plus de quelques ajouts, il s’accompagne de fonctionnalités obsolètes et supprimées. L'une des fonctionnalités qui n'existe pas dans Windows 11 est Paint3D. Bien qu'il propose toujours Paint classique, idéal pour les dessinateurs, les griffonneurs et les griffonneurs, il abandonne Paint3D, qui offre des fonctionnalités supplémentaires idéales pour les créateurs 3D. Si vous recherchez des fonctionnalités supplémentaires, nous recommandons Autodesk Maya comme le meilleur logiciel de conception 3D. comme

Obtenez une femme virtuelle en 3D en 30 secondes avec une seule carte ! Text to 3D génère un humain numérique de haute précision avec des détails de pores clairs, se connectant de manière transparente à Maya, Unity et d'autres outils de production.

May 23, 2023 pm 02:34 PM

Obtenez une femme virtuelle en 3D en 30 secondes avec une seule carte ! Text to 3D génère un humain numérique de haute précision avec des détails de pores clairs, se connectant de manière transparente à Maya, Unity et d'autres outils de production.

May 23, 2023 pm 02:34 PM

ChatGPT a injecté une dose de sang de poulet dans l’industrie de l’IA, et tout ce qui était autrefois impensable est devenu aujourd’hui une pratique de base. Le Text-to-3D, qui continue de progresser, est considéré comme le prochain point chaud dans le domaine de l'AIGC après la diffusion (images) et le GPT (texte), et a reçu une attention sans précédent. Non, un produit appelé ChatAvatar a été mis en version bêta publique discrète, recueillant rapidement plus de 700 000 vues et attention, et a été présenté sur Spacesoftheweek. △ChatAvatar prendra également en charge la technologie Imageto3D qui génère des personnages stylisés en 3D à partir de peintures originales à perspective unique/multi-perspective générées par l'IA. Le modèle 3D généré par la version bêta actuelle a reçu une large attention.

Une interprétation approfondie de l'algorithme de perception visuelle 3D pour la conduite autonome

Jun 02, 2023 pm 03:42 PM

Une interprétation approfondie de l'algorithme de perception visuelle 3D pour la conduite autonome

Jun 02, 2023 pm 03:42 PM

Pour les applications de conduite autonome, il est finalement nécessaire de percevoir des scènes 3D. La raison est simple : un véhicule ne peut pas conduire sur la base des résultats de perception obtenus à partir d’une image. Même un conducteur humain ne peut pas conduire sur la base d’une image. Étant donné que la distance de l'objet et les informations sur la profondeur de la scène ne peuvent pas être reflétées dans les résultats de perception 2D, ces informations sont la clé permettant au système de conduite autonome de porter des jugements corrects sur l'environnement. De manière générale, les capteurs visuels (comme les caméras) des véhicules autonomes sont installés au-dessus de la carrosserie du véhicule ou sur le rétroviseur intérieur. Peu importe où elle se trouve, la caméra obtient la projection du monde réel dans la vue en perspective (PerspectiveView) (du système de coordonnées mondiales au système de coordonnées de l'image). Cette vue est très similaire au système visuel humain,

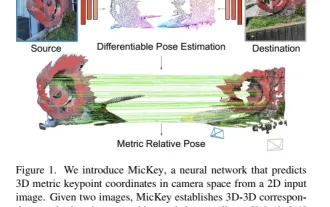

Les dernières nouvelles de l'Université d'Oxford ! Mickey : correspondance d'images 2D en 3D SOTA ! (CVPR\'24)

Apr 23, 2024 pm 01:20 PM

Les dernières nouvelles de l'Université d'Oxford ! Mickey : correspondance d'images 2D en 3D SOTA ! (CVPR\'24)

Apr 23, 2024 pm 01:20 PM

Lien du projet écrit devant : https://nianticlabs.github.io/mickey/ Étant donné deux images, la pose de la caméra entre elles peut être estimée en établissant la correspondance entre les images. En règle générale, ces correspondances sont 2D à 2D et nos poses estimées sont à échelle indéterminée. Certaines applications, telles que la réalité augmentée instantanée, à tout moment et en tout lieu, nécessitent une estimation de pose des métriques d'échelle, elles s'appuient donc sur des estimateurs de profondeur externes pour récupérer l'échelle. Cet article propose MicKey, un processus de correspondance de points clés capable de prédire les correspondances métriques dans l'espace d'une caméra 3D. En apprenant la correspondance des coordonnées 3D entre les images, nous sommes en mesure de déduire des métriques relatives.