Opération et maintenance

Opération et maintenance

exploitation et maintenance Linux

exploitation et maintenance Linux

Combat pratique | Adresse d'entrée RISC-V Linux optimisation de la mémoire réservée 2M

Combat pratique | Adresse d'entrée RISC-V Linux optimisation de la mémoire réservée 2M

Combat pratique | Adresse d'entrée RISC-V Linux optimisation de la mémoire réservée 2M

L'article précédent a analysé la création de table de pages pour le démarrage de RISC-V Linux. Il a été mentionné que l'adresse d'entrée RISC-V Linux doit être alignée sur 2M. Aujourd'hui, je vais parler de la façon de résoudre le problème d'alignement 2M, ou de la manière de le faire. optimiser une partie de la mémoire.

Remarque : cet article est basé sur le noyau Linux5.10.111

Analyse de l'utilisation de la mémoire

Lorsque chaque puce quitte l'usine, son bootrom a été solidifié à l'intérieur de la puce. Supposons que l'adresse de. le bootrom est 0x0, c'est-à-dire ce qui précède. Après la mise sous tension, le programme commencera à s'exécuter à partir de l'adresse 0x0.

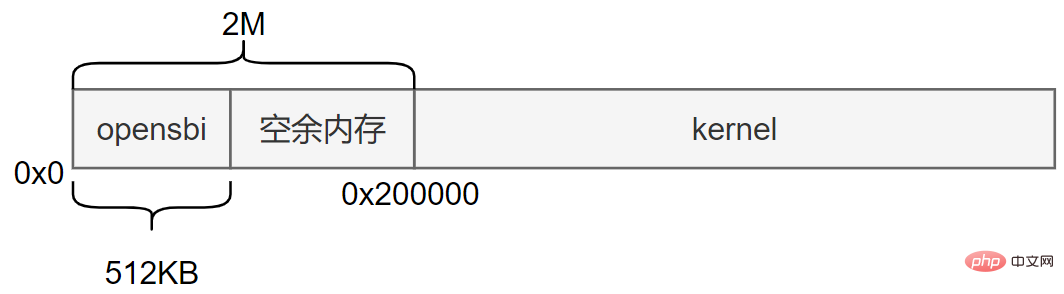

Avant de démarrer RISC-V Linux, vous devez d'abord exécuter opensbi, donc opensbi doit être placé à l'adresse 0x0处,这样芯片上电后,就会从0x0地址处执行opensbi。在opensbi运行完后,会跳转到opensbi运行地址偏移2M的位置去执行下一级boot(这里下一级boot是kernel),即跳转到0x200000地址处运行kernel,因此应该把kernel放到内存的0x200000.

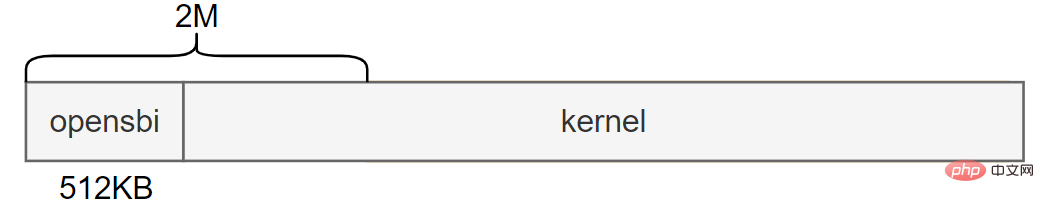

Le schéma de répartition de la mémoire est le suivant :

Pour le noyau, il chargera l'adresse de son propre noyau au démarrage (c'est-à-dire 0x200000) commence à établir le mappage de la table des pages. Ce n'est que lorsque le mappage de la table des pages est établi pour la mémoire physique que ces mémoires sont accessibles ultérieurement. Le noyau charge la mémoire 2M devant l'adresse (c'est-à-dire 0x0 - 0x200000) sera ignoré par le noyau et la table des pages ne sera pas établie pour ces 2 Mo de mémoire, c'est-à-dire que le noyau ne pourra pas accéder à ces 2 Mo de mémoire. 0x200000)开始建立页表映射,只有对物理内存建立了页表映射,后面才能访问这些内存。而kernel加载地址前面的2M内存(即0x0 - 0x200000)将被kernel忽略,不会对这2M内存建立页表,即kernel无法访问这2M内存。

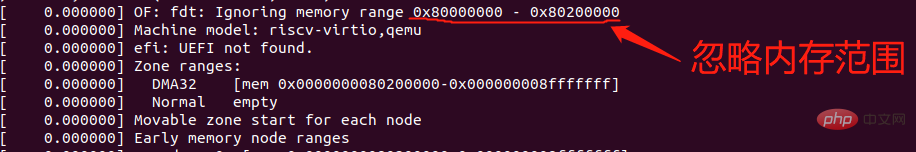

在QEMU上RISC-V Linux的启动信息:

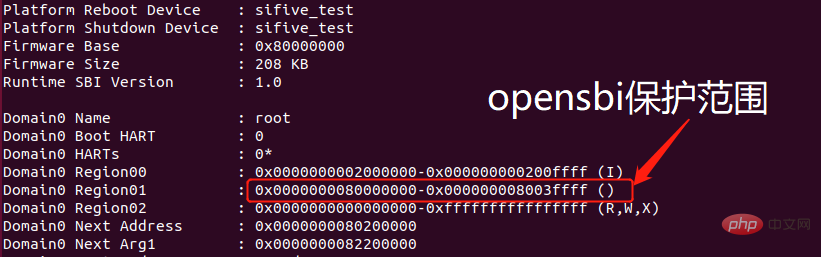

但opensbi实际不需要使用2M这么大的范围,默认是512KB,opensbi的pmp会保护这512KB内存,不让其他程序访问。

因此在Kernel和opensbi之间会存在1.5M

Mais opensbi n'a pas réellement besoin d'utiliser une plage aussi grande que 2M. La valeur par défaut est 512 Ko, le pmp d'opensbi protégera ceci512 Ko mémoire, non accessible à d'autres programmes.

Il y aura donc 1,5 M espace mémoire et cette partie de l'espace mémoire n'est pas utilisée par le programme, ce qui entraînera un gaspillage de mémoire. Alors comment laisser le noyau utiliser la partie précédente de la mémoire ?

Plan d'optimisation

Il existe deux plans pour optimiser cette mémoire de 2 Mo : 🎜🎜🎜Option 1🎜 : Mettez opensbi à la fin de la mémoire, et l'adresse d'entrée du noyau conserve toujours l'alignement de 2 M. 🎜🎜🎜Option 2🎜 : Opensbi est toujours placé au début de la mémoire. En modifiant le code source du noyau et en levant la restriction d'alignement 2M, l'adresse du noyau peut être avancée. 🎜

Option 1

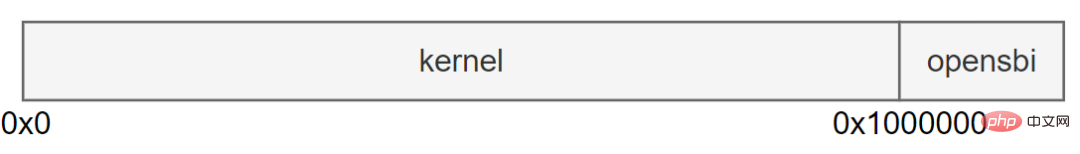

Nous mettons opensbi à la fin de la mémoire, et l'adresse d'entrée du noyau maintient toujours l'alignement 2M.

C'est-à-dire que le noyau est placé à l'avant de la mémoire, et opensbi est placé à l'arrière :

Par exemple, le noyau est placé à l'adresse 0x0地址处,opensbi放到内存的0x10000000地址处。这样kernel前面就不会有预留内存,只不过这样需要修改bootrom的地址,将地址从0x0修改为0x0x10000000。这种方案只适合芯片还没出厂前,因为用户无法修改bootrom的地址,芯片出厂后,bootrom地址是固定的,假设bootrom地址为0x0,那么芯片上电后,就会从0x0开始运行程序,所以opensbi必须放到0x0 de la mémoire, donc le noyau ne peut être décalé de 2M.

Option 2

Nous pouvons également modifier le code source du noyau de RISC-V Linux pour lever la restriction d'alignement 2M. Il nous suffit de setup_vm (), changez la table de pages de deuxième niveau d'origine en une table de pages de troisième niveau, de sorte que l'adresse d'entrée du noyau n'ait besoin que d'être alignée sur 4K, afin que le noyau puisse être avancé, utilisant ainsi la mémoire avant. setup_vm()函数中,将原来的二级页表改为三级页表,这样kernel入口地址只需要4K对齐,因此就能将kernel往前挪,从而利用前面的内存。

修改代码

路径:arch/riscv/mm/init.c

Modifier le code

Chemin :

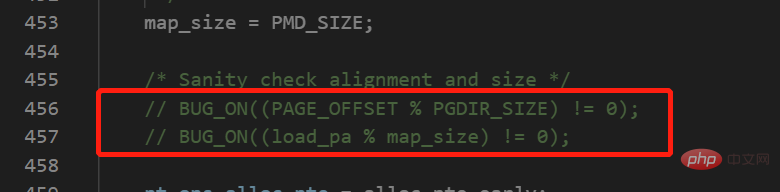

Chemin : arch /riscv/mm/init.cCommentez la vérification d'alignement 2M d'origine :

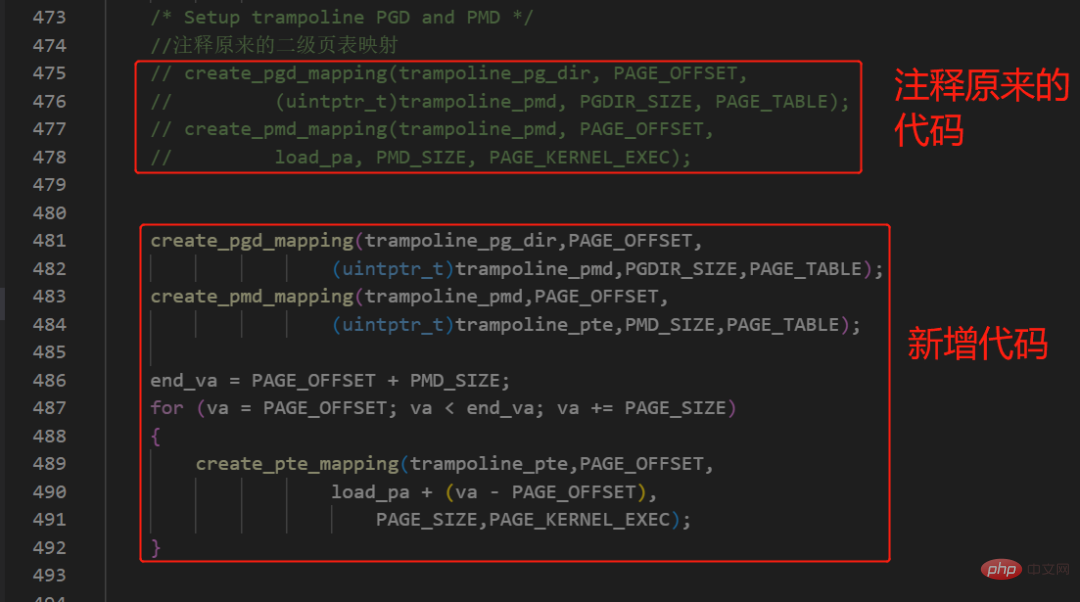

Modifiez le premier mappage de la table de pages 2M du noyau de la table des pages de deuxième niveau à la table des pages de troisième niveau :

//新增一个PTE

pte_t trampoline_pte[PTRS_PER_PTE] __page_aligned_bss;

create_pgd_mapping(trampoline_pg_dir,PAGE_OFFSET,

(uintptr_t)trampoline_pmd,PGDIR_SIZE,PAGE_TABLE);

create_pmd_mapping(trampoline_pmd,PAGE_OFFSET,

(uintptr_t)trampoline_pte,PMD_SIZE,PAGE_TABLE);

end_va = PAGE_OFFSET + PMD_SIZE;

for (va = PAGE_OFFSET; va < end_va; va += PAGE_SIZE)

{

create_pte_mapping(trampoline_pte,PAGE_OFFSET,

load_pa + (va - PAGE_OFFSET),

PAGE_SIZE,PAGE_KERNEL_EXEC);

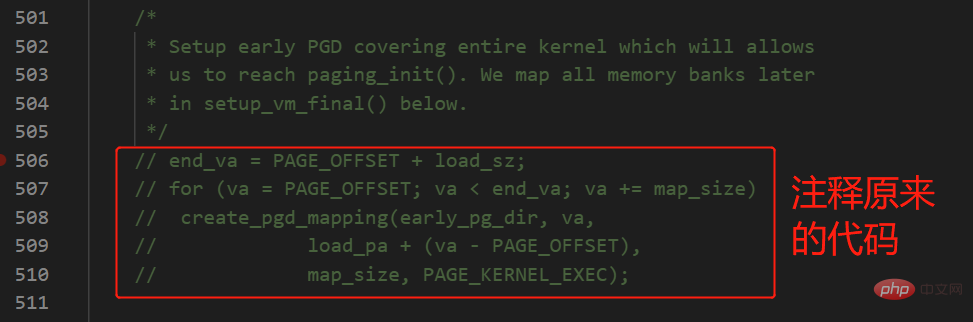

}Le mappage de la table des pages de l'ensemble du noyau est modifié de la table des pages de deuxième niveau à la table des pages de troisième niveau :

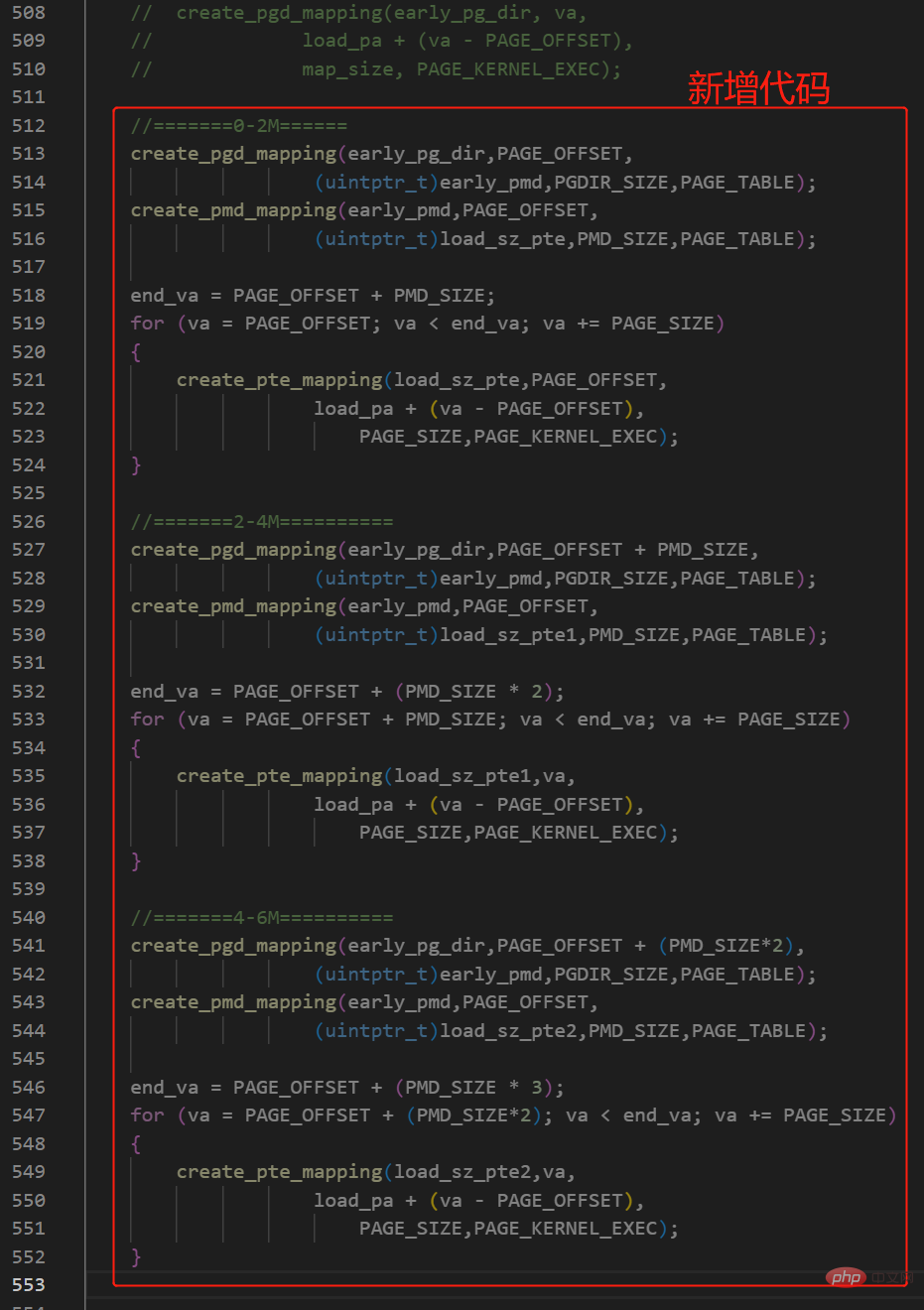

//定义三个PTE

pte_t load_sz_pte[PTRS_PER_PTE] __page_aligned_bss;

pte_t load_sz_pte1[PTRS_PER_PTE] __page_aligned_bss;

pte_t load_sz_pte2[PTRS_PER_PTE] __page_aligned_bss;

//=======0-2M======

create_pgd_mapping(early_pg_dir,PAGE_OFFSET,

(uintptr_t)early_pmd,PGDIR_SIZE,PAGE_TABLE);

create_pmd_mapping(early_pmd,PAGE_OFFSET,

(uintptr_t)load_sz_pte,PMD_SIZE,PAGE_TABLE);

end_va = PAGE_OFFSET + PMD_SIZE;

for (va = PAGE_OFFSET; va < end_va; va += PAGE_SIZE)

{

create_pte_mapping(load_sz_pte,PAGE_OFFSET,

load_pa + (va - PAGE_OFFSET),

PAGE_SIZE,PAGE_KERNEL_EXEC);

}

//=======2-4M==========

create_pgd_mapping(early_pg_dir,PAGE_OFFSET + PMD_SIZE,

(uintptr_t)early_pmd,PGDIR_SIZE,PAGE_TABLE);

create_pmd_mapping(early_pmd,PAGE_OFFSET,

(uintptr_t)load_sz_pte1,PMD_SIZE,PAGE_TABLE);

end_va = PAGE_OFFSET + (PMD_SIZE * 2);

for (va = PAGE_OFFSET + PMD_SIZE; va < end_va; va += PAGE_SIZE)

{

create_pte_mapping(load_sz_pte1,va,

load_pa + (va - PAGE_OFFSET),

PAGE_SIZE,PAGE_KERNEL_EXEC);

}

//=======4-6M==========

create_pgd_mapping(early_pg_dir,PAGE_OFFSET + (PMD_SIZE*2),

(uintptr_t)early_pmd,PGDIR_SIZE,PAGE_TABLE);

create_pmd_mapping(early_pmd,PAGE_OFFSET,

(uintptr_t)load_sz_pte2,PMD_SIZE,PAGE_TABLE);

end_va = PAGE_OFFSET + (PMD_SIZE * 3);

for (va = PAGE_OFFSET + (PMD_SIZE*2); va < end_va; va += PAGE_SIZE)

{

create_pte_mapping(load_sz_pte2,va,

load_pa + (va - PAGE_OFFSET),

PAGE_SIZE,PAGE_KERNEL_EXEC);

}

Résumé

L'opération d'alignement de l'adresse d'entrée Linux RISC-V 2M n'a pas encore été expliquée, mais elle devrait être de réserver 2M pour opensbi, de sorte que le noyau n'a établi qu'une table de pages secondaire, de sorte que l'adresse d'entrée doit être alignée sur 2M. Personne n'a encore donné de solution d'optimisation pour cette partie de la mémoire. J'espère que la solution d'optimisation présentée dans cet article pourra aider certaines personnes et vous inspirer.

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!

Outils d'IA chauds

Undresser.AI Undress

Application basée sur l'IA pour créer des photos de nu réalistes

AI Clothes Remover

Outil d'IA en ligne pour supprimer les vêtements des photos.

Undress AI Tool

Images de déshabillage gratuites

Clothoff.io

Dissolvant de vêtements AI

AI Hentai Generator

Générez AI Hentai gratuitement.

Article chaud

Outils chauds

Bloc-notes++7.3.1

Éditeur de code facile à utiliser et gratuit

SublimeText3 version chinoise

Version chinoise, très simple à utiliser

Envoyer Studio 13.0.1

Puissant environnement de développement intégré PHP

Dreamweaver CS6

Outils de développement Web visuel

SublimeText3 version Mac

Logiciel d'édition de code au niveau de Dieu (SublimeText3)

Explorer les fonctions du noyau Linux : une introduction détaillée aux cinq parties principales

Mar 21, 2024 am 09:57 AM

Explorer les fonctions du noyau Linux : une introduction détaillée aux cinq parties principales

Mar 21, 2024 am 09:57 AM

En tant qu'élément central du système d'exploitation, le noyau Linux est responsable de fonctions importantes telles que la gestion des ressources matérielles et la fourniture d'appels système. Cet article se penchera sur les cinq parties principales du noyau Linux, notamment la gestion des processus, le système de fichiers, la communication réseau, les pilotes de périphériques et la gestion de la mémoire, et fournira une introduction détaillée et des exemples de code. 1. Gestion des processus Création de processus Dans le noyau Linux, la création de processus est implémentée via l'appel système fork(). Voici un exemple de code simple : #include

Le support non-MMU est-il fourni par le port uClinux du noyau Linux ?

Jan 26, 2024 pm 05:18 PM

Le support non-MMU est-il fourni par le port uClinux du noyau Linux ?

Jan 26, 2024 pm 05:18 PM

Il est long et contient beaucoup de contenu technique, alors cliquez pour le suivre et vous ne vous perdrez pas. Préface : Comprendre le noyau Linux Un système informatique est une symbiose de matériel et de logiciels. Ils sont interdépendants et indissociables. Les étapes de transplantation du noyau Linux sur le matériel informatique comprennent les périphériques, les processeurs, la mémoire, les disques durs et autres appareils électroniques qui composent le cylindre de l'ordinateur. Et sans logiciel pour le faire fonctionner et le contrôler, il ne peut pas fonctionner tout seul. Le logiciel qui effectue ce travail de contrôle s'appelle le système d'exploitation, appelé « noyau » dans la terminologie Linux, et peut également être appelé « noyau ». Les principaux modules (ou composants) du noyau Linux sont divisés en parties suivantes : gestion du stockage, gestion du processeur et des processus, système de fichiers, gestion des périphériques et pilotes, forum Linux de communication réseau et système.

Combat pratique | Adresse d'entrée RISC-V Linux optimisation de la mémoire réservée 2M

Aug 01, 2023 pm 03:37 PM

Combat pratique | Adresse d'entrée RISC-V Linux optimisation de la mémoire réservée 2M

Aug 01, 2023 pm 03:37 PM

L'article précédent a analysé la création de table de pages pour le démarrage de RISC-V Linux. Il a été mentionné que l'adresse d'entrée RISC-V Linux doit être alignée sur 2M. Aujourd'hui, je vais parler de la façon de résoudre le problème d'alignement 2M ou d'en optimiser une partie. la mémoire.

Des conseils secrets pour l'optimisation de la pile de protocole TCP du noyau Linux révélés

Jan 28, 2024 am 09:39 AM

Des conseils secrets pour l'optimisation de la pile de protocole TCP du noyau Linux révélés

Jan 28, 2024 am 09:39 AM

Bonjour chers lecteurs ! Ici, j'ai l'honneur de partager avec vous l'expérience et les compétences précieuses que j'ai accumulées en tant qu'ingénieur réseau senior grâce à mes compétences professionnelles dans le développement et l'optimisation de la pile de protocole TCP du noyau Linux. Je crois que grâce à cet article, nous pouvons apprendre les uns des autres et en discuter, et vous apporter des documents de référence pratiques et utiles qui sont fortement intéressés par ce domaine ou qui effectuent un travail connexe. 1. Établissement d'une connexion TCP L'établissement d'une connexion TCP est une transaction clé de la pile de protocoles TCP, mais il n'est pas rare de rencontrer de nombreux problèmes de connexion. Après un examen attentif et un débogage détaillé, j'ai découvert certains problèmes courants et pratiques ainsi que leurs solutions, notamment la prévention des attaques par inondation SYN (en ajustant les paramètres du système) et la gestion de la congestion du réseau (c'est-à-dire en utilisant TCPFastOp

Noyau Linux : révéler le BOSS caché des systèmes d'exploitation informatiques

Mar 24, 2024 am 09:10 AM

Noyau Linux : révéler le BOSS caché des systèmes d'exploitation informatiques

Mar 24, 2024 am 09:10 AM

Discute de l'idée selon laquelle le noyau Linux joue un rôle important dans la conception et la mise en œuvre du noyau Linux. Grâce à une analyse approfondie de la conception du noyau Linux et de ses applications pratiques, il révèle sa position et son influence de premier plan dans ce domaine. 1. Gestion optimisée de la mémoire En utilisant la technologie de gestion de la mémoire virtuelle, le noyau Linux peut effectuer efficacement l'allocation et le recyclage de la mémoire. À l'aide de l'algorithme de page de remplacement, le noyau Linux est conçu et implémenté pour gérer avec précision la relation de mappage entre la mémoire physique et la mémoire virtuelle. Des ajustements flexibles peuvent être effectués en fonction des besoins spécifiques de l'application, améliorant ainsi les performances globales du système. 2. Le puissant noyau de gestion des processus utilise son excellente technologie multitâche pour permettre à plusieurs processus de coexister harmonieusement dans un seul système. Soigneusement formulé

Une exploration approfondie de la distribution du code source du noyau Linux

Mar 15, 2024 am 10:21 AM

Une exploration approfondie de la distribution du code source du noyau Linux

Mar 15, 2024 am 10:21 AM

Il s'agit d'un article de 1 500 mots qui explore en profondeur la distribution du code source du noyau Linux. En raison de l'espace limité, nous nous concentrerons sur la structure organisationnelle du code source du noyau Linux et fournirons quelques exemples de code spécifiques pour aider les lecteurs à mieux comprendre. Le noyau Linux est un noyau de système d'exploitation open source dont le code source est hébergé sur GitHub. La distribution entière du code source du noyau Linux est très vaste, contenant des centaines de milliers de lignes de code, impliquant plusieurs sous-systèmes et modules différents. Pour mieux comprendre le code source du noyau Linux

Explorez la relation entre le système Android et le noyau Linux

Mar 14, 2024 pm 12:48 PM

Explorez la relation entre le système Android et le noyau Linux

Mar 14, 2024 pm 12:48 PM

Le système Android et le noyau Linux sont deux entités étroitement liées, et la relation entre eux est étroite et complexe. Dans le système Android, le noyau Linux joue un rôle important, fournissant les pilotes matériels sous-jacents et la prise en charge des appels système pour le système Android. Cet article explorera la relation entre le système Android et le noyau Linux, la manière dont ils interagissent et fonctionnent ensemble, et fournira quelques exemples de code spécifiques. Android est un système d'exploitation mobile développé sur la base du noyau Linux et est principalement utilisé pour les appareils mobiles tels que les smartphones et les tablettes. L

Savez-vous vraiment comment déboguer les pannes du noyau Linux ? Vous serez éclairé après avoir lu cet article !

Aug 03, 2023 pm 04:50 PM

Savez-vous vraiment comment déboguer les pannes du noyau Linux ? Vous serez éclairé après avoir lu cet article !

Aug 03, 2023 pm 04:50 PM

Le noyau Linux est le cœur du système d'exploitation et contrôle l'accès aux ressources système telles que le processeur, les périphériques d'E/S, la mémoire physique et les systèmes de fichiers. Pendant le processus de démarrage et pendant que le système est en cours d'exécution, le noyau écrit divers messages dans le tampon en anneau du noyau. Ces messages incluent diverses informations sur les opérations du système.