Le 27 septembre, Samsung Electronics a annoncé hier avoir développé avec succès un nouveau module de mémoire complémentaire compressée à faible consommation de 7,5 Gbit/s (LPCAMM). Cette spécification innovante marque une avancée majeure dans la technologie de mémoire future. Le module combine les caractéristiques de taille compacte et de détachable et devrait être commercialisé en 2024.

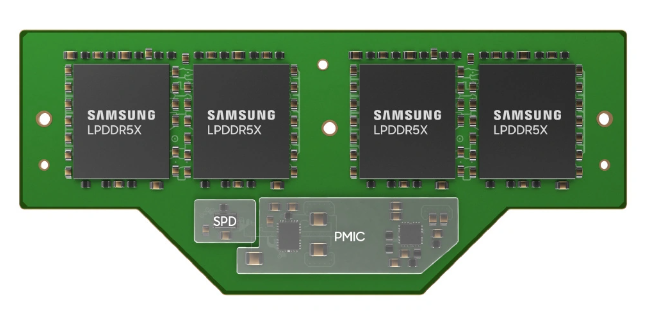

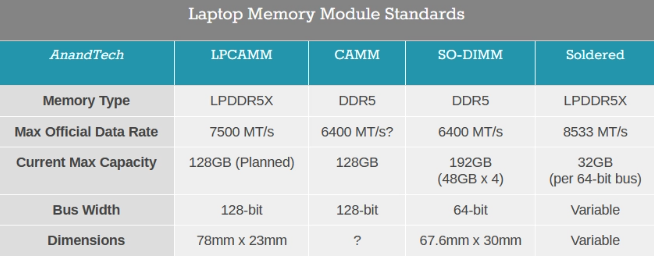

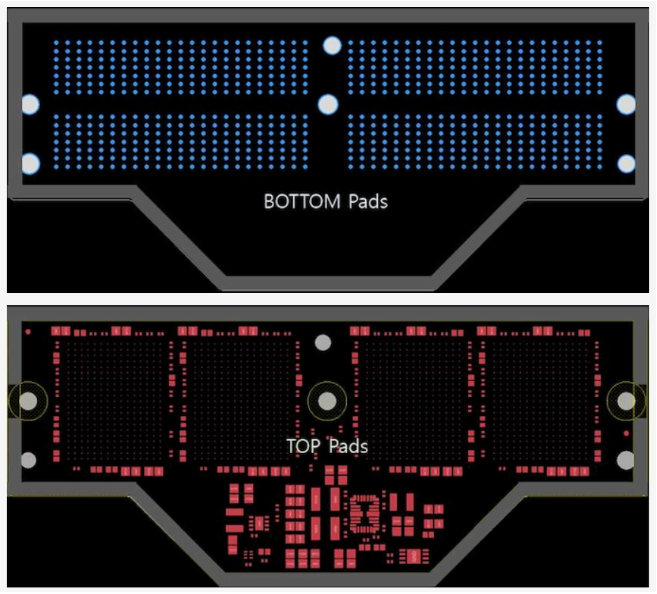

Il est rapporté que la mémoire LPCAMM est une innovation technologique améliorée par Samsung sur la base de la mémoire LPDDR. Malgré la similitude de nom avec CAMM, ils sont en réalité physiquement et électriquement incompatibles. La conception unique de ce module de mémoire est qu'il regroupe directement quatre particules de mémoire LPDDR5X de 32 bits sur un connecteur de compression, permettant l'utilisation d'un bus mémoire de 128 bits. Il ressort d'un diagramme de plots que les contacts de la mémoire LPCAMM sont situés à l'arrière de la carte PCB, très proches des particules de mémoire, raccourcissant ainsi considérablement la distance de transmission du signal.

La taille de la mémoire LPCAMM est de 78 mm x

23 mm, en plus du boîtier DRAM lui-même, il comprend également un SPD et un circuit intégré de gestion de l'alimentation (PMIC). Semblable à la norme CAMM, il permet au module de fournir ses propres fonctions de régulation de tension et d'identification. Initialement, Samsung prévoit de lancer des versions de 32 Go, 64 Go et 128 Go de mémoire LPCAMM, prenant en charge le débit de données du LPDDR5X-7500. Cependant, étant donné qu'il n'existe actuellement pas de 256 Gbit

Puces mémoire LPDDR5X, pour obtenir une seule mémoire de 128 Go, vous devez soit installer 8 puces sur LPCAMM, soit augmenter la taille globale du module de mémoire.

Selon l'éditeur, Samsung a terminé avec succès la vérification du système sur la plate-forme Intel et prévoit d'effectuer des tests LPCAMM avec des clients majeurs, dont Intel, en 2023. De plus, ils travaillent avec des partenaires pour développer la norme JEDEC pour LPCAMM afin de promouvoir la standardisation de cette technologie. Dans le même temps, JEDEC étend également activement la norme CAMM pour couvrir la mémoire LPDDR et implémente les mêmes normes de connecteur que DDR5 et LPDDR5, ouvrant ainsi la voie au développement futur de la technologie de mémoire. Cette série d'innovations devrait améliorer les performances et l'efficacité de la mémoire des appareils mobiles et des ordinateurs, ouvrant ainsi de nouvelles possibilités pour le développement technologique futur.

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!