Périphériques technologiques

Périphériques technologiques

Industrie informatique

Industrie informatique

La mémoire HBM4 est en cours de développement et utilisera une interface plus large de 2048 bits

La mémoire HBM4 est en cours de développement et utilisera une interface plus large de 2048 bits

La mémoire HBM4 est en cours de développement et utilisera une interface plus large de 2048 bits

Les nouvelles officielles de Samsung montrent que la mémoire HBM pour le calcul haute performance (HPC) a fait de nouveaux progrès. Le produit HBM3E à 9,8 Gbit/s a commencé à être échantillonné auprès des clients, tandis que la mémoire HBM4 devrait être lancée en 2025

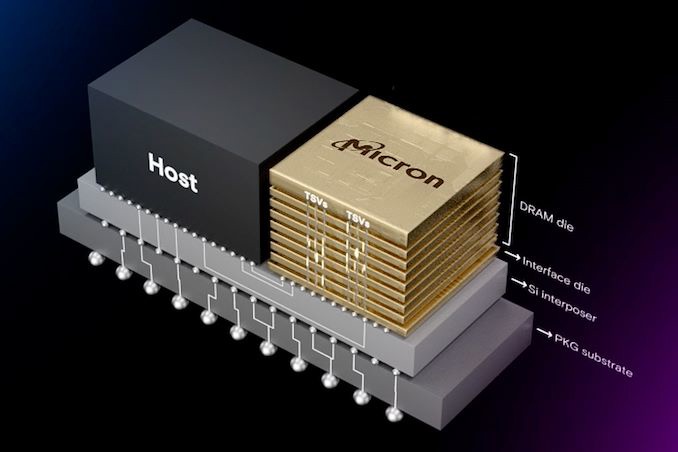

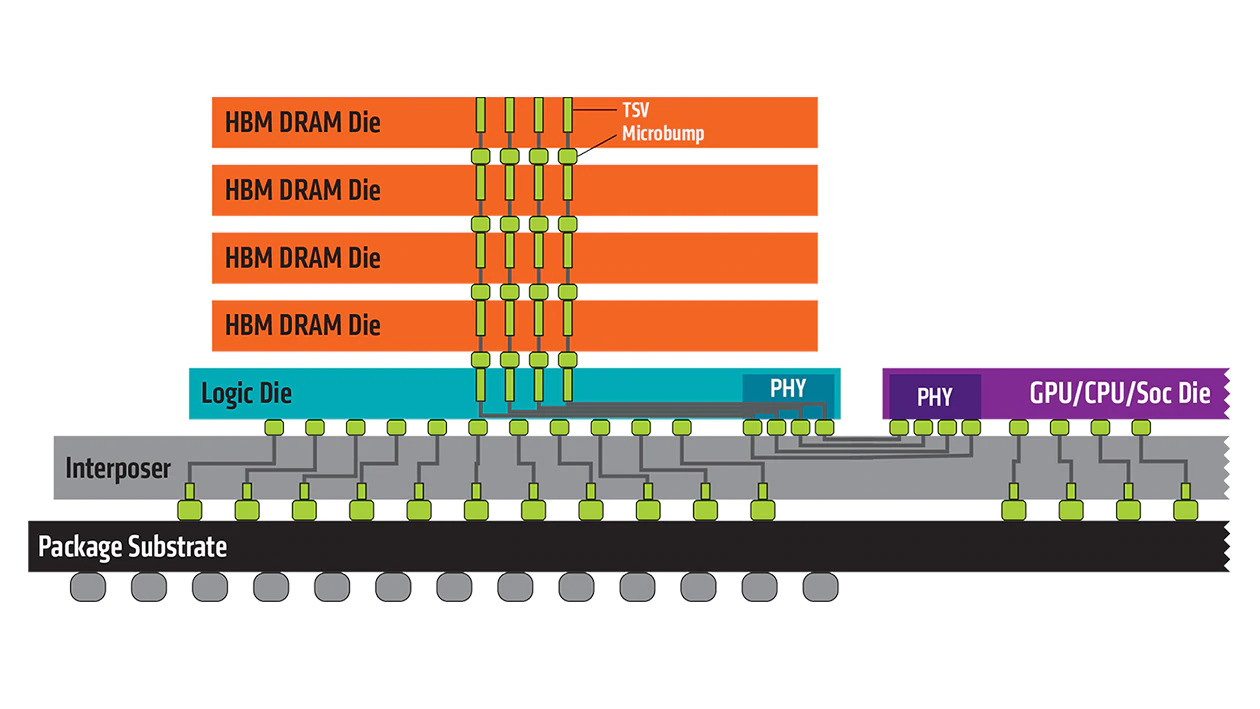

Bien qu'il n'y ait pas encore de spécifications officielles pour HBM4, TSMC a révélé certaines normes en cours de développement lors du forum OIP 2023. TSMC a déclaré qu'à l'avenir, la largeur de bit de l'interface de la mémoire HBM4 doublera pour atteindre 2048 bits

Il convient de mentionner que pour diverses raisons techniques, ils espèrent également le faire sans augmenter l'espace occupé par la pile de mémoire HBM. Atteindre cet objectif doublera également la densité d'interconnexion de la mémoire HBM de nouvelle génération sans augmenter davantage les vitesses d'horloge.

Selon le plan, cela permettra à HBM4 de réaliser des avancées majeures à plusieurs niveaux techniques

En termes d'empilement de DRAM, une interface mémoire de 2048 bits nécessite une augmentation significative du nombre de vias traversants en silicium. Dans le même temps, l'interface de la puce externe devra réduire le pas des bosses à moins de 55 microns et augmenter considérablement le nombre de micro-bosses (Remarque sur ce site : le HBM3 compte actuellement environ 3982 micro-bosses).

De plus, HBM4 adoptera le mode d'empilement 16-Hi, qui empile 16 puces mémoire dans un module, augmentant ainsi la complexité technique (bien que d'un point de vue technique, HBM3 prenne également en charge l'empilement 16-Hi, mais donc jusqu'à présent, aucun fabricant n'a adopté cette approche)

Tous ces nouveaux paramètres nécessitent à leur tour une approche collaborative plus étroite entre les fabricants de puces, les fabricants de mémoire et les entreprises d'emballage de puces pour garantir que tout se passe bien.

Lors de la conférence TSMC OIP 2023 à Amsterdam, Dan Kochpatcharin, responsable de la gestion de l'infrastructure de conception chez TSMC, a déclaré : « Parce qu'au lieu de doubler la vitesse, ils ont doublé les broches [de l'interface] [Avec HBM4] C'est pourquoi nous travaillons dur pour assurez-vous que nous travaillons avec les trois partenaires pour rendre leur HBM4 [disponible via notre emballage avancé] qualifié et assurez-vous que le RDL ou le médiateur ou tout ce qui se trouve entre les deux. Tout le contenu peut prendre en charge la mise en page et la vitesse de HBM4. Par conséquent, nous maintenons. coopération avec Samsung, SK Hynix et Micron. Les résultats sont à titre de référence uniquement. Tous les articles de ce site contiennent cette déclaration.

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!

Outils d'IA chauds

Undresser.AI Undress

Application basée sur l'IA pour créer des photos de nu réalistes

AI Clothes Remover

Outil d'IA en ligne pour supprimer les vêtements des photos.

Undress AI Tool

Images de déshabillage gratuites

Clothoff.io

Dissolvant de vêtements AI

AI Hentai Generator

Générez AI Hentai gratuitement.

Article chaud

Outils chauds

Bloc-notes++7.3.1

Éditeur de code facile à utiliser et gratuit

SublimeText3 version chinoise

Version chinoise, très simple à utiliser

Envoyer Studio 13.0.1

Puissant environnement de développement intégré PHP

Dreamweaver CS6

Outils de développement Web visuel

SublimeText3 version Mac

Logiciel d'édition de code au niveau de Dieu (SublimeText3)

Samsung va lancer le SSD PM1753 de qualité centre de données : 14,8 Go/s en lecture séquentielle, 3,4 millions d'IOPS en lecture aléatoire

Aug 08, 2024 pm 04:40 PM

Samsung va lancer le SSD PM1753 de qualité centre de données : 14,8 Go/s en lecture séquentielle, 3,4 millions d'IOPS en lecture aléatoire

Aug 08, 2024 pm 04:40 PM

Selon les informations de ce site du 8 août, Samsung a présenté un certain nombre de nouveaux produits SSD lors du Flash Memory Summit (FMS) 2024 - PM1753, BM1743, PM9D3a, PM9E1, et a également testé les QLCV-NAND, TLCV-NAND et TLCV-NAND de neuvième génération. Les technologies CMM-D –DRAM, CMM-HTM, CMM-HPM et CMM-BCXL ont été introduites. Le BM1743 utilise une mémoire flash QLC d'une capacité allant jusqu'à 128 To, une vitesse de lecture continue de 7,5 Go/s, une vitesse d'écriture de 3,5 Go/s, une lecture aléatoire de 1,6 million d'IOPS et une écriture de 45 000 IOPS. Facteur de forme de 2,5 pouces et une interface U.2, et est inactif La consommation d'énergie est réduite à 4 W, et après les mises à jour OTA ultérieures, seulement

Taux de transfert le plus élevé du secteur, soit 3,6 Go/s, Micron annonce la production en série d'une mémoire flash NAND TLC à 276 couches de neuvième génération

Jul 31, 2024 am 08:05 AM

Taux de transfert le plus élevé du secteur, soit 3,6 Go/s, Micron annonce la production en série d'une mémoire flash NAND TLC à 276 couches de neuvième génération

Jul 31, 2024 am 08:05 AM

Selon les informations de ce site du 30 juillet, Micron a annoncé aujourd'hui (heure locale) que sa neuvième génération (note du site : 276 couches) de mémoire flash 3DTLC NAND serait produite et expédiée en série. Micron a déclaré que son G9NAND a le taux de transfert d'E/S le plus élevé du secteur, soit 3,6 Go/s (c'est-à-dire un taux d'interface de mémoire flash de 3 600 MT/s), soit 50 % plus élevé que les produits concurrents existants de 2 400 MT/s, et peut mieux répondre aux exigences. besoins des charges de travail gourmandes en données. Exigences de débit élevé. Dans le même temps, le G9NAND de Micron est respectivement 99 % et 88 % supérieur aux autres solutions du marché en termes de bande passante d'écriture et de bande passante de lecture. Cet avantage au niveau des particules NAND apportera des performances et une efficacité énergétique aux disques SSD et au stockage intégré. solutions. De plus, comme les générations précédentes de mémoire flash Micron NAND, Micron 276

Fuite du téléphone portable Samsung Galaxy S25 Ultra : 6,86 pouces, rapport écran/corps horizontal 94,1 %

Aug 17, 2024 pm 01:49 PM

Fuite du téléphone portable Samsung Galaxy S25 Ultra : 6,86 pouces, rapport écran/corps horizontal 94,1 %

Aug 17, 2024 pm 01:49 PM

Selon les informations du 17 août, la source @ibinguniverse a publié aujourd'hui sur Weibo, déclarant que la taille exacte de l'Apple iPhone 16 Pro Max est de 6,88 pouces et que la taille exacte du Galaxy S25 Ultra est de 6,86 pouces. . Des sources indiquent que le Samsung Galaxy S25 Ultra a un corps plus étroit et un écran plus large que le S24 Ultra, avec un rapport écran/corps horizontal de 94,1 %, tandis que le rapport écran/corps horizontal du S24 Ultra est de 91,5 %. Fenye a vérifié le Weibo de la source. Il a également commenté les photos récemment exposées de l'iPhone 16 Pro Max et a estimé qu'il était erroné d'être proche d'une micro-courbe. Le téléphone est en fait un écran droit + un verre 2,5D.

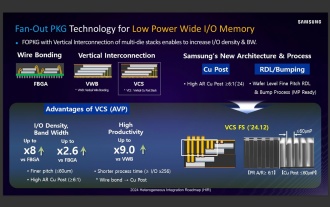

Des sources affirment que Samsung Electronics et SK Hynix commercialiseront de la mémoire mobile empilée après 2026

Sep 03, 2024 pm 02:15 PM

Des sources affirment que Samsung Electronics et SK Hynix commercialiseront de la mémoire mobile empilée après 2026

Sep 03, 2024 pm 02:15 PM

Selon des informations publiées sur ce site Web le 3 septembre, le média coréen etnews a rapporté hier (heure locale) que les produits de mémoire mobile à structure empilée « de type HBM » de Samsung Electronics et SK Hynix seraient commercialisés après 2026. Des sources ont indiqué que les deux géants coréens de la mémoire considèrent la mémoire mobile empilée comme une source importante de revenus futurs et prévoient d'étendre la « mémoire de type HBM » aux smartphones, tablettes et ordinateurs portables afin de fournir de la puissance à l'IA finale. Selon des rapports précédents sur ce site, le produit de Samsung Electronics s'appelle LPWide I/O memory, et SK Hynix appelle cette technologie VFO. Les deux sociétés ont utilisé à peu près la même voie technique, à savoir combiner emballage en sortance et canaux verticaux. La mémoire LPWide I/O de Samsung Electronics a une largeur de 512 bits.

Le téléphone pliable W25 de Samsung, d'une valeur de 10 000 yuans, dévoilé : une caméra frontale sous l'écran de 5 mégapixels et un corps plus fin

Aug 23, 2024 pm 12:43 PM

Le téléphone pliable W25 de Samsung, d'une valeur de 10 000 yuans, dévoilé : une caméra frontale sous l'écran de 5 mégapixels et un corps plus fin

Aug 23, 2024 pm 12:43 PM

Selon les informations du 23 août, Samsung est sur le point de lancer un nouveau téléphone mobile pliable W25, qui devrait être dévoilé fin septembre. Il apportera des améliorations correspondantes à la caméra frontale sous l'écran et à l'épaisseur du corps. Selon certaines informations, le Samsung W25, nom de code Q6A, sera équipé d'un appareil photo sous-écran de 5 mégapixels, ce qui constitue une amélioration par rapport à l'appareil photo de 4 mégapixels de la série Galaxy Z Fold. De plus, la caméra frontale à écran externe et la caméra ultra grand angle du W25 devraient respectivement mesurer 10 millions et 12 millions de pixels. En termes de conception, le W25 a une épaisseur d'environ 10 mm à l'état plié, soit environ 2 mm de moins que le Galaxy Z Fold 6 standard. En termes d'écran, le W25 dispose d'un écran externe de 6,5 pouces et d'un écran interne de 8 pouces, tandis que le Galaxy Z Fold6 dispose d'un écran externe de 6,3 pouces et d'un écran interne de 8 pouces.

Il est révélé que Samsung commencera à installer sa première machine de lithographie ASML High-NA EUV d'ici fin 2024 au plus tôt

Aug 16, 2024 am 11:11 AM

Il est révélé que Samsung commencera à installer sa première machine de lithographie ASML High-NA EUV d'ici fin 2024 au plus tôt

Aug 16, 2024 am 11:11 AM

Selon des informations de ce site du 16 août, le Seoul Economic Daily a rapporté hier (15 août) que Samsung installerait sa première machine de lithographie High-NAEUV d'ASML entre le quatrième trimestre 2024 et le premier trimestre 2025. Elle devrait être mis en service à la mi-2025. Les rapports indiquent que Samsung installera la première machine de lithographie ASMLTwinscanEXE:5000High-NA sur son campus de Hwaseong, qui sera principalement utilisée à des fins de recherche et développement pour développer des technologies de fabrication de nouvelle génération pour la logique et la DRAM. Samsung prévoit de développer un écosystème solide autour de la technologie High-NAEUV : en plus d'acquérir des équipements de lithographie à High-NAEUV, Samsung coopère également avec la société japonaise Lasertec pour développer des équipements de lithographie à High-NAEUV spécifiquement destinés aux équipements de lithographie à High-NAEUV.

Les noms de code complets de la série Xiaomi 15 révélés : Dada, Haotian, Xuanyuan

Aug 22, 2024 pm 06:47 PM

Les noms de code complets de la série Xiaomi 15 révélés : Dada, Haotian, Xuanyuan

Aug 22, 2024 pm 06:47 PM

La série Xiaomi Mi 15 devrait être officiellement lancée en octobre, et les noms de code de sa série complète ont été exposés dans la base de code MiCode des médias étrangers. Parmi eux, le produit phare Xiaomi Mi 15 Ultra porte le nom de code « Xuanyuan » (qui signifie « Xuanyuan »). Ce nom vient de l'Empereur Jaune dans la mythologie chinoise, qui symbolise la noblesse. Le Xiaomi 15 porte le nom de code « Dada », tandis que le Xiaomi 15Pro s'appelle « Haotian » (qui signifie « Haotian »). Le nom de code interne du Xiaomi Mi 15S Pro est « dijun », qui fait allusion à l'empereur Jun, le dieu créateur du « Classique des montagnes et des mers ». Couvertures de la série Xiaomi 15Ultra

Un premier aperçu du modèle de téléphone mobile Samsung Galaxy Z Fold6 / Flip6 Gemini Nano AI : fonctionnant localement, pas encore intégré au Galaxy AI

Aug 10, 2024 pm 01:59 PM

Un premier aperçu du modèle de téléphone mobile Samsung Galaxy Z Fold6 / Flip6 Gemini Nano AI : fonctionnant localement, pas encore intégré au Galaxy AI

Aug 10, 2024 pm 01:59 PM

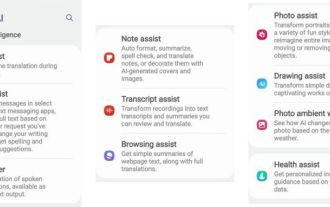

Selon les informations du 10 août, le média technologique Android Authority a publié un article de blog le 8 août indiquant que les Samsung Galaxy Z Fold6 et Galaxy Z Flip 6 sont devenus les premiers téléphones pliables à prendre en charge l'exécution locale du modèle Gemini Nano AI. Il n'a pas encore été intégré à Galaxy AI. Selon des rapports citant des sources, les modèles Galaxy AI et Gemini Nano AI sont à ce stade deux systèmes indépendants. Même les fonctions basées sur le texte (telles que l'assistance par chat) ne sont pas encore intégrées. , aide aux notes, aide à l'enregistrement de texte ou aide à la navigation) ) ni l'un ni l'autre. Ce test multimédia peut exécuter GalaxyAI localement sans télécharger le modèle GeminiNano : Samsun