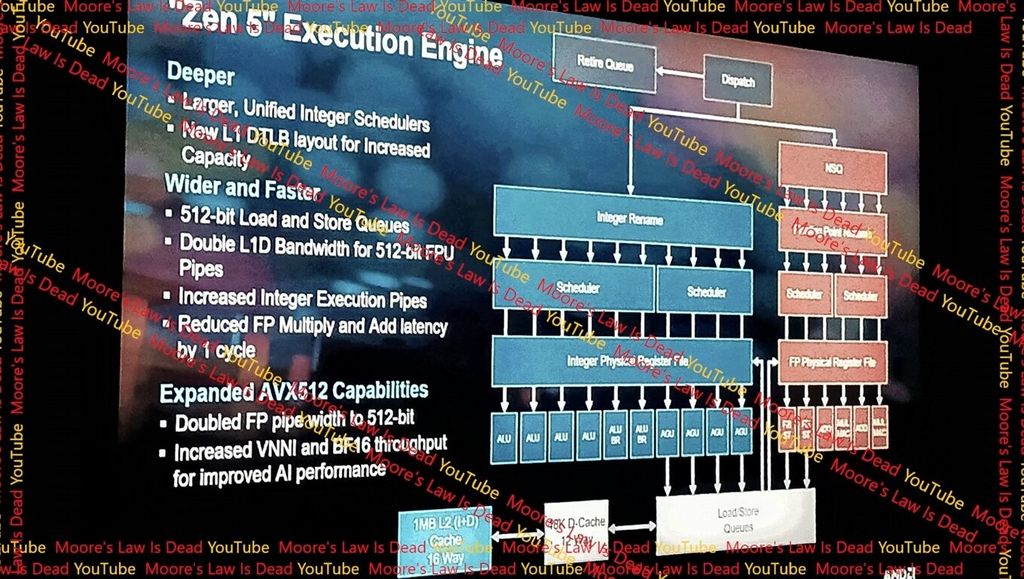

Nouvelles de ce site le 5 avril. Dans la dernière vidéo, la source Moore's Law is Dead a partagé des informations sur le moteur d'exécution du processeur AMD Zen 5 (Execution Engine), affirmant qu'il utilisera une véritable unité de calcul à virgule flottante de 512 bits (FPU ).

Selon les diapositives partagées par la source, le moteur d'exécution de Zen 5 est décrit en détail, utilisant un véritable FPU de 512 bits.

Le processeur AMD Zen 4 utilise un FPU double canal de 256 bits lors de l'exécution de la charge de travail d'instructions AVX-512, tandis que Zen 5 utilise un véritable FPU de 512 bits pour traiter les instructions AVX ou VNNI de 512 bits. Il y aura des performances plus élevées.

Ce site a également appris des rapports selon lesquels AMD a mis à niveau les composants associés pour le FPU 512 bits, augmenté la capacité du DTLB L1, étendu la file d'attente de stockage de chargement, doublé la bande passante du cache de données L1 et augmenté la taille de 50. %. La taille de L1D est passée de 32 Ko dans "Zen 4" à 48 Ko désormais.

Latence FPU MADD réduite de 1 cycle. En plus du FPU, AMD a augmenté le nombre de canaux d'exécution Integer de 8 (Zen 4) à 10, et la taille du cache L2 exclusif reste de 1 Mo par cœur.

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!