.2 HOST主桥(2)

3 使用Outbound寄存器访问PCI总线地址空间 MPC8548处理器使用Outbound寄存器组访问PCI总线地址空间的步骤如下。 (1) 首先MPC8548处理器需要将程序使用的32位有效地址EA (Effective Address)转换为41位的虚拟地址VA (Virtual Address)。E500 V2内核不能关闭MM

3 使用Outbound寄存器访问PCI总线地址空间

MPC8548处理器使用Outbound寄存器组访问PCI总线地址空间的步骤如下。

(1) 首先MPC8548处理器需要将程序使用的32位有效地址EA (Effective Address)转换为41位的虚拟地址VA (Virtual Address)。E500 V2内核不能关闭MMU(Memory Management Unit),因此不能直接访问物理地址。

(2) MPC8548处理器通过MMU将41位的虚拟地址转换为36位的物理地址。在E500 V2内核中,物理地址是36位(缺省是32位,需要使能)。

(3) 检查LAWBAR和LAWAR寄存器,判断当前36位的物理地址是否属于PCI总线空间。在MPC8548中定义了一组LAWBAR和LAWAR寄存器对,每一对寄存器描述当前物理空间是与PCI总线、PCIe总线、DDR还是RapidIO空间对应。该组寄存器的详细说明见MPC8548 PowerQUICC III? Integrated Host Processor Family Reference Manual。如果CPU访问的空间为PCI总线空间,则执行第(4)步,否则处理器将不会访问PCI地址空间。

(4) 判断当前36位物理地址是否在POWBARn寄存器1~4描述的窗口中,如果在则将36位的处理器物理地址通过寄存器POTARn和POTEARn转换为64位的PCI总线地址,然后HOST主桥将来自处理器的读写请求发送到PCI总线上;如果不在POWBARn寄存器1~4描述的窗口中,POWBAR0寄存器作为缺省窗口,接管这个存储器访问,并使用寄存器POTAR0和POTEAR0,将处理器物理地址转换为PCI总线地址,当然在正常设计中很少出现这种情况。

许多系统软件,将Outbound窗口两边的寄存器使用“直接相等”的方法进行映射,将存储器域的地址与PCI总线地址设为相同的值。但是系统软件程序员务必注意这个存储器地址与PCI总线地址是分属于存储器域与PCI总线域的,这两个值虽然相等,但是所代表的地址并不相同,一个属于存储器域,而另一个属于PCI总线域。

2.2.3 PCI总线域地址空间到存储器域地址空间的转换

MPC8548处理器使用Inbound寄存器组将PCI总线域地址转换为存储器域的地址。PCI设备进行DMA读写时,只有访问的地址在Inbound窗口中时,HOST主桥才能接收这些读写请求,并将其转发到存储器控制器。MPC8548处理器提供了3组Inbound寄存器,即提供3个Inbound寄存器窗口,实现PCI总线地址到存储器地址的反向映射。

从PCI设备的角度上看,PCI设备访问存储器域的地址空间时,首先需要通过Inbound窗口将PCI总线地址转换为存储器域的地址;而从处理器的角度上看,处理器必须要将存储器地址通过Inbound寄存器组反向映射为PCI总线地址空间,才能被PCI设备访问。

PCI设备只能使用PCI总线地址访问PCI总线域的地址空间。HOST主桥将这段地址空间通过Inbound窗口转换为存储器域的地址之后,PCI设备才能访问存储器域地址空间。这个地址转换过程如图2?5所示。

在介绍MPC8548处理器如何使用Inbound寄存器组进行PCI总线域地址空间到存储器域地址空间的转换之前,我们首先简要介绍Inbound寄存器组中的相应寄存器。该组寄存器的地址偏移、属性和复位值如表2?3所示。

表2?3 PCI/X ATMU Inbound寄存器组

|

Offset |

寄存器名 |

属性 |

复位值 |

|

0x0_8DA0/C0/E0 |

PITARn |

可读写 |

0x0000-0000 |

|

0x0_8DA8/C8/E8 |

PIWBARn |

可读写 |

0x0000-0000 |

|

0x0_8DAC/CC |

PIWBEARn |

可读写 |

0x0000-0000 |

|

0x0_8DB0/D0/F0 |

PIWARn |

可读写 |

0x0000-0000 |

值得注意的是,Inbound寄存器组除了可以进行PCI总线地址空间到存储器域地址空间的转换之外,还可以转换分属不同PCI总线域的地址空间,以支持PCI总线的Peer-to-Peer数据传送方式。

1 PITARn寄存器

PITARn寄存器保存当前Inbound窗口在存储器域中的36位地址空间的基地址,其地址窗口的大小至少为4KB,因此在该寄存器中仅存放存储器域地址的第0~23位,该寄存器的其主要字段如下所示。

- TEA字段存放存储器地址空间的第0~3位。

- TA字段存放存储器地址空间的第4~23位。

2 PIWBARn和PIWBEARn寄存器

- PIWBARn和PIWBEARn寄存器保存当前Inbound窗口在PCI总线域中的64位地址空间的基地址的第63~12位,Inbound窗口使用的最小地址空间为4KB,因此在这两个寄存器中不含有PCI总线地址空间的第11~0位。这两个寄存器的主要字段如下所示。

- PIWBARn寄存器的BEA字段存放PCI总线地址空间的第43~32位。

- PIWBARn寄存器的BA字段存放PCI总线地址空间的第31~12位。

- PIWBEARn寄存器的BEA字段存放PCI总线地址空间的第63~44位。

3 PIWARn寄存器

PIWARn寄存器描述当前Inbound窗口的属性,该寄存器由以下位和字段组成。

- EN位,第0位。该位是Inbound窗口的使能位,为1表示当前Inbound寄存器组描述的存储器地址空间到PCI总线地址空间的映射关系有效;为0表示无效。

- PF位,第2位。该位为1表示当前Inbound窗口描述的存储区域支持预读;为0表示不支持预读。

- TGI字段,第8~11位。该字段为0b0010表示当前Inbound窗口描述的存储区域属于PCIe总线域地址空间;为0b1100表示当前Inbound窗口描述的存储区域属于RapidIO总线域地址空间。该字段对于OCeaN实现不同域间的报文转发非常重要,如果当前Inbound窗口的TGI字段为0b0010,此时PCI总线上的设备可以使用该Inbound窗口,通过OCeaN直接读取PCIe总线的地址空间,而不需要经过SoC平台总线。如果TGI字段为0b1111表示Inbound窗口描述的存储器区域属于主存储器地址空间,这也是最常用的方式。使用该字段可以实现HOST主桥的Peer-to-Peer数据传送方式。

- RTT字段和WTT字段,分别为该寄存器的第12~15位和第16~19位。Inbound窗口的RTT/WTT字段的含义与Outbound窗口的RTT/WTT字段基本类似。只是在Inbound窗口中可以规定PCI设备访问主存储器时,是否需要进行Cache一致性操作(Cache Lock and Allocate),在进行DMA写操作时,数据是否可以直接进入到Cache中。该字段是PowerPC处理器对PCI总线规范的有效补充,由于该字段的存在,PowerPC处理器的PCI设备可以将数据直接写入Cache,也可以视情况决定DMA操作是否需要进行Cache共享一致性操作。

- IWS字段,第26~31位。该字段描述当前窗口的大小,Inbound窗口的大小在4KB~16GB之间,其值为2IWS+1。

4 使用Inbound寄存器组进行DMA操作

PCI设备使用DMA操作访问主存储器空间,或者访问其他PCI总线域地址空间时,需要通过Inbound窗口,其步骤如下。

(1) PCI设备在访问主存储器空间时,将首先检查当前PCI总线地址是否在PIWBARn和PIWBEARn寄存器描述的窗口中。如果在这个窗口中,则将这个PCI总线地址通过PITARn寄存器转换为存储器域的地址或者其他PCI总线域的地址;如果不在将禁止本次访问。

(2) 如果PCI设备访问的是存储器地址空间,HOST主桥将来自PCI总线的读写请求发送到存储器空间,进行存储器读写操作,并根据Inbound寄存器组的RTT/WTT位决定是否需要进行Cache一致性操作,或者将数据直接写入到Cache中。

结合Outbound寄存器组,可以发现PCI总线地址空间与存储器地址空间是有一定联系的。如果存储器域地址空间被Inbound寄存器组反向映射到PCI空间,这个存储器地址具有两个地址,一个是在存储器域的地址,一个是在PCI总线域的地址;同理PCI总线空间的地址如果使用Outbound寄存器映射到寄存器地址空间,这个PCI总线地址也具有两个地址,一个是在PCI总线域的地址,一个是在存储器域的地址。

能够被处理器和PCI总线同时访问的地址空间,一定在PCI总线域和存储器域中都存在地址映射。再次强调,绝大多数操作系统将同一个空间的PCI总线域地址和存储器地址设为相同的值,但是这两个相同的值所代表的含义不同。

由此可以看出,如果MPC8548处理器的某段存储器区域没有在Inbound窗口中定义时,PCI设备将不能使用DMA机制访问这段存储器空间;同理如果PCI设备的空间不在Outbound窗口,HOST处理器也不能访问这段PCI地址空间。

在绝大多数PowerPC处理器系统中,PCI设备地址空间都在HOST主桥的Outbound窗口中建立了映射;而MPC8548处理器可以选择将哪些主存储器空间共享给PCI设备,从而对主存储器空间进行保护。

2.2.4 x86处理器的HOST主桥

x86处理器使用南北桥结构连接CPU和PCI设备。其中北桥(North Bridge)连接快速设备,如显卡、和内存条,并推出PCI总线,HOST主桥包含在北桥中。而南桥(South Bridge)连接慢速设备。x86处理器使用的南北桥结构如图2?6所示。

Intel使用南北桥概念统一PC架构。但是从体系结构的角度上看,南北桥架构并不重要,北桥中存放的主要部件不过是存储器控制器、显卡控制器和HOST主桥而已,而南桥存放的是一些慢速设备,如ISA总线和中断控制器等。

不同的处理器系统集成这些组成部件的方式并不相同,如PowerPC、MIPS和ARM处理器系统通常将CPU和主要外部设备都集成到一颗芯片中,组成一颗基于SoC架构的处理器系统。这些集成方式并不重要,每一个处理器系统都有其针对的应用领域,不同应用领域的需求对处理器系统的集成方式有较大的影响。Intel采用的南北桥架构针对x86处理器的应用领域而设计,并不能说采用这种结构一定比MPC8548处理器中即含有HOST-to-PCI主桥也含有HOST-to-PCIe主桥更为合理。

在许多嵌入式处理器系统中,即含有PCI设备也含有PCIe设备,为此MPC8548处理器同时提供了PCI总线和PCIe总线接口,在这个处理器系统中,PCI设备可以与PCI总线直接相连,而PCIe设备可以与PCIe总线直接相连,因此并不需要使用PCIe桥扩展PCI总线,从而在一定程度上简化了嵌入式系统的设计。

嵌入式系统所面对的应用千姿百态,进行芯片设计时所要考虑的因素相对较多,因而在某种程度上为设计带来了一些难度。而x86处理器系统所面对的应用领域针对个人PC**务器,向前兼容和通用性显得更加重要。在多数情况下,一个通用处理器系统的设计难过专用处理器系统的设计,Intel为此付出了极大的代价。

在一些相对较老的北桥中,如Intel 440系列芯片组中包含了HOST主桥,从系统软件的角度上看HOST-to-PCI主桥实现的功能与HOST-to-PCIe主桥实现的功能相近。本节仅简单介绍Intel的HOST-to-PCI主桥如何产生PCI的配置周期,有关Intel HOST-to-PCIe主桥[9]的详细信息参见第5章。

x86处理器定义了两个I/O端口寄存器,分别为CONFIG_ADDRESS和CONFIG_DATA寄存器,其地址为0xCF8和0xCFC。x86处理器使用这两个I/O端口访问PCI设备的配置空间。PCI总线规范也以这个两个寄存器为例,说明处理器如何访问PCI设备的配置空间。其中CONFIG_ADDRESS寄存器存放PCI设备的ID号,而CONFIG_DATA寄存器存放进行配置读写的数据。

CONFIG_ADDRESS寄存器与PowerPC处理器中的CFG_ADDR寄存器的使用方法类似,而CONFIG_DATA寄存器与PowerPC处理器中的CFG_DATA寄存器的使用方法类似。CONFIG_ADDRESS寄存器的结构如图2?7所示。

CONFIG_ADDRESS寄存器的各个字段和位的说明如下所示,

- Enable位,第31位。该位为1时,对CONFIG_DATA寄存器进行读写时将引发PCI总线的配置周期。

- Bus Number字段,第23~16位,记录PCI设备的总线号。

- Device Number字段,第15~11位,记录PCI设备的设备号。

- Function Number字段,第10~8位,记录PCI设备的功能号。

- Register Number字段,第7~2位,记录PCI设备的寄存器号。

当x86处理器对CONFIG_DATA寄存器进行I/O读写访问,且CONFIG_ADDR寄存器的Enable位为1时,HOST主桥将这个I/O读写访问转换为PCI配置读写总线事务,然后发送到PCI总线上,PCI总线根据保存在CONFIG_ADDR寄存器中的ID号,将PCI配置读写请求发送到指定PCI设备的指定配置寄存器中。

x86处理器使用小端地址模式,因此从CONFIG_DATA寄存器中读出的数据不需要进行模式转换,这点和PowerPC处理器不同,此外x86处理器的HOST主桥也实现了存储器域到PCI总线域的地址转换,但是这个概念在x86处理器中并不明晰。

本书将在第5章以HOST-to-PCIe主桥为例,详细介绍Intel处理器的存储器地址与PCI总线地址的转换关系,而在本节不对x86处理器的HOST主桥做进一步说明。x86处理器系统的升级速度较快,目前在x86的处理器体系结构中,已很难发现HOST主桥的身影。

目前Intel对南北桥架构进行了升级,其中北桥被升级为MCH(Memory Controller Hub),而南桥被升级为ICH(I/O Controller Hub)。x86处理器系统在MCH中集成了存储器控制器、显卡芯片和HOST-to-PCIe主桥,并通过Hub Link与ICH相连;而在ICH中集成了一些相对低速总线接口,如AC’97、LPC(Low Pin Count)、IDE和USB总线,当然也包括一些低带宽的PCIe总线接口。

在Intel最新的Nehelem[10]处理器系统中,MCH被一份为二,存储器控制器和图形控制器已经与CPU内核集成在一个Die中,而MCH剩余的部分与ICH合并成为PCH(Peripheral Controller Hub)。但是从体系结构的角度上看,这些升级与整合并不重要。

目前Intel在Menlow[11]平台基础上,计划推出基于SoC架构的x86处理器,以进军手持设备市场。在基于SoC构架的x86处理器中将逐渐淡化Chipset的概念,其拓扑结构与典型的SoC处理器,如ARM和PowerPC处理器,较为类似。

[8]WBA字段并没有保存存储器域的第24~35位地址,因为Outbound窗口大小至少为4KB。

[9]这个HOST-to-PCIe主桥也是RC(Root Complex)的一部分。

[10] Nehelem处理器也被称为Core i7处理器。

[11] Menlow平台于2008年3月发布,其目标应用为MID(Mobile Internet Device)设备。Menlow平台基于低功耗处理器内核Atom。

ホットAIツール

Undresser.AI Undress

リアルなヌード写真を作成する AI 搭載アプリ

AI Clothes Remover

写真から衣服を削除するオンライン AI ツール。

Undress AI Tool

脱衣画像を無料で

Clothoff.io

AI衣類リムーバー

Video Face Swap

完全無料の AI 顔交換ツールを使用して、あらゆるビデオの顔を簡単に交換できます。

人気の記事

ホットツール

メモ帳++7.3.1

使いやすく無料のコードエディター

SublimeText3 中国語版

中国語版、とても使いやすい

ゼンドスタジオ 13.0.1

強力な PHP 統合開発環境

ドリームウィーバー CS6

ビジュアル Web 開発ツール

SublimeText3 Mac版

神レベルのコード編集ソフト(SublimeText3)

ホットトピック

7716

7716

15

15

1641

1641

14

14

1396

1396

52

52

1289

1289

25

25

1232

1232

29

29

マグネットリンクの使い方

Feb 18, 2024 am 10:02 AM

マグネットリンクの使い方

Feb 18, 2024 am 10:02 AM

マグネット リンクは、リソースをダウンロードするためのリンク方法であり、従来のダウンロード方法よりも便利で効率的です。マグネット リンクを使用すると、中間サーバーに依存せずに、ピアツーピア方式でリソースをダウンロードできます。この記事ではマグネットリンクの使い方と注意点を紹介します。 1. マグネット リンクとは? マグネット リンクは、P2P (Peer-to-Peer) プロトコルに基づくダウンロード方式です。ユーザーはマグネット リンクを通じてリソースの発行者に直接接続し、リソースの共有とダウンロードを完了できます。従来のダウンロード方法と比較して、磁気

Windows 11 シャットダウン プロンプト タスク ホスト ウィンドウ タスク ホストがシャットダウン タスク ソリューションを実行しています

Feb 12, 2024 pm 12:40 PM

Windows 11 シャットダウン プロンプト タスク ホスト ウィンドウ タスク ホストがシャットダウン タスク ソリューションを実行しています

Feb 12, 2024 pm 12:40 PM

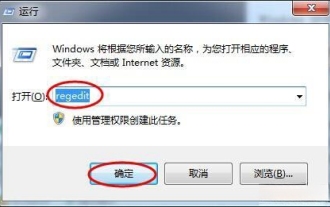

最近、多くの Win11 ユーザーが、シャットダウン時に、taskhostwindow タスク ホストがシャットダウン タスクを実行しているというメッセージが表示されると報告しています。ユーザーは、ローカル レジストリ エディターの下のデスクトップ フォルダーに入り、右側のウィンドウで AutoEndTasks を選択して設定できます。このサイトは、シャットダウン時にこの問題の解決策をユーザーに丁寧に紹介します。 Windows 11 のシャットダウンでは、taskhostwindow タスク ホストがシャットダウン タスクを実行していることを示すメッセージが表示されます。 解決策 1. 次の図に示すように、win キー + r キーの組み合わせを使用し、「regedit」と入力して Enter キーを押します。 2. [HKEY]を検索します

mdfおよびmdsファイルの使用方法

Feb 19, 2024 pm 05:36 PM

mdfおよびmdsファイルの使用方法

Feb 19, 2024 pm 05:36 PM

mdf ファイルと mds ファイルの使用方法 コンピューター技術の継続的な進歩により、さまざまな方法でデータを保存および共有できるようになりました。デジタル メディアの分野では、特殊なファイル形式に遭遇することがよくあります。この記事では、一般的なファイル形式である mdf および mds ファイルについて説明し、その使用方法を紹介します。まず、mdf ファイルと mds ファイルの意味を理解する必要があります。 mdf は CD/DVD イメージ ファイルの拡張子で、mds ファイルは mdf ファイルのメタデータ ファイルです。

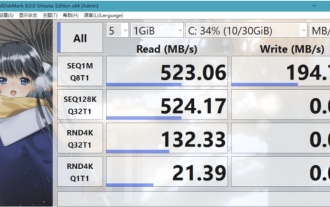

CrystalDiskmarkとはどのようなソフトウェアですか? -crystaldiskmarkの使い方は?

Mar 18, 2024 pm 02:58 PM

CrystalDiskmarkとはどのようなソフトウェアですか? -crystaldiskmarkの使い方は?

Mar 18, 2024 pm 02:58 PM

CrystalDiskMark は、シーケンシャルおよびランダムの読み取り/書き込み速度を迅速に測定する、ハード ドライブ用の小型 HDD ベンチマーク ツールです。次に、編集者が CrystalDiskMark と Crystaldiskmark の使用方法を紹介します。 1. CrystalDiskMark の概要 CrystalDiskMark は、機械式ハード ドライブとソリッド ステート ドライブ (SSD) の読み取りおよび書き込み速度とパフォーマンスを評価するために広く使用されているディスク パフォーマンス テスト ツールです。 ). ランダム I/O パフォーマンス。これは無料の Windows アプリケーションで、使いやすいインターフェイスとハード ドライブのパフォーマンスのさまざまな側面を評価するためのさまざまなテスト モードを提供し、ハードウェアのレビューで広く使用されています。

foobar2000のダウンロード方法は? -foobar2000の使い方

Mar 18, 2024 am 10:58 AM

foobar2000のダウンロード方法は? -foobar2000の使い方

Mar 18, 2024 am 10:58 AM

foobar2000 は、音楽リソースをいつでも聴くことができるソフトウェアです。あらゆる種類の音楽をロスレス音質で提供します。音楽プレーヤーの強化版により、より包括的で快適な音楽体験を得ることができます。その設計コンセプトは、高度なオーディオをコンピュータ上で再生可能 デバイスを携帯電話に移植し、より便利で効率的な音楽再生体験を提供 シンプルでわかりやすく、使いやすいインターフェースデザイン 過度な装飾や煩雑な操作を排除したミニマルなデザインスタイルを採用また、さまざまなスキンとテーマをサポートし、自分の好みに合わせて設定をカスタマイズし、複数のオーディオ形式の再生をサポートする専用の音楽プレーヤーを作成します。過度の音量による聴覚障害を避けるために、自分の聴覚の状態に合わせて調整してください。次は私がお手伝いさせてください

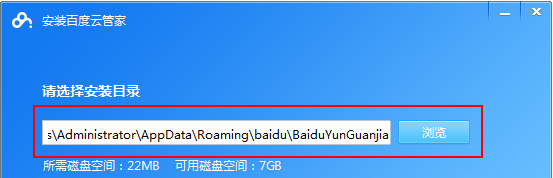

Baidu Netdisk アプリの使用方法

Mar 27, 2024 pm 06:46 PM

Baidu Netdisk アプリの使用方法

Mar 27, 2024 pm 06:46 PM

クラウド ストレージは今日、私たちの日常生活や仕事に欠かせない部分になっています。中国有数のクラウド ストレージ サービスの 1 つである Baidu Netdisk は、強力なストレージ機能、効率的な伝送速度、便利な操作体験により多くのユーザーの支持を得ています。また、重要なファイルのバックアップ、情報の共有、オンラインでのビデオの視聴、または音楽の聴きたい場合でも、Baidu Cloud Disk はニーズを満たすことができます。しかし、Baidu Netdisk アプリの具体的な使用方法を理解していないユーザーも多いため、このチュートリアルでは Baidu Netdisk アプリの使用方法を詳しく紹介します。まだ混乱しているユーザーは、この記事に従って詳細を学ぶことができます。 Baidu Cloud Network Disk の使用方法: 1. インストール まず、Baidu Cloud ソフトウェアをダウンロードしてインストールするときに、カスタム インストール オプションを選択してください。

NetEase メールボックス マスターの使用方法

Mar 27, 2024 pm 05:32 PM

NetEase メールボックス マスターの使用方法

Mar 27, 2024 pm 05:32 PM

NetEase Mailbox は、中国のネットユーザーに広く使用されている電子メール アドレスとして、その安定した効率的なサービスで常にユーザーの信頼を獲得してきました。 NetEase Mailbox Master は、携帯電話ユーザー向けに特別に作成された電子メール ソフトウェアで、電子メールの送受信プロセスが大幅に簡素化され、電子メールの処理がより便利になります。 NetEase Mailbox Master の使い方と具体的な機能について、以下ではこのサイトの編集者が詳しく紹介しますので、お役に立てれば幸いです。まず、モバイル アプリ ストアで NetEase Mailbox Master アプリを検索してダウンロードします。 App Store または Baidu Mobile Assistant で「NetEase Mailbox Master」を検索し、画面の指示に従ってインストールします。ダウンロードとインストールが完了したら、NetEase の電子メール アカウントを開いてログインします。ログイン インターフェイスは次のとおりです。

PIP ミラー ソースの簡単なガイド: 使い方を簡単にマスターする

Jan 16, 2024 am 10:18 AM

PIP ミラー ソースの簡単なガイド: 使い方を簡単にマスターする

Jan 16, 2024 am 10:18 AM

簡単に始めましょう: pip ミラー ソースの使用方法 世界中での Python の人気により、pip は Python パッケージ管理の標準ツールになりました。ただし、pip を使用してパッケージをインストールするときに多くの開発者が直面する一般的な問題は速度の遅さです。これは、デフォルトでは、pip は Python 公式ソースまたはその他の外部ソースからパッケージをダウンロードしますが、これらのソースが海外のサーバーに配置されている可能性があるため、ダウンロード速度が遅くなることがあります。ダウンロード速度を向上させるために、pip ミラー ソースを使用できます。ピップミラーソースとは何ですか?簡単に言えば、ただ、