キャッシュとは何ですか?

キャッシュとはキャッシュメモリと呼ばれるもので、中央処理装置とメインメモリの間にある高速かつ小容量のメモリで、一般的には高速なSRAMで構成されますが、この種のローカルメモリは、 CPU とメモリの速度差によるシステム パフォーマンスへの影響を軽減または排除するために導入されました。キャッシュ容量は小さいですが高速、メモリ速度は遅いですが容量は大きく、スケジューリングアルゴリズムを最適化することでシステムのパフォーマンスが大幅に向上します。

このチュートリアルの動作環境: Windows 7 システム、Dell G3 コンピューター。

キャッシュとは何ですか?

キャッシュ メモリ: コンピュータ内の CPU およびメイン メモリ DRAM (Dynamic Random Access Memory) にあるキャッシュ メモリ。 )、小さいながらも非常に高速なメモリで、通常は SRAM(スタティック ランダム アクセス メモリ)で構成されます。

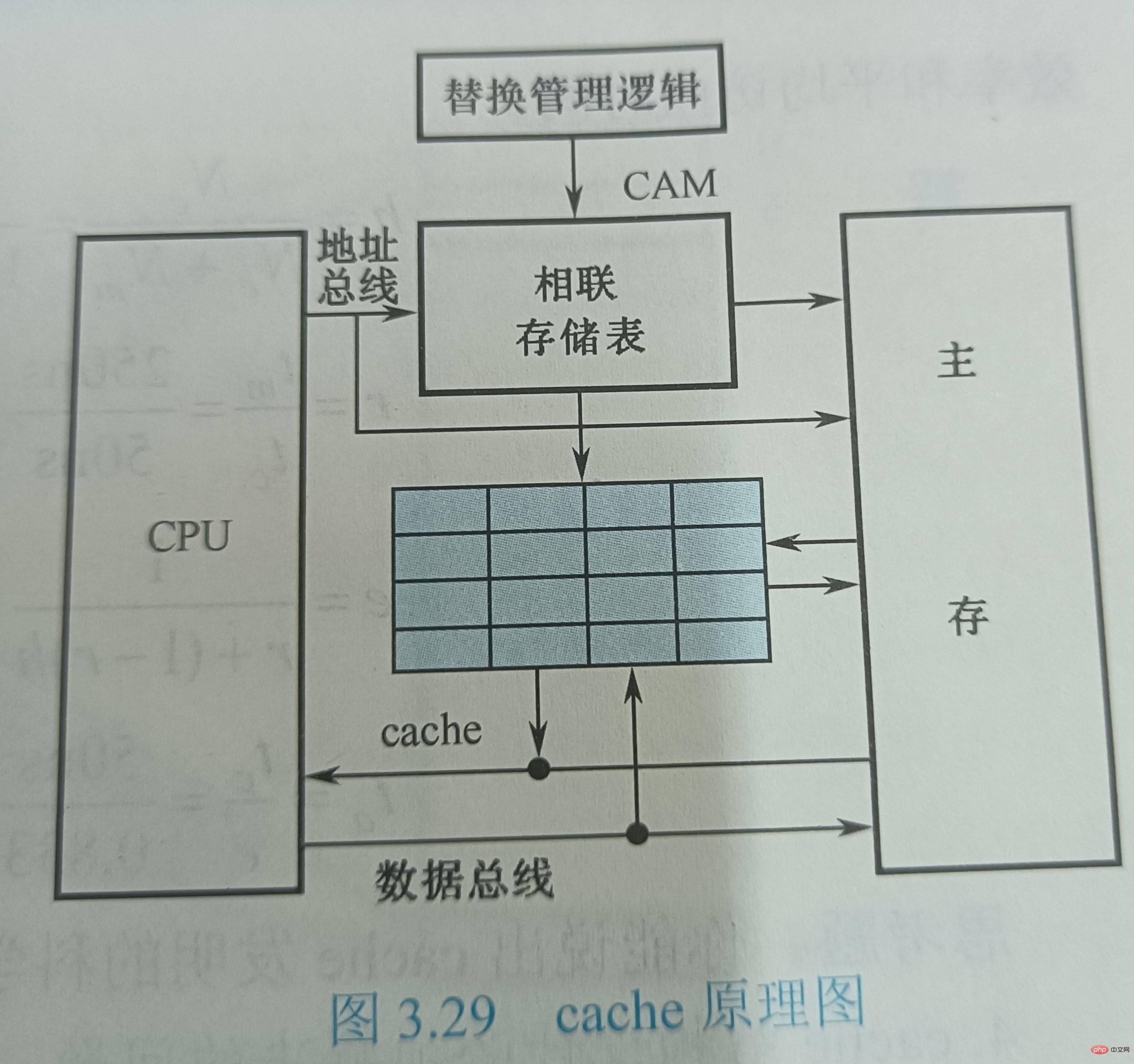

図 3.28 に示すように、キャッシュは CPU とメインメモリ M2 の間にある小容量のメモリですが、アクセス速度はメインメモリやメモリ M2 よりも高速です。容量はメインメモリよりもはるかに小さいです。キャッシュは命令とデータを CPU に高速に提供できるため、プログラムの実行が高速化されます。機能的にはメインメモリのバッファメモリであり、高速SRAMで構成されています。高速性を追求するため、管理を含むすべての機能がハードウェアに実装されているため、プログラマにとって透過的です。

現在、半導体デバイスの集積化が進み、小容量のキャッシュとCPUを同一チップに集積することが可能となり、その動作速度はCPUの速度に近くなり、 2 レベル以上のキャッシュ システム。

キャッシュの機能

キャッシュの機能は、CPU データの入出力速度を高めることです。キャッシュ容量は小さいが高速、メモリ速度は低いが容量は大きい、スケジューリング アルゴリズムを最適化することで、あたかもストレージ システムの容量がメモリと同等で、アクセス速度が同等であるかのように、システムのパフォーマンスが大幅に向上します。キャッシュ。

CPU の速度はメモリの速度よりもはるかに高速です。CPU がメモリからデータに直接アクセスする場合、一定時間待機する必要がありますが、キャッシュはデータの一部を保存できます。 CPU が使用したばかりまたはリサイクルしたデータ。CPU が再度データにアクセスする必要がある場合、データのこの部分を使用するときにキャッシュから直接呼び出すことができるため、データへの繰り返しアクセスが回避され、CPU の待機時間が短縮されます。したがって、システムの効率が向上します。キャッシュは L1Cache (レベル 1 キャッシュ) と L2Cache (レベル 2 キャッシュ) に分けられ、L1Cache は主に CPU 内に統合され、L2Cache はマザーボードまたは CPU 上に統合されます。

キャッシュの基本原理

SRAM に加えて、キャッシュには制御ロジックもあります。キャッシュが CPU チップの外部にある場合、その制御ロジックは通常、メイン メモリ/チェイス コントローラーと呼ばれるメイン メモリ制御ロジックと組み合わされます。キャッシュが CPU 内部にある場合、CPU がその制御ロジックを提供します。

CPUとキャッシュ間のデータ交換はワード単位ですが、キャッシュとメインメモリ間のデータ交換はブロック単位です。ブロックは複数のワードで構成され、固定長です。 CPU がメモリ内のワードを読み取ると、そのワードのメモリ アドレスがキャッシュとメイン メモリに送信されます。このとき、キャッシュ制御ロジックは、アドレスに基づいてワードが現在キャッシュにあるかどうかを判断します。キャッシュにあれば、キャッシュがヒットし、ワードはすぐに CPU に転送されます。そうでない場合は、キャッシュが欠落しています (ミス)。メイン メモリ読み取りサイクルは、メイン メモリからワードを読み取るために使用され、その読み取り結果は CPU に送信され、同時にこのワードを含むデータ ブロック全体がメイン メモリから読み取られてキャッシュに送信されます。

キャッシュ ヒット率

CPU の観点から見ると、キャッシュを増やす目的は、メイン メモリの平均読み取り時間を増やすことです。パフォーマンス キャッシュ読み取り時間に可能な限り近い値。この目標を達成するには、すべてのメモリ アクセスのうち、CPU のニーズを満たすためにキャッシュによって満たされる部分が高い割合を占める必要があります。つまり、キャッシュ ヒット率が 1 に近い必要があります。この目標の達成は、プログラム アクセスの局所性により可能です。 プログラム実行時、総キャッシュアクセス数をNc、メインメモリアクセス総数をNₘ、ヒット率をhとすると、 h=Nc/(Nc+Nₘ) ヒット時のキャッシュアクセス時間をtc、ミス時のメインメモリアクセス時間をtₘ、ミス率(欠落率)を1-hとすると、平均アクセス時間tₐはキャッシュ/メイン メモリ システムはです

tₐ=htc+(1−h)tₘ

私たちが追求する目標は、キャッシュ/メイン メモリ システムの平均アクセス時間 tₐ を、少ないハードウェア コストでできるだけ tc に近づけることです。メインメモリとキャッシュ間のアクセス時間の比率を r=tₘ/tc、アクセス効率を e とすると、

e=tc/ta=tc/(htc+(1−h)tm)=1/(h+(1−h)r)=1/(r+(1−r)h)

この式から、アクセス効率を向上させるためには、命中率 h は 1 になるほど良くなります。適切な r 値は 5 ~ 10 であり、大きすぎないようにする必要があります。

ヒット率 h は、プログラムの動作、キャッシュ容量、編成方法、ブロック サイズに関係します。

#キャッシュ構造設計で解決すべき問題

キャッシュの基本的な動作原理から、キャッシュの設計に必要なことがわかります。 1 つは、キャッシュ ヒット率ができるだけ高いことを期待し、実際には 1 に近い値であることを期待すること、もう 1 つは、キャッシュが CPU に対して透過的であることを期待することです。キャッシュがある場合でも、CPU によるメモリへのアクセス方法は同じであり、ソフトウェアで何も追加する必要はなく、コマンドでキャッシュにアクセスできます。ヒット率や透過性の問題は解決され、CPUのメモリアクセスの観点からはメインメモリに匹敵する容量とキャッシュに近い速度のメモリとなります。このためには、制御機能を完成させるために特定のハードウェア回路、つまりキャッシュ コントローラを追加する必要があります。 キャッシュ構造を設計する際には、次のいくつかの問題を解決する必要があります: ① メインメモリの内容をキャッシュに転送するときに、どのように格納するか? ② メモリにアクセスするときに、キャッシュ内の情報をどのように検索するか? ③ キャッシュ容量が不足した場合のキャッシュの置き換え方法 すでに存在するコンテンツをキャッシュアドレスに変換します。キャッシュ容量は主記憶容量に比べて非常に小さく、保存される内容は主記憶内容の一部に過ぎず、キャッシュと主記憶間のデータ交換はブロック単位で行われます。メイン メモリ ブロックをキャッシュに配置するには、アドレス マッピングと呼ばれる、キャッシュ内のメイン メモリ アドレスを特定する何らかの方法を使用する必要があります。 「マッピング」という言葉の物理的な意味は、位置間の対応関係を決定し、それをハードウェアで実装することです。このように、CPU がメモリにアクセスすると、CPU から与えられたワードのメモリアドレスが自動的にキャッシュアドレスに変換されます。つまり、キャッシュアドレス変換です。 キャッシュ置換問題は主に、キャッシュがミスした場合にキャッシュ内の内容を置換する置換アルゴリズムを選択して実行することです。最後の質問は、更新中にメイン メモリとキャッシュの間の一貫性を維持することに焦点を当てた、キャッシュの書き込み操作戦略に関するものです。 さらに関連する知識については、FAQ

列をご覧ください。以上がキャッシュとは何ですか?の詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。

ホットAIツール

Undresser.AI Undress

リアルなヌード写真を作成する AI 搭載アプリ

AI Clothes Remover

写真から衣服を削除するオンライン AI ツール。

Undress AI Tool

脱衣画像を無料で

Clothoff.io

AI衣類リムーバー

AI Hentai Generator

AIヘンタイを無料で生成します。

人気の記事

ホットツール

メモ帳++7.3.1

使いやすく無料のコードエディター

SublimeText3 中国語版

中国語版、とても使いやすい

ゼンドスタジオ 13.0.1

強力な PHP 統合開発環境

ドリームウィーバー CS6

ビジュアル Web 開発ツール

SublimeText3 Mac版

神レベルのコード編集ソフト(SublimeText3)

ホットトピック

7486

7486

15

15

1377

1377

52

52

77

77

11

11

19

19

38

38

アクセス速度が最も速いメモリはどれですか?

Jul 26, 2022 am 10:54 AM

アクセス速度が最も速いメモリはどれですか?

Jul 26, 2022 am 10:54 AM

アクセスが最も速いメモリは「内部メモリ」で、コンピュータのメモリは速度の速い順に内部メモリ、キャッシュメモリ、コンピュータのメインメモリ、大容量ディスクなどの階層構造をとっており、一般的には次のように分けられます。 RAM ランダム アクセス メモリと ROM 読み取り専用メモリ。

入社してキャッシュとは何かを理解した

Jul 31, 2023 pm 04:03 PM

入社してキャッシュとは何かを理解した

Jul 31, 2023 pm 04:03 PM

実際は次のようなものです。当時、私のリーダーは私に perf ハードウェア パフォーマンス監視タスクを与えました。perf を使用するプロセス中に、コマンド perf list を入力すると、次の情報が表示されました。私のタスクは、これらのキャッシュ イベントを有効にすることです。しかし重要なのは、これらのミスやロードが何を意味するのか全く分からないということです。

CPUは内部メモリのデータに直接アクセスできますか?

Nov 25, 2022 pm 02:02 PM

CPUは内部メモリのデータに直接アクセスできますか?

Nov 25, 2022 pm 02:02 PM

直接アクセスできます。内部メモリはメモリとも呼ばれ、外部メモリと CPU の間のブリッジであり、コンピュータ内のすべてのプログラムはメモリ内で実行されます。メモリの役割は、CPU内の計算データやハードディスクなどの外部メモリとやり取りされるデータを一時的に保存することです。コンピュータが動作している限り、オペレーティング システムは計算に必要なデータをメモリから CPU に転送して計算し、計算が完了すると CPU は結果を送信します。パソコンの安定した動作。

コンピューターが強力な記憶能力を備えている根拠は何でしょうか?

Jul 09, 2021 pm 03:59 PM

コンピューターが強力な記憶能力を備えている根拠は何でしょうか?

Jul 09, 2021 pm 03:59 PM

コンピュータが強力なメモリ機能を備えるための基礎となるのは、十分な容量を持つストレージ デバイスです。メモリは内部メモリと外部メモリに分けられ、コンピュータが強力な記憶機能を持ち、さまざまなデータ情報だけでなく、それらのデータを処理するためのプログラムなどの情報を大量に保存することができます。

コンピュータシステムのメモリシステムとは何ですか?

Jul 22, 2022 pm 02:23 PM

コンピュータシステムのメモリシステムとは何ですか?

Jul 22, 2022 pm 02:23 PM

メモリシステムとは、プログラムやデータを格納する各種記憶装置、制御コンポーネント、情報のスケジューリングを管理する装置(ハードウェア)やアルゴリズム(ソフトウェア)から構成されるコンピュータ内のシステムを指します。ストレージシステムは、コンピュータの作業に必要な情報(プログラムやデータ)の書き込みと読み出しの機能を提供し、コンピュータの情報記憶機能を実現します。ストレージ システムの階層構造は、レジスタ グループ、キャッシュ キャッシュ、メイン メモリ、仮想メモリ、外部メモリの 5 つのレベルに分けることができます。

USBフラッシュドライブを発明した国はどこですか?

Oct 09, 2022 pm 02:26 PM

USBフラッシュドライブを発明した国はどこですか?

Oct 09, 2022 pm 02:26 PM

USB フラッシュ ドライブは中国で発明され、Netac は USB フラッシュ ドライブの世界的な発明者です。 2002 年 7 月、Netac の「データ処理システム用の高速ライトニング外部ストレージ方式およびデバイス」が国家知識産権局から正式に認可され、この特許は中国のコンピュータ ストレージ分野における発明特許の 20 年間の空白を埋めました。 2019年12月7日、Netacは米国特許庁より正式に認定されたフラッシュディスクの基本発明特許を取得しました。

キャッシュを使用するとコンピュータの速度が向上するのはなぜですか?

Dec 09, 2020 am 11:28 AM

キャッシュを使用するとコンピュータの速度が向上するのはなぜですか?

Dec 09, 2020 am 11:28 AM

キャッシュを使用すると、CPU の待ち時間が短縮されるため、コンピューターの速度が向上します。キャッシュは、CPU とメイン メモリ DRAM の間に位置する小さいながらも高速なメモリです。キャッシュの機能はCPUのデータ入出力速度を高めることであり、キャッシュは容量は小さいが速度が速く、メモリは速度は低いが容量が大きいため、スケジューリングアルゴリズムを最適化することでシステムのパフォーマンスを向上させることができます。大幅に改善されました。

キャッシュとは何ですか?

Nov 25, 2022 am 11:48 AM

キャッシュとは何ですか?

Nov 25, 2022 am 11:48 AM

キャッシュはキャッシュメモリと呼ばれ、中央処理装置とメインメモリの間にある高速かつ小容量のメモリで、通常は高速SRAMで構成され、CPU向けのこの種のローカルメモリが導入されています。 CPU とメモリ間の速度差がシステム パフォーマンスに及ぼす影響を軽減または排除します。キャッシュ容量は小さいですが高速、メモリ速度は遅いですが容量は大きく、スケジューリングアルゴリズムを最適化することでシステムのパフォーマンスが大幅に向上します。