VSCode で Verilog 環境を構成するにはどうすればよいですか?コードプロンプト + 自動インスタンス化 + フォーマットプラグインの共有

VSCodeVerilog 環境を構成するにはどうすればよいですか?次の記事では、VSCode で Verilog をスムーズに記述するための、コード プロンプト、自動インスタンス化、およびフォーマットを実現できる 3 つのプラグインを推奨しています。

[推奨学習: vscode チュートリアル 、プログラミング ビデオ ]

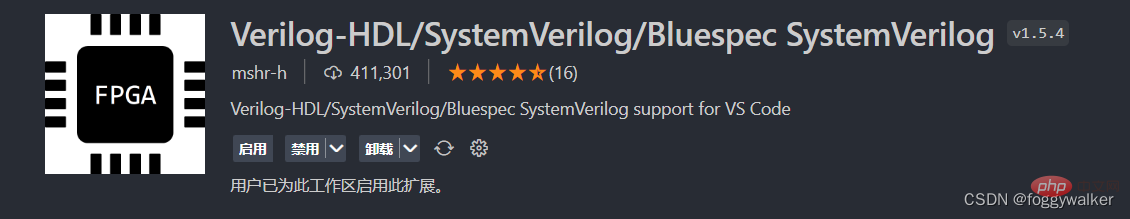

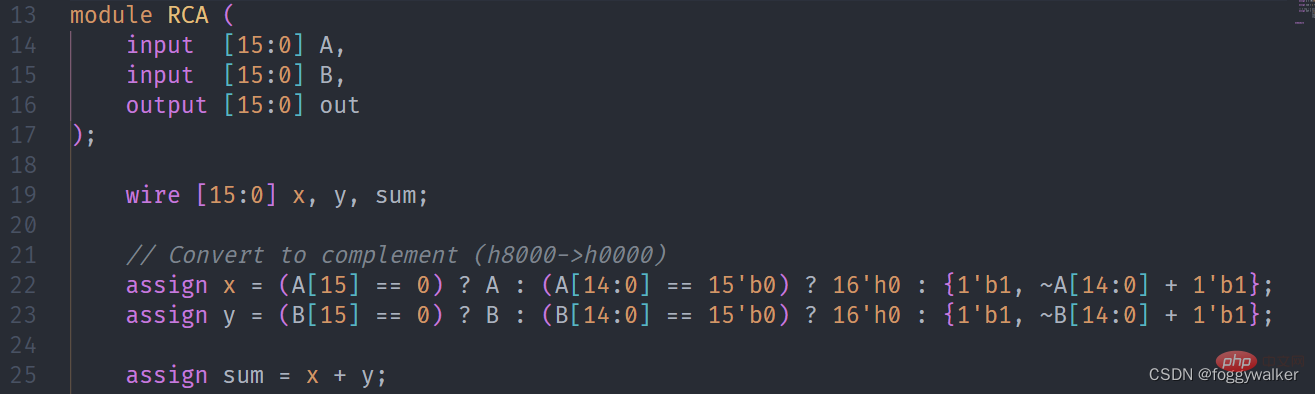

Verilog-HDL/ SystemVerilog/Bluespec SystemVerilog

#実現可能な機能:

- 構文の強調表示

- 自動インスタンス化

- コード プロンプトとジャンプ

- 自動補完

プラグイン設定

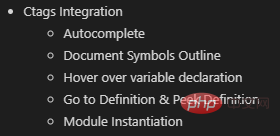

Verilog HDL/SystemVerilog プラグインのウェルカム ページで説明されているように、Ctags 機能をサポートします:

- 最新バージョンをダウンロード

- 置き換えますctags.exe システム環境変数へのパスを設定します;

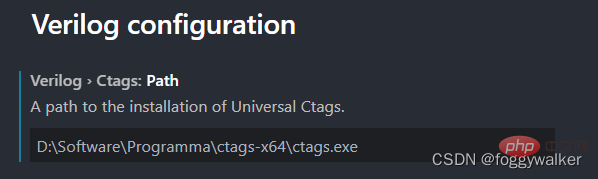

- プラグイン設定で ctags パスを構成します;

- VSCode を再起動するだけです;

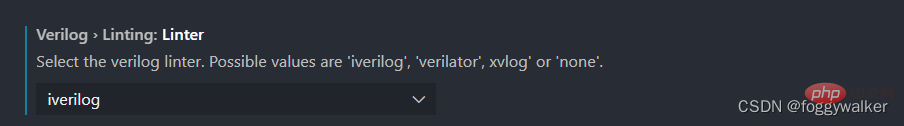

iverilog

- xvlog(vivado)

- modelsim

Verilog、SV、およびその他の構文の強調表示をサポートします。

shift ctrl p input verilog を使用すると、モジュールを直接自動的にインスタンス化できます。

マウスを信号上に置くと、フローティング ボックスにステートメントが表示されます。 Ctrl キーを押しながら信号名をクリックすると、宣言に自動的にジャンプします。信号にカーソルを置き、右クリックして [定義の表示] を選択します (ショートカット キーは自分でバインドできます)。ここで宣言のコードを展開できます。前後にジャンプすることなく宣言を変更するのに非常に便利です。 。

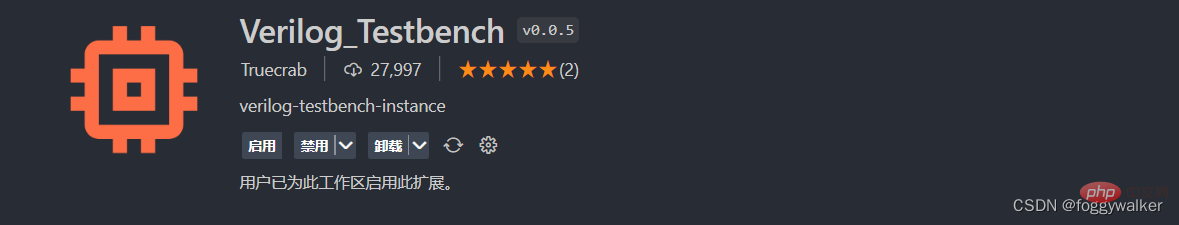

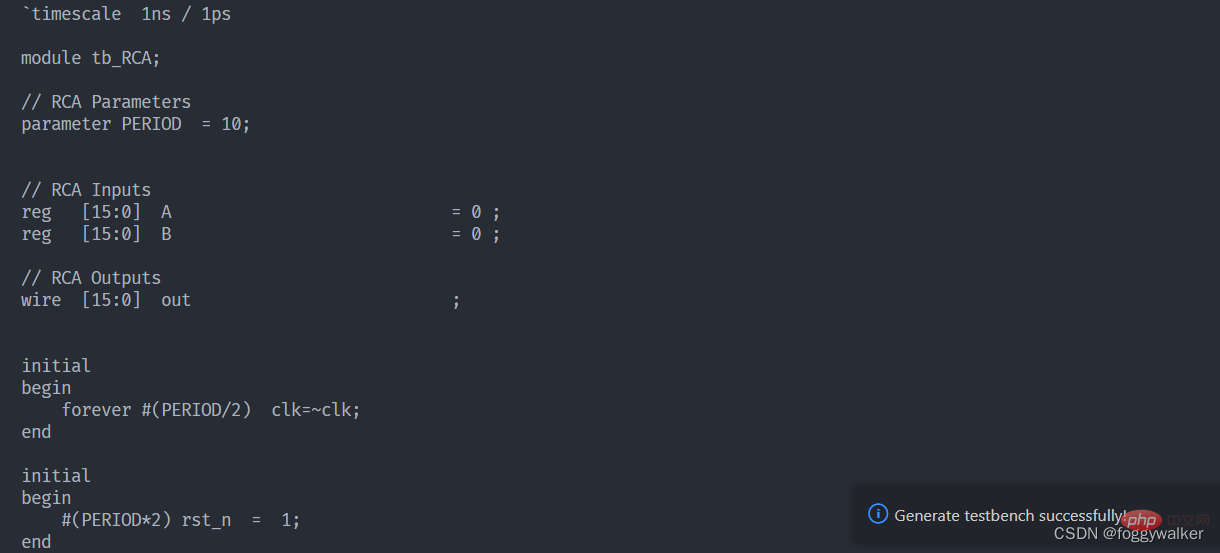

Verilog_Testbench

##実現可能な機能:

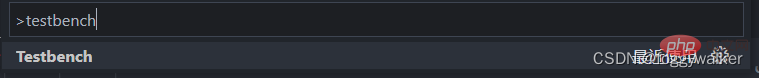

テストベンチを自動的に生成

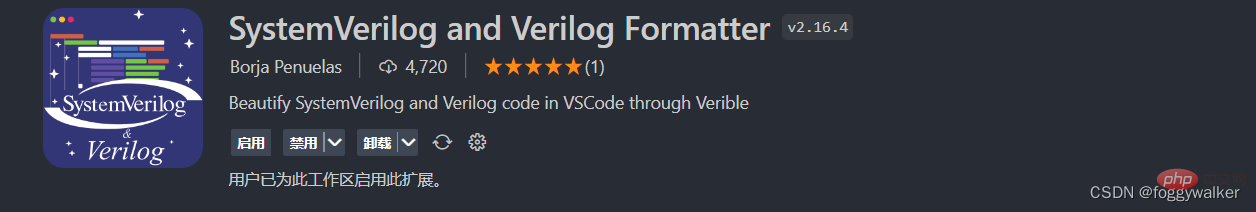

SystemVerilog と Verilog Formatter

このツールは Google によって開発され、Verilog と System Verilog の両方をサポートします。 ,

効果は非常に優れています。また、幅広いカスタマイズされた書式設定パラメータもサポートしています。個人的にはverilog形式よりも使いやすいと思います。

#実現可能な機能

#実現可能な機能

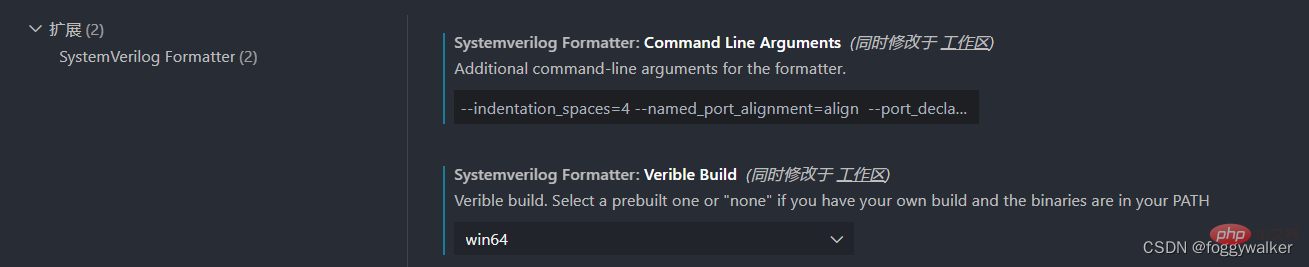

ファイルの自動フォーマット#選択したコンテンツの自動フォーマット#カスタムフォーマット

- #カスタム パラメータ設定テーブル

- ##verible-verilog-format: 使用法: bazel-bin/verilog/tools/formatter /verible-verilog-format [オプション]

[ ]

common/formatting/basic_format_style_init.cc からのフラグ:

--column_limit (書式設定時に維持するターゲット行の長さ制限。);

デフォルト: 100;

--indentation_spaces (インデントレベルごとに追加されます)この数のスペース。);

デフォルト: 2;

--line_break_penalty (導入された行

Break ごとにソリューションにペナルティが追加されます。);デフォルト: 2;

--over_column_limit_penalty (ペナルティを最小限に抑えるため、これは列制限を超えた場合の

ベースライン ペナルティ値を表します。この制限を超える文字ごとに追加のペナルティ

1 が発生します);デフォルト: 100;

--wrap_spaces (ラップ レベルごとにこの数のスペースが追加されます。これは、オープングループ セクションの後の

最初の要素がラップされる場合に適用されます。それ以外の場合は、

インデント レベルが列に設定されますオープングループ

演算子の位置);デフォルト: 4;

external/com_google_absl/absl/flags/parse.cc からのフラグ:

--flagfile (フラグをロードするファイルのカンマ区切りリスト);デフォルト: ;

--fromenv (環境から設定するフラグのカンマ区切りのリスト [use

'export FLAGS_flag1=value']);デフォルト: ;

--tryfromenv (

環境が存在する場合、その環境から設定を試行するフラグのカンマ区切りのリスト);デフォルト: ;

--undefok (プログラムでその

名前のフラグが定義されていない場合でも、コマンドラインで

指定しても問題ないフラグ名のコンマ区切りのリスト);デフォルト: ;###

verilog/formatting/format_style_init.cc からのフラグ:

--assignment_statement_alignment (さまざまな割り当てのフォーマット:

{align,flush-left,preserve,infer});デフォルト: infer;

--case_items_alignment (ケース項目のフォーマット:

{align,flush-left,preserve,infer});デフォルト: infer;

--class_member_variable_alignment (クラスメンバー変数のフォーマット:

{align,flush-left,preserve,infer});デフォルト: infer;

--compact_indexing_and_selections (

インデックス付け/ビット選択演算子内でコンパクトなバイナリ式を使用します);デフォルト: true;

--distribution_items_alignment (配布アイテムを揃える:

{align,flush-left,preserve,infer});デフォルト: infer;

--enum_assignment_statement_alignment (列挙型で割り当てをフォーマットする:

{align,flush-left,preserve,infer});デフォルト: infer;

--expand_coverpoints (true の場合、常にカバーポイントを展開します。);デフォルト: false;

--formal_parameters_alignment (形式パラメータ:

{align,flush-left,preserve,infer});デフォルト: infer;

--formal_parameters_indentation (仮パラメータのインデント: {indent,wrap});

デフォルト: Wrap;

--module_net_variable_alignment (ネット/変数宣言のフォーマット:

{align,flush-左、保存、推測});デフォルト: infer;

--named_parameter_alignment (形式名付き実際のパラメータ:

{align,flush-left,preserve,infer});デフォルト: infer;

--named_parameter_indentation (名前付きパラメータ割り当てのインデント:

{indent,wrap});デフォルト: Wrap;

--named_port_alignment (名前付きポート接続の形式:

{align,flush-left,preserve,infer});デフォルト: infer;

--named_port_indentation (名前付きポート接続のインデント: {indent,wrap});

デフォルト: Wrap;

--port_declarations_alignment (ポート宣言のフォーマット:

{align,flush-left 、保存、推測});デフォルト: infer;

--port_declarations_indentation (ポート宣言のインデント: {indent,wrap});

デフォルト: Wrap;

--port_declarations_right_align_packed_dimensions (true の場合、アライメントが有効になっているコンテキスト内のパック

ディメンションは右揃え。);

デフォルト: false;

--port_declarations_right_align_unpacked_dimensions (true の場合、配置が有効になっているコンテキスト内の unpacked

ディメンションは右揃えになります。);

デフォルト: false;

--struct_union_members_alignment (構造体/共用体メンバーの形式:

{align,flush-left,preserve,infer});デフォルト: infer;

--try_wrap_long_lines (true の場合、フォーマッタは行の最適化を試みます。

折り返しが必要な場合は折り返しの決定を行い、それ以外の場合は書式設定されないままにします。

これはリスクを軽減するための短期的な対策です。有害です。);デフォルト: false;

verilog/parser/verilog_parser.cc からのフラグ:

--verilog_trace_parser (トレース verilog パーサー);デフォルト: false;

verilog/tools/formatter/verilog_format.cc からのフラグ:

--failsafe_success (true の場合、

入力エラーまたは内部エラーがあった場合でも、常に 0 ステータスで終了します。すべてのエラーでこの条件では、元の

テキストは常に保持されます。これは、

フェールセーフ動作が成功とみなされる必要があるサービスを展開する場合に役立ちます。);デフォルト: true;

--inplace (true の場合、成功した場合に入力ファイルを上書きします。);

デフォルト: false;

--lines (フォーマットする特定の行、1 ベース、カンマ区切り) 、N-M

範囲を含み、N は N-N の略です。デフォルトでは、指定しないままにすると、すべての行が

書式設定可能になります。(反復可能、累積));デフォルト: ;

--max_search_states (行

ラップの最適化中に調査される検索状態の数を制限します。);デフォルト: 100000;

--show_equally_optimal_wrappings (true の場合、複数の最適な

ソリューション (stderr) が見つかったときに出力しますが、通常どおり動作し続けます。);

デフォルト: false;

--show_inter_token_info ( true の場合、show_token_partition_tree とともに、

スペースやブレーク ペナルティなどのトークン間情報が含まれます。);

デフォルト: false;

--show_largest_token_partitions (> 0 の場合、トークンのパーティション分割を出力し、

出力をフォーマットせずに終了します。);デフォルト: 0;

--show_token_partition_tree (true の場合、token

パーティショニング後に診断を出力し、出力をフォーマットせずに終了します。);デフォルト: false;

--stdin_name (「-」を使用して標準入力から読み取る場合、診断目的で代替の

名前が与えられます。それ以外の場合、これは無視されます。);

デフォルト: "

--verbose (より冗長になります。);デフォルト: false;

--verify_convergence (true で、

--lines による増分フォーマットではない場合、フォーマットされた出力を再フォーマットしてもそれ以上の変更が生じないこと、つまりフォーマットが収束していることを検証します。);デフォルト: true;

に指定された部分文字列が含まれる

フラグのヘルプが表示されます。 path.

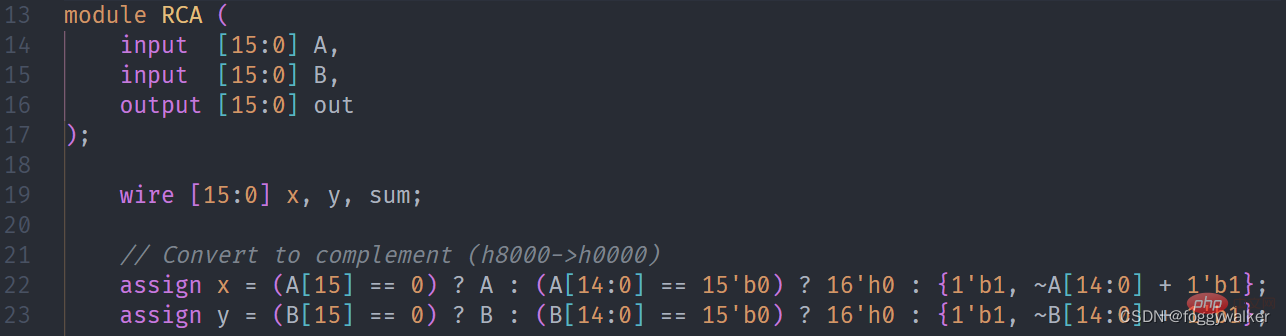

ファイル構成

# と vscode 内置形式化、直接 shift ctrl f でファイルを形式化できます、ctrl k で指定した内容を形式化できます。 ## このソフトウェアも完全に動作しているため、部分的に問題が存在することに注意してください。 そうしないと動作しません。 、または会話法を認識できない場合、形式化は使用されません。ここでは最後のポートを追加します。","就は形式化できません。

詳細VSCode の関連知識、访藮: vscode ベース教程

vscode ベース教程

以上がVSCode で Verilog 環境を構成するにはどうすればよいですか?コードプロンプト + 自動インスタンス化 + フォーマットプラグインの共有の詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。

ホットAIツール

Undresser.AI Undress

リアルなヌード写真を作成する AI 搭載アプリ

AI Clothes Remover

写真から衣服を削除するオンライン AI ツール。

Undress AI Tool

脱衣画像を無料で

Clothoff.io

AI衣類リムーバー

AI Hentai Generator

AIヘンタイを無料で生成します。

人気の記事

ホットツール

メモ帳++7.3.1

使いやすく無料のコードエディター

SublimeText3 中国語版

中国語版、とても使いやすい

ゼンドスタジオ 13.0.1

強力な PHP 統合開発環境

ドリームウィーバー CS6

ビジュアル Web 開発ツール

SublimeText3 Mac版

神レベルのコード編集ソフト(SublimeText3)

ホットトピック

7564

7564

15

15

1386

1386

52

52

86

86

11

11

28

28

99

99

VSCODEに必要なコンピューター構成

Apr 15, 2025 pm 09:48 PM

VSCODEに必要なコンピューター構成

Apr 15, 2025 pm 09:48 PM

VSコードシステムの要件:オペレーティングシステム:オペレーティングシステム:Windows 10以降、MACOS 10.12以上、Linux Distributionプロセッサ:最小1.6 GHz、推奨2.0 GHz以上のメモリ:最小512 MB、推奨4 GB以上のストレージスペース:最低250 MB以上:その他の要件を推奨:安定ネットワーク接続、XORG/WAYLAND(Linux)

vscodeのヘッダーファイルを定義する方法

Apr 15, 2025 pm 09:09 PM

vscodeのヘッダーファイルを定義する方法

Apr 15, 2025 pm 09:09 PM

ビジュアルスタジオコードを使用してヘッダーファイルを定義する方法は?ヘッダーファイルを作成し、.hまたは.hpp接尾辞名(クラス、関数、変数など)を使用してヘッダーファイルにシンボルを宣言し、#includeディレクティブを使用してプログラムをコンパイルして、ソースファイルにヘッダーファイルを含めます。ヘッダーファイルが含まれ、宣言された記号が利用可能になります。

vscodeで中国モードを切り替える方法

Apr 15, 2025 pm 11:39 PM

vscodeで中国モードを切り替える方法

Apr 15, 2025 pm 11:39 PM

vs中国モードを切り替えるコード:設定インターフェイスを開き(Windows/Linux:Ctrl、MacOS:CMD、)[エディター:言語]設定を検索します。ドロップダウンメニューで[中国語]を選択します。

vscode setting中国のチュートリアル

Apr 15, 2025 pm 11:45 PM

vscode setting中国のチュートリアル

Apr 15, 2025 pm 11:45 PM

VSコードは、ステップに従うことで完了することができる中国の設定をサポートしています。設定パネルを開き、「ロケール」を検索します。 「locale.language」を「zh-cn」(単純化された中国人)または「zh-tw」(伝統的な中国語)に設定します。設定を保存し、コードを再起動します。設定メニュー、ツールバー、コードプロンプト、およびドキュメントが中国語で表示されます。ファイルタグ形式、エントリの説明、診断プロセス言語など、他の言語設定もカスタマイズできます。

中国語でVSCodeを設定する方法

Apr 15, 2025 pm 09:27 PM

中国語でVSCodeを設定する方法

Apr 15, 2025 pm 09:27 PM

ビジュアルスタジオコードで中国語を設定するには2つの方法があります。1。中国語パッケージをインストールします。 2。構成ファイルの「ロケール」設定を変更します。 Visual Studioコードバージョンが1.17以上であることを確認してください。

vscodeを設定する方法

Apr 15, 2025 pm 10:45 PM

vscodeを設定する方法

Apr 15, 2025 pm 10:45 PM

VSCODEを有効にして設定するには、次の手順に従います。VSCODEをインストールして開始します。テーマ、フォント、スペース、コードフォーマットなどのカスタム設定。拡張機能をインストールして、プラグイン、テーマ、ツールなどの機能を強化します。プロジェクトを作成するか、既存のプロジェクトを開きます。 IntelliSenseを使用して、コードプロンプトと完了を取得します。コードをデバッグして、コードを介してブレークポイントを設定し、変数を確認します。バージョン制御システムを接続して変更を管理し、コードをコミットします。

VSCODE端子の共通コマンド

Apr 15, 2025 pm 10:06 PM

VSCODE端子の共通コマンド

Apr 15, 2025 pm 10:06 PM

VSコード端子の一般的なコマンドには、端子画面のクリア(クリア)、現在のディレクトリファイル(LS)のリスト、現在のワーキングディレクトリ(CD)、現在のワーキングディレクトリパス(PWD)の印刷、新しいディレクトリ(MKDIR)の作成、空のディレクトリ(RMDIR)の削除、新しいファイルの作成(RM)の削除(RM)、COPのコピー(RM)、 (MV)ファイルコンテンツの表示(CAT)ファイルコンテンツを表示してスクロール(より少ない)ファイルコンテンツを表示するだけです(その他)ファイルの最初の数行(ヘッド)を表示する

VSCODE前の次のショートカットキー

Apr 15, 2025 pm 10:51 PM

VSCODE前の次のショートカットキー

Apr 15, 2025 pm 10:51 PM

VSコードワンステップ/次のステップショートカットキー使用法:ワンステップ(後方):Windows/Linux:Ctrl←; macOS:CMD←次のステップ(フォワード):Windows/Linux:Ctrl→; macOS:CMD→