Tesla Dojo スーパーコンピューティング アーキテクチャの詳細が初公開!自動運転は「ばらばら」

人工知能と機械学習モデルに対する需要の高まりに応えるため、テスラはテスラ車に自動運転を教えるための独自の人工知能テクノロジーを開発しました。

最近、テスラは Hot Chips 34 カンファレンスで、Dojo スーパーコンピューティング アーキテクチャに関する多くの詳細を明らかにしました。

本質的に、Dojo は、計算、ネットワーキング、入出力 (I/O) チップから命令セット アーキテクチャまでをカバーする完全なカスタム アーキテクチャから構築された巨大なコンポーザブル スーパーコンピュータです。 (ISA)、電力供給、パッケージング、冷却。これらはすべて、カスタムの特定の機械学習トレーニング アルゴリズムを大規模に実行するために行われます。

Ganesh Venkataramanan は、Tesla の自動運転ハードウェア担当シニア ディレクターであり、Dojo プロジェクトと AMD の CPU 設計チームの責任者です。 Hot Chips 34 カンファレンスで、彼とチップ、システム、ソフトウェア エンジニアのグループは、マシンのアーキテクチャ上の機能の多くを初めて発表しました。

データセンター「サンドイッチ」

一般的に言えば、チップを製造するプロセスは、チップをパッケージ上に配置し、そのパッケージをプリント基板上に配置することです。それからシステムに入り、システムはラックに入ります」とヴェンカタラマナン氏は語った。

しかし、このプロセスには問題があります。データがチップからパッケージに移動し、パッケージの外に移動するたびに、遅延と帯域幅の損失が発生します。

これらの制限を回避するために、Venkataramanan と彼のチームはゼロから始めることにしました。

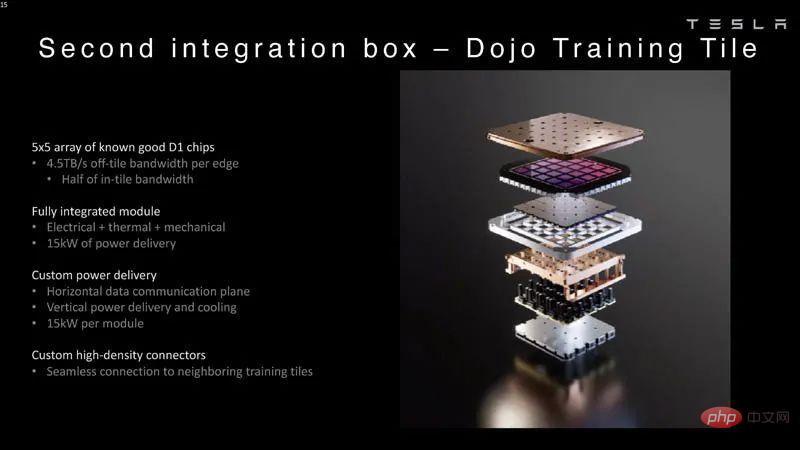

こうして、Dojo のトレーニング タイルが誕生しました。

これは、半分立方フィートを占有し、15kW の水冷パッケージで 556TFLOPS の FP32 パフォーマンスが可能な自己完結型コンピューティング クラスターです。

各タイルには 11 GB の SRAM が搭載されており、スタック全体でカスタム トランスポート プロトコルを使用して 9 TB/秒のファブリック経由で接続されています。

Venkataramanan 氏は次のように述べています。「このトレーニング ボードは、追加のスイッチを必要とせずに、コンピュータからメモリ、電力供給、通信に至るまで、比類のないレベルの統合を実現しています。」

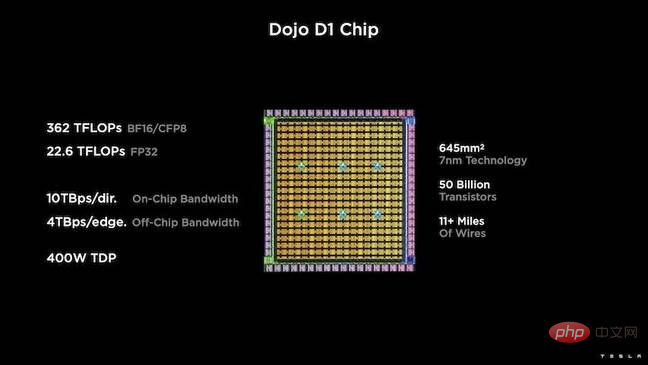

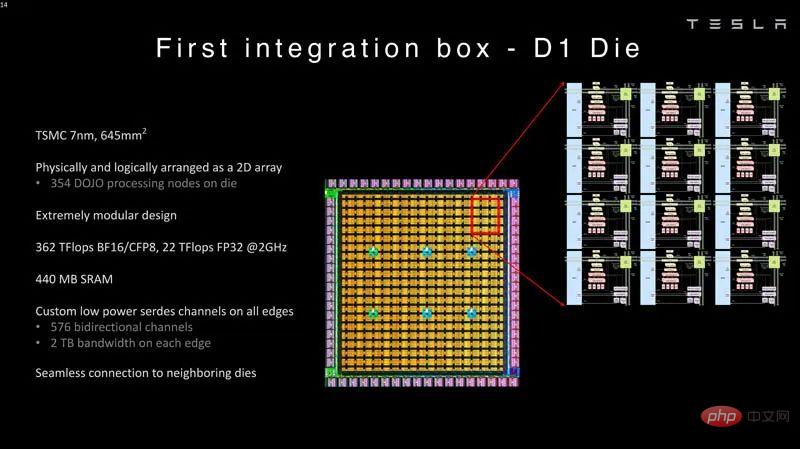

トレーニング タイルのコアは、TSMC の 7nm プロセスに基づく 500 億個のトランジスタ チップである Tesla の D1 です。テスラによれば、各 D1 は 400W の TDP で 22TFLOPS の FP32 パフォーマンスを達成できるという。

テスラは 25 個の D1 を使用し、既知の良好な金型に分割し、TSMC のオンウェーハ システム テクノロジを使用してそれらをまとめて大規模なコンピューティングを可能にしました。非常に低い遅延と非常に高い帯域幅を備えた統合。

ただし、チップ上のシステム設計と垂直スタック アーキテクチャにより、電力供給に課題が生じます。

Venkataramanan 氏によると、現在の加速器のほとんどは電源をシリコン ウェーハのすぐ隣に配置しています。同氏は、このアプローチは効果的ではあるものの、アクセラレータの大部分をこれらのコンポーネント専用に費やす必要があることを意味し、これは Dojo にとって現実的ではないと説明しました。したがって、テスラはチップの底部から直接電力を供給することを選択しました。

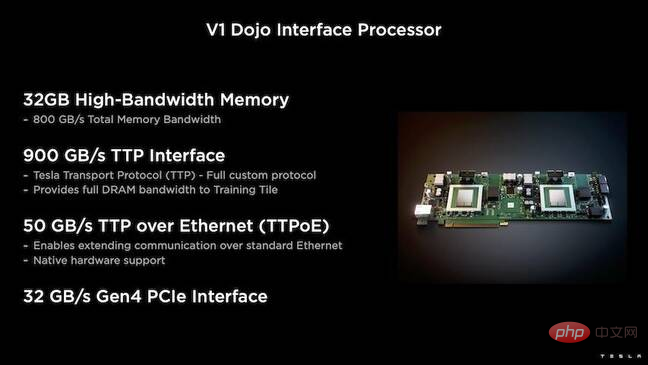

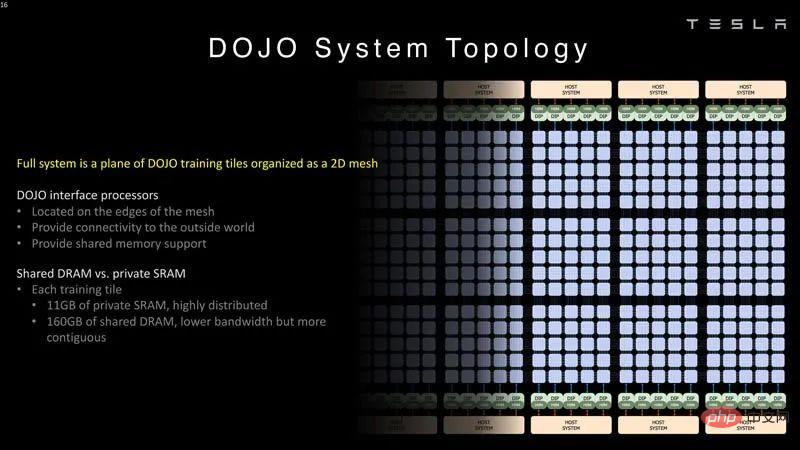

さらに、Tesla は、ホスト CPU とトレーニング プロセッサ間のブリッジとなる Dojo Interface Processor (DIP) も開発しました。

各 DIP には 32 GB の HBM があり、これらのカードのうち最大 5 枚を 900 GB/秒でトレーニング タイルに接続でき、合計 4.5 TB/秒の量になります。各タイルには、合計 160GB HBM。

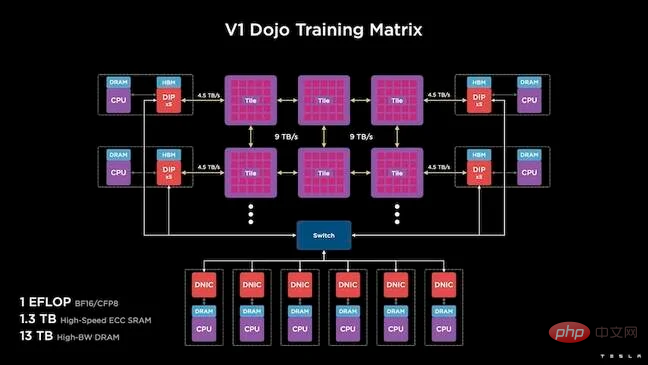

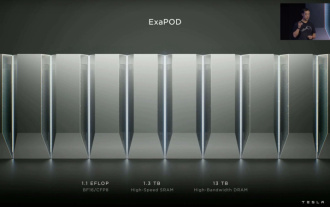

Tesla の V1 構成は、これらのタイル (または 150 個の D1 ダイ) をアレイ内でペアにして、ホスト CPU ごとに 5 つの DIP カードを備えた 4 つのホスト CPU をサポートします。主張されている BF16 または CFP8 のパフォーマンスのエクサフロップを達成します。

ソフトウェア

このような特殊なコンピューティング アーキテクチャには、特殊なソフトウェア スタックが必要です。しかし、Venkataramanan と彼のチームは、プログラマビリティが Dojo の成功か失敗かを決定することを認識していました。

「これらのシステムを設計するとき、ソフトウェア仲間によるプログラムの容易さが最も重要です。研究者は、実行したい新しいアルゴリズムに対応するためにソフトウェア担当者が手書きのカーネルを作成するのを待ちません。」

これを行うために、Tesla はカーネルを使用するという考えを放棄し、コンパイラーを中心に Dojo のアーキテクチャを設計しました。

「私たちが行っているのは、PiTorch を使用することです。中間層を作成して、その下にあるハードウェアを並列化して拡張するのに役立ちます。その下にはすべてコンパイルされたコードがあります。」ソフトウェアを作成するには将来のあらゆるワークロードに適応できるスタックを構築するには、これが唯一の方法です。

Venkataramanan 氏は、ソフトウェアの柔軟性を強調しながらも、現在研究室で実行されているプラットフォームは Tesla に限定されていると指摘しました。

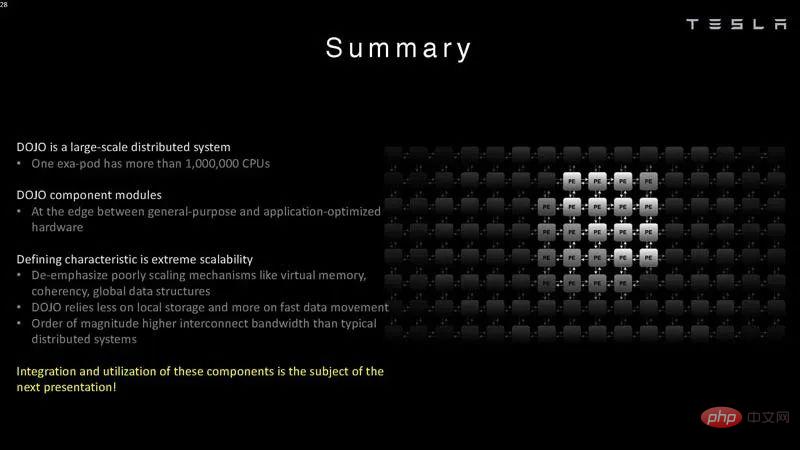

Dojo アーキテクチャの概要

上記を読んだ後、Dojo アーキテクチャを詳しく見てみましょう。

テスラは、機械学習用のエクサスケール人工知能システムを備えています。テスラには従業員を雇用し、テスラの車載システムと同様に自社アプリケーション専用のチップやシステムを構築するのに十分な資本がある。

テスラは、独自の AI チップだけでなく、スーパーコンピューターも開発しています。

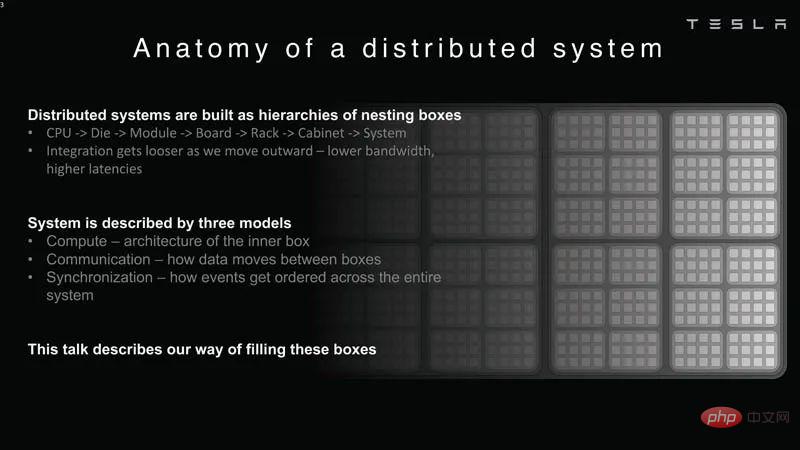

#分散システム分析

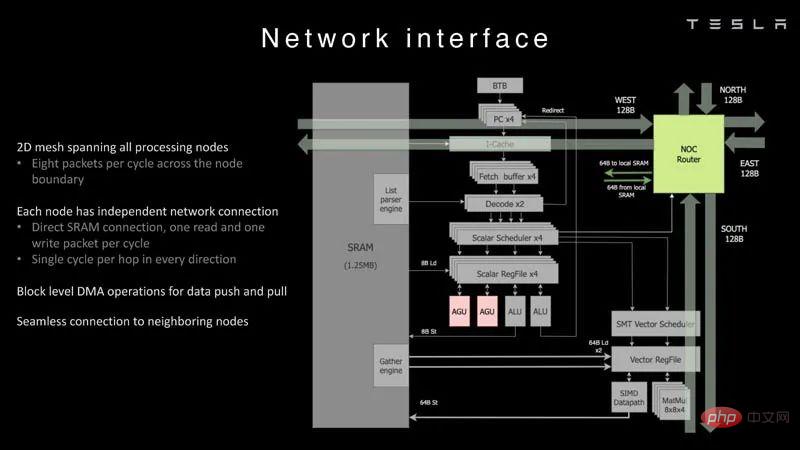

Dojo の各ノードには独自の CPU があり、メモリと通信インターフェイス。

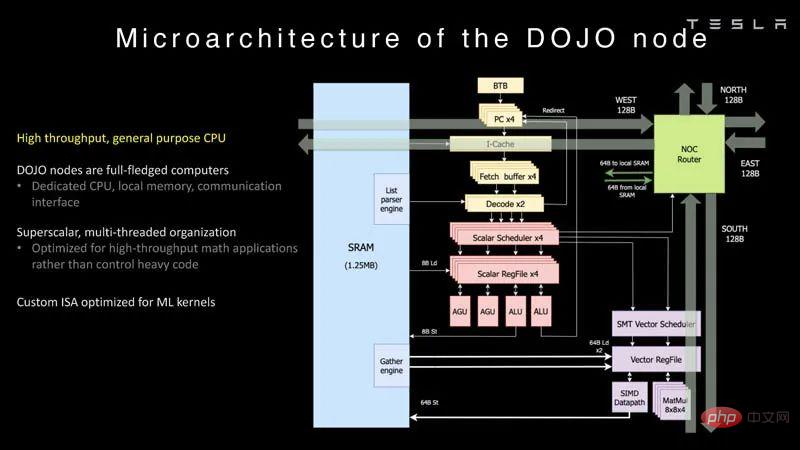

#Dojo ノード

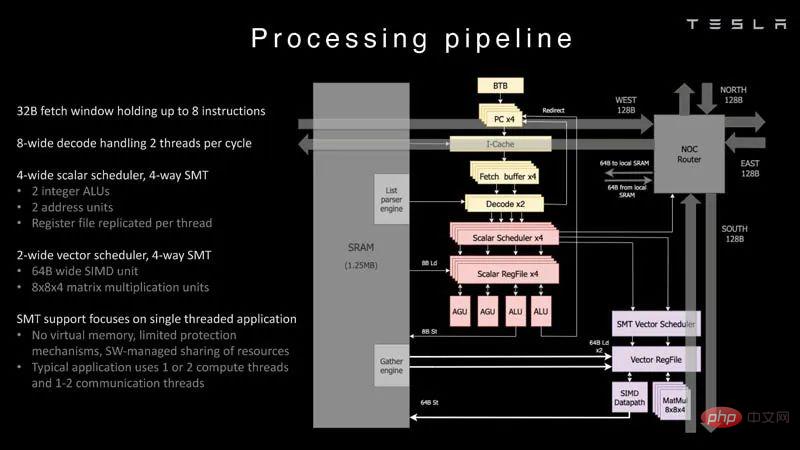

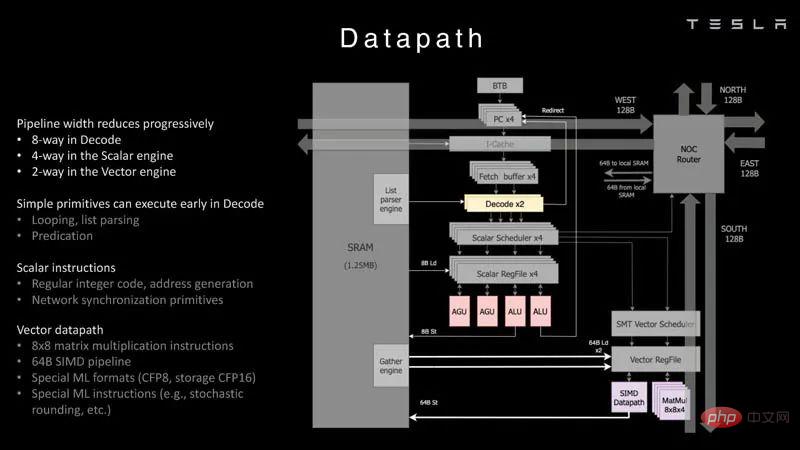

これは、Dojo プロセッサーの処理パイプラインです。 。

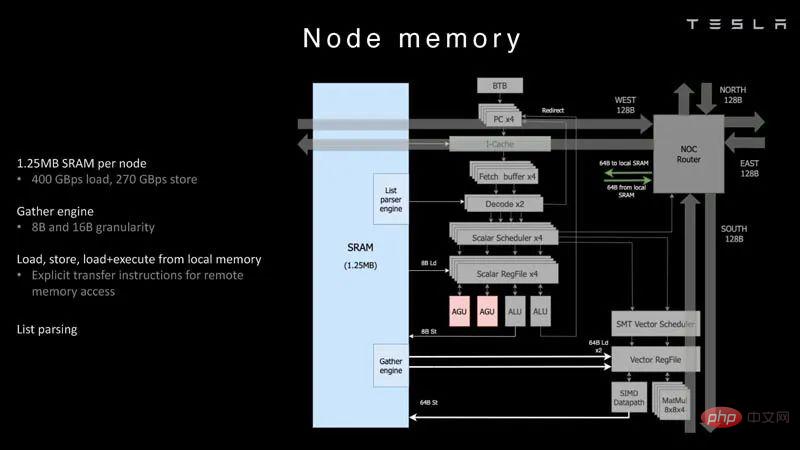

各ノードには 1.25MB の SRAM があります。 AI トレーニングおよび推論チップにおける一般的な手法は、メモリと計算を同じ場所に配置してデータ転送を最小限に抑えることですが、これは電力とパフォーマンスの観点から非常に高価です。

#ノード メモリ

#ノード メモリ

次に、各ノードが 2D グリッドに接続されます。 。

#ネットワーク インターフェイス

これは、データ パスの概要です。

データ パス

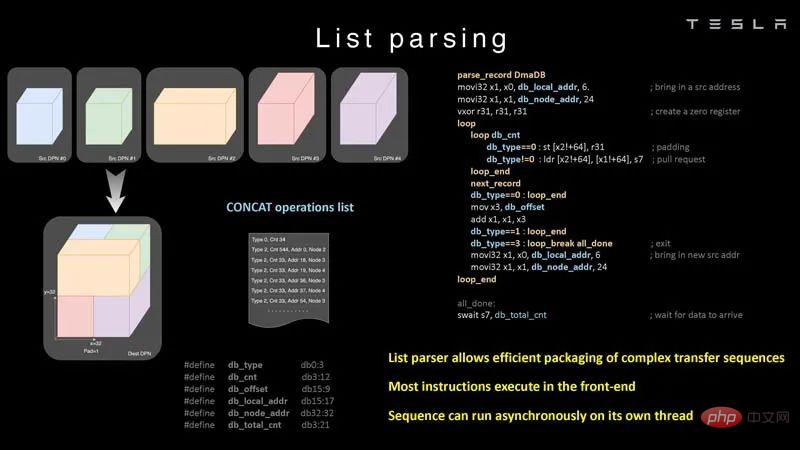

チップができることの例を次に示します。リストの解析を行います。

#リスト解析

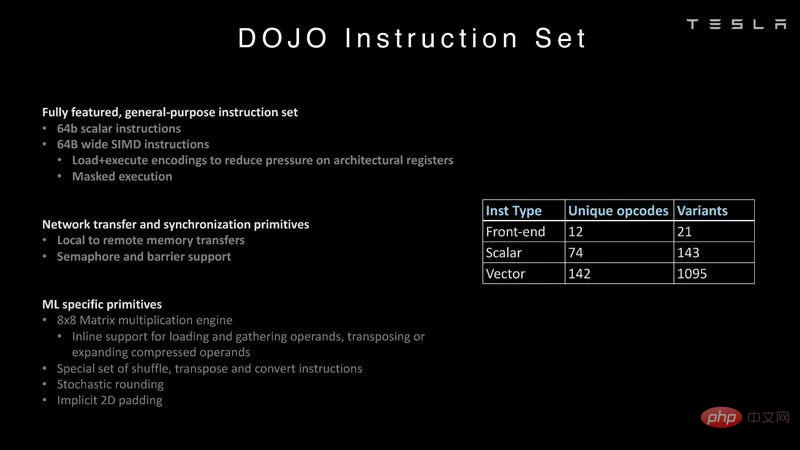

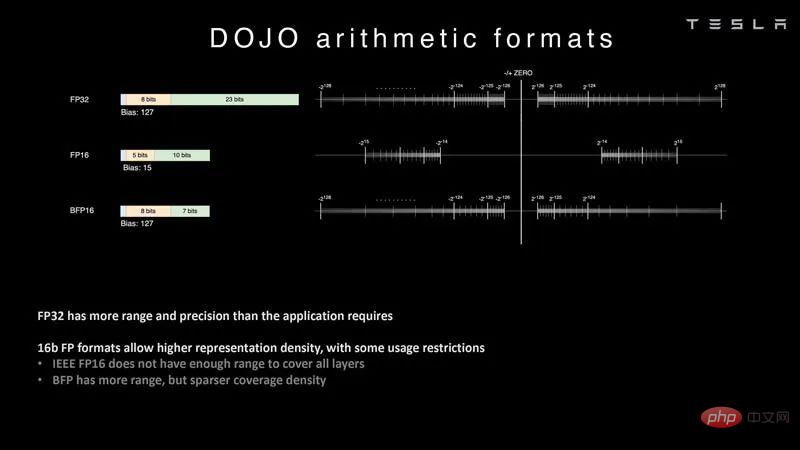

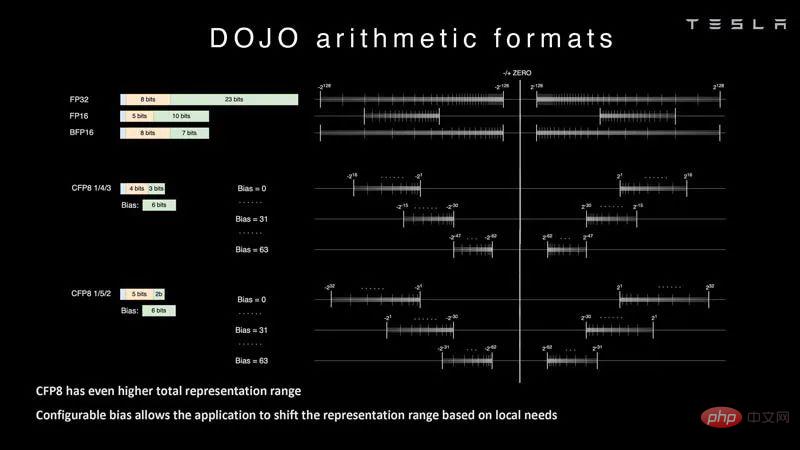

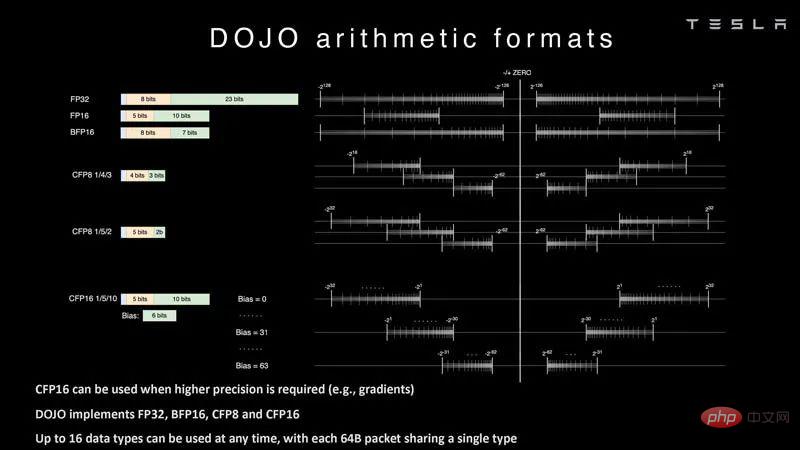

命令セットの詳細については、こちらをご覧ください。一般的な Intel、Arm、NVIDIA、AMD CPU/GPU 命令セットではなく、Tesla オリジナル。 命令セット 人工知能では、算術形式、特にチップがサポートする形式が非常に重要です。フォーマット。 Tesla は DOJO を使用して、FP32、FP16、BFP16 などの一般的なフォーマットを学習できます。これらは一般的な業界形式です。 #算術フォーマット Tesla は構成可能な FP8 または CFP8 にも取り組んでいます。 4/3 と 5/2 の範囲オプションがあります。これは、FP8 の NVIDIA H100 ホッパー構成に似ています。また、さまざまな FP8 タイプに焦点を当てた Untether.AI Boqueria 1458 RISC-V コア AI アクセラレータも確認できます。 #算術フォーマット 2

これらのコアは、製造されたコアに統合されます。型の中で。 TeslaのD1チップはTSMCによって7nmプロセスを使用して製造されています。各チップには 354 個の Dojo 処理ノードと 440MB の SRAM が搭載されています。

これらの D1 チップは、道場の練習タイルに。 D1 チップはテストされ、5×5 タイルに組み立てられます。これらのタイルの帯域幅はエッジごとに 4.5 TB/秒です。また、モジュールあたり 15kW、または 40 個の I/O ダイで使用される電力を差し引いた D1 チップあたり約 600W の電力供給エンベロープもあります。この比較は、企業がそのようなものを設計したくない場合に、Lightmatter Passage のようなものがより魅力的になる理由を示しています。

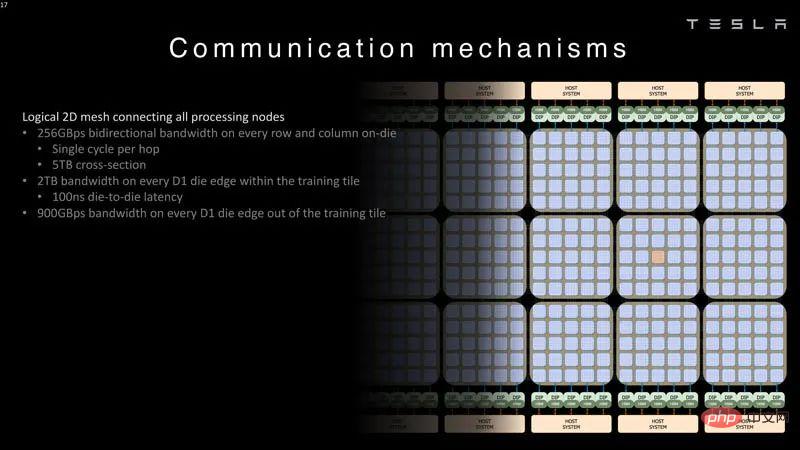

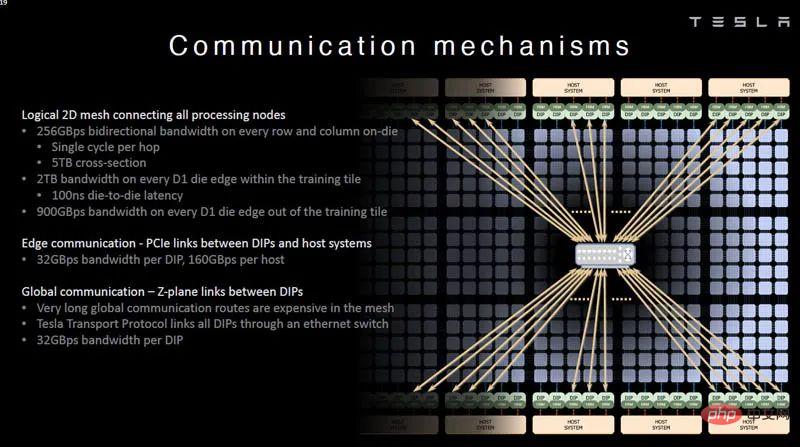

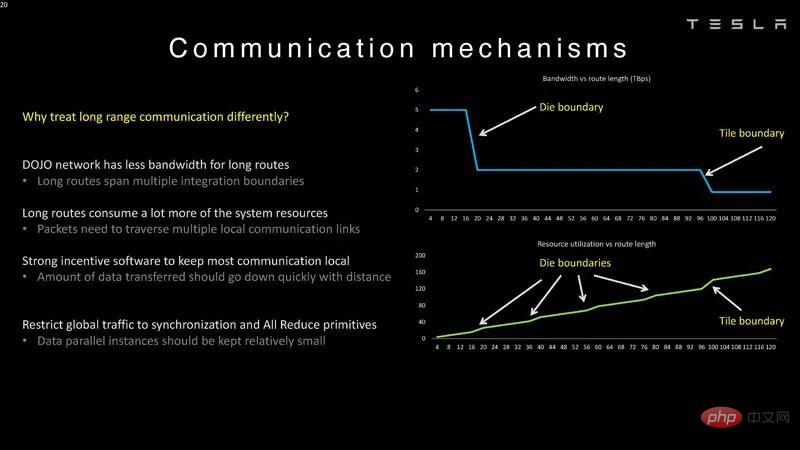

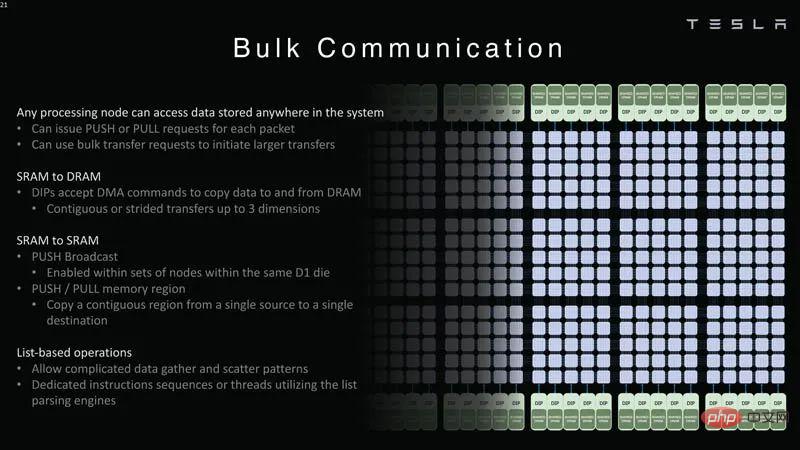

#セカンダリ統合ボックス Dojo トレーニング タイル Dojo インターフェイス プロセッサーは2D グリッドの端に位置します。各トレーニング ブロックには 11 GB の SRAM と 160 GB の共有 DRAM があります。 #Dojo システム トポロジ 以下は、Dojo システムを接続する 2D ネットワークです。処理ノード グリッド帯域幅データ。 #Dojo システム通信ロジックの 2 次元グリッド 各 DIP が提供するものホスト システムへの 32GB/秒のリンク。 ##Dojo システム通信 PCIe リンク DIP およびホスト テスラには、長距離ルート用の Z プレーン リンクもあります。講演の残りの部分で、テスラはシステムレベルのイノベーションについて語った。 #通信メカニズム これはダイとタイルの遅延境界です, そのため、Dojo では扱いが異なります。 Z プレーン リンクが必要な理由は、長いパスはコストがかかるためです。 #Dojo システム通信メカニズム

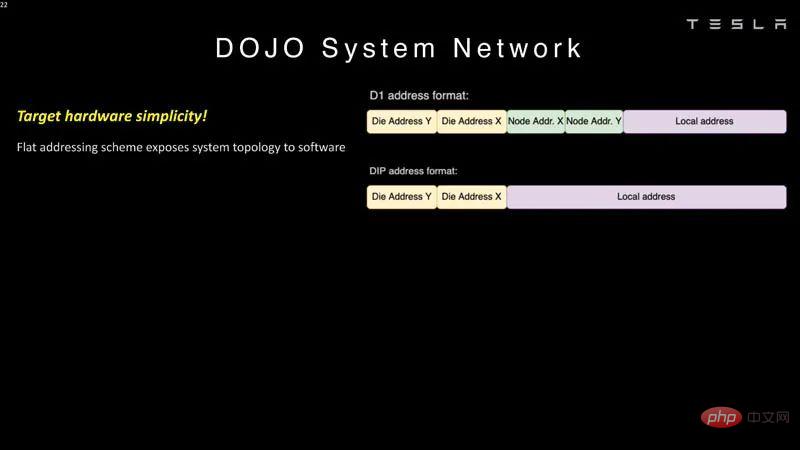

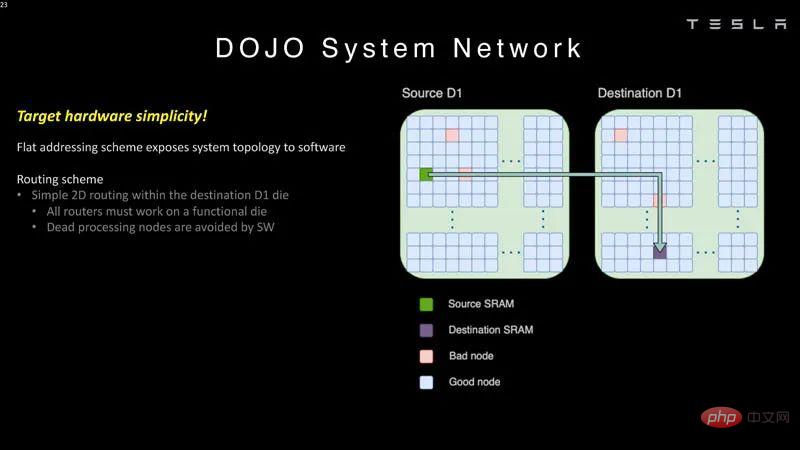

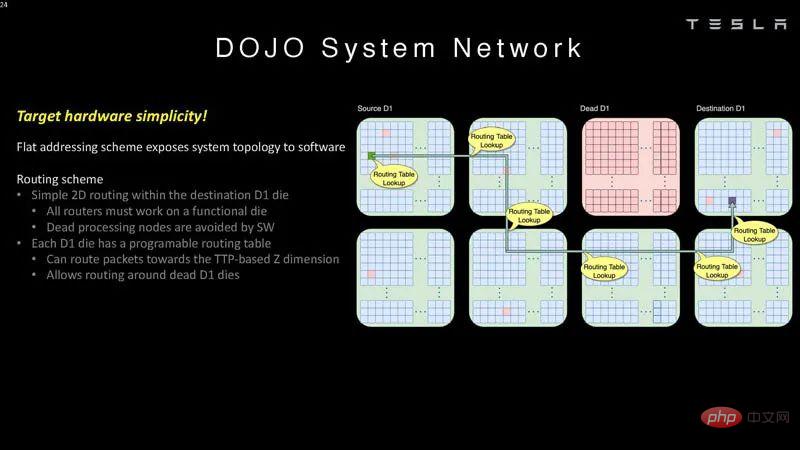

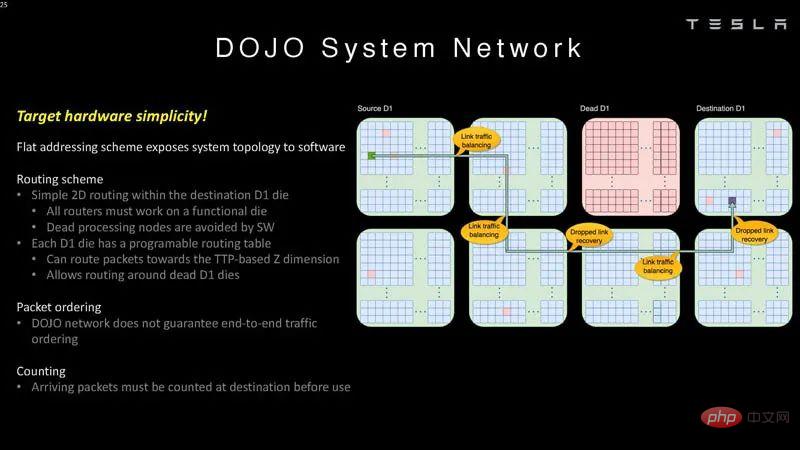

Dojo はフラット アドレッシング スキーム通信を使用します。

これらのチップはソフトウェアでバイパスできます 間違っています処理ノード。

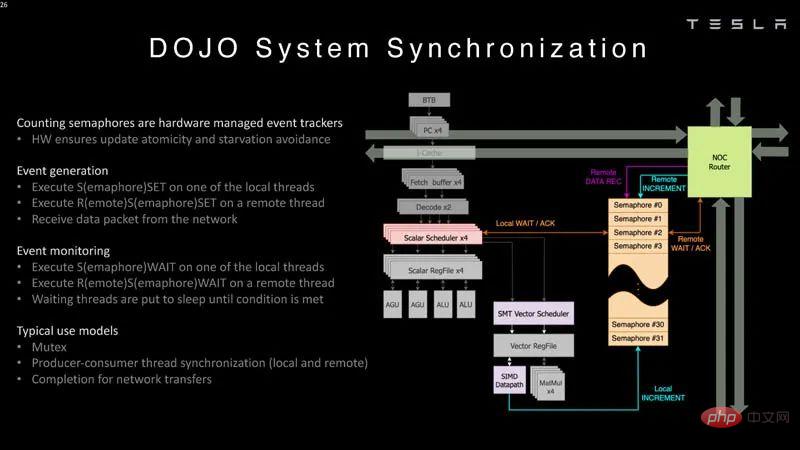

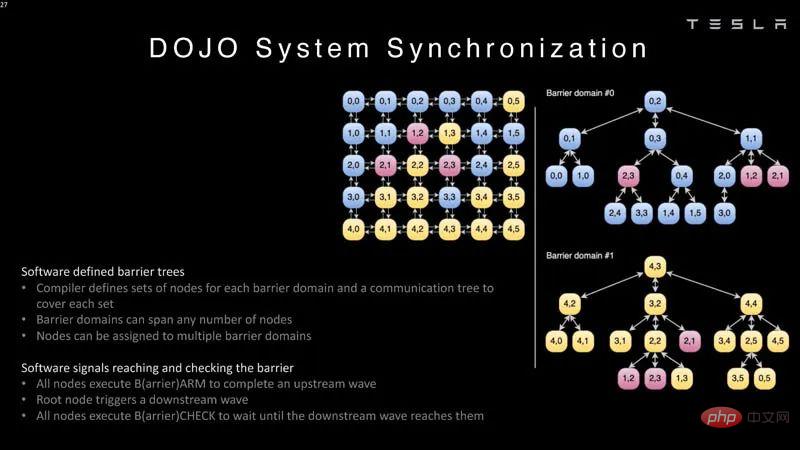

#システム ネットワーク 2 これは、ソフトウェアが次のことを理解する必要があることを意味します。システムトポロジ。 #システム ネットワーク 3 Dojo はエンドツーエンドを保証しません。トラフィックの順序付けが終了するため、宛先でパケットをカウントする必要があります。 #システム ネットワーク 4 システムへのパケットのカウント方法は次のとおりです。同期の一部。 #システム同期 。 システム同期 2

概要 Tesla は、特に大規模な作業を目的として Dojo を構築しました。通常、スタートアップ企業はシステムごとに 1 つまたはいくつかの AI チップを構築しようとします。明らかに、テスラはより大きな規模に焦点を当てています。 テスラが巨大な AI トレーニング場を持つことは、多くの意味で理にかなっています。さらに興味深いのは、市販のシステムを使用しているだけでなく、独自のチップとシステムも構築していることです。スカラー側の一部の ISA は RISC-V から借用していますが、ベクトル側と Tesla がカスタマイズしたアーキテクチャの多くは、多くの作業を必要とします。

#最初の統合ボックス D1 モールド

#最初の統合ボックス D1 モールド

#システム ネットワーク 1

#システム ネットワーク 1

以上がTesla Dojo スーパーコンピューティング アーキテクチャの詳細が初公開!自動運転は「ばらばら」の詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。

ホットAIツール

Undresser.AI Undress

リアルなヌード写真を作成する AI 搭載アプリ

AI Clothes Remover

写真から衣服を削除するオンライン AI ツール。

Undress AI Tool

脱衣画像を無料で

Clothoff.io

AI衣類リムーバー

Video Face Swap

完全無料の AI 顔交換ツールを使用して、あらゆるビデオの顔を簡単に交換できます。

人気の記事

ホットツール

メモ帳++7.3.1

使いやすく無料のコードエディター

SublimeText3 中国語版

中国語版、とても使いやすい

ゼンドスタジオ 13.0.1

強力な PHP 統合開発環境

ドリームウィーバー CS6

ビジュアル Web 開発ツール

SublimeText3 Mac版

神レベルのコード編集ソフト(SublimeText3)

ホットトピック

7622

7622

15

15

1389

1389

52

52

89

89

11

11

31

31

138

138

テスラがついに行動を起こす!自動運転タクシーは間もなく発表されるでしょうか? !

Apr 08, 2024 pm 05:49 PM

テスラがついに行動を起こす!自動運転タクシーは間もなく発表されるでしょうか? !

Apr 08, 2024 pm 05:49 PM

4月8日のニュースによると、テスラのCEOイーロン・マスク氏は最近、テスラが自動運転車技術の開発に取り組んでいることを明らかにし、待望の無人自動運転タクシー「ロボタクシー」が8月8日に正式デビューすると発表した。データ編集者は、マスク氏の発言が次のことであることを知った。以前ロイターは、テスラの自動車運転計画はロボタクシーの生産に焦点を当てていると報じた。しかし、マスク氏はこれに反論し、ロイター通信が低価格車の開発計画を中止し、再び虚偽の報告書を発表したと非難し、一方、低価格車のモデル2とロボタックスの開発は明らかになったと明らかにした。

Tesla Dojo のスーパーコンピューティング デビュー、マスク氏: 年末までに AI をトレーニングするためのコンピューティング能力は、NVIDIA H100 GPU 8,000 個とほぼ同等になるでしょう

Jul 24, 2024 am 10:38 AM

Tesla Dojo のスーパーコンピューティング デビュー、マスク氏: 年末までに AI をトレーニングするためのコンピューティング能力は、NVIDIA H100 GPU 8,000 個とほぼ同等になるでしょう

Jul 24, 2024 am 10:38 AM

7 月 24 日のこの Web サイトのニュースによると、テスラ CEO イーロン マスク (イーロン マスク) は、本日の決算電話会議で、同社が 2,000 台の NVIDIA H100 を搭載するこれまでで最大の人工知能トレーニング クラスターを完成させようとしていると述べました。 GPU。マスク氏はまた、同社の決算会見で投資家に対し、NvidiaのGPUは高価であるため、テスラはDojoスーパーコンピューターの開発に取り組むと語った。このサイトは、マスク氏のスピーチの一部を次のように翻訳しました: Dojo を通じて NVIDIA と競争する道は困難ですが、私たちは今、NVIDIA に過度に依存しています。 NVIDIA の観点からすると、市場が耐えられるレベルまで GPU の価格を引き上げるのは必然ですが、

テスラ サイバートラックが崖から飛び降りて挑む、限界を超えたパワーショー!

Mar 07, 2024 pm 09:28 PM

テスラ サイバートラックが崖から飛び降りて挑む、限界を超えたパワーショー!

Mar 07, 2024 pm 09:28 PM

3月7日のニュースによると、アメリカのユタ州の小さな町でテスラ・サイバートラックが「地獄の復讐への道」に挑戦する動画がこのほどインターネット上で公開された。クリフは米国ユタ州ソルトレイクシティにあり、アウトドア愛好家に人気の場所です。ここには 30 以上のオフロードロードがあり、険しい険しい岩壁に多くのエクストリーム オフロード愛好家が挑戦します。動画では、テスラ サイバートラックが45度近いV字渓谷に挑戦した際、3つのモーターの強力なパワーを頼りに着実に坂道を登り、ついに頂上に到達することに成功した様子が収められています。登りでは、滑りやすい岩の表面にもかかわらず、サイバートラックは滑ることなく順調に走行しました。編集者の理解によると、テスラ サイバートラックのモデルはシングルモーターのリアに分けられます。

テスラの新型モデル3高性能バージョンが韓国認証を通過、パワーパラメータが公開され注目を集めた

Mar 06, 2024 pm 08:49 PM

テスラの新型モデル3高性能バージョンが韓国認証を通過、パワーパラメータが公開され注目を集めた

Mar 06, 2024 pm 08:49 PM

3月6日のニュースによると、メディアは最近、テスラの新しいモデル3高性能バージョンが韓国の関連認証に合格し、一連の注目すべきパワーパラメータを公開したことを明らかにした。この新型車には、フロントに3D3誘導非同期モーター、リアに4D2永久磁石同期モーターを搭載した先進のデュアルモーターシステムが搭載され、これら2つが連携して驚異的なパワーを発揮するという。具体的には、フロントモーターは 215 馬力、リアモーターは最大 412 馬力を供給し、車両の総出力は驚異的な 461kW になります。リアの 4D2 モーターだけの出力は約 303kW です。この新型車のモーター設計は、速度が 110km/h に達するとピーク出力に達することができるため、高速走行時の新型モデル 3 のパフォーマンスが向上します。

テスラのFSD技術がドイツを驚かせ、自動運転は将来有望

Apr 29, 2024 pm 01:20 PM

テスラのFSD技術がドイツを驚かせ、自動運転は将来有望

Apr 29, 2024 pm 01:20 PM

4月29日のニュースによると、テスラは最近、待望の完全自動運転FSD技術をドイツで初めて公の場でデモンストレーションし、FSD技術の欧州市場への正式参入を示した。デモンストレーションイベント中に、スウェーデン運輸省上級顧問のリカルド・フレドリクソン氏が体験する機会がありました。彼はテスラ モデル Y に乗り、FSD(完全自動運転)の利便性を自ら体験しました。ドイツの道路でのパフォーマンス。フレドリクソン氏は、Apple の自動車プロジェクトで製品安全関連の役職を歴任しており、自動運転技術について深い理解を持っています。フレドリクソンの運転支援システムを体験してみると、FSD+12の運転はスムーズで自然だ。彼はまた、ミュンヘン市内中心部から空港に移動するときのことについても特に言及しました。

テスラの2024年第1四半期財務報告書が発表:収益減少、低価格モデルの生産が議題に

Apr 24, 2024 pm 06:16 PM

テスラの2024年第1四半期財務報告書が発表:収益減少、低価格モデルの生産が議題に

Apr 24, 2024 pm 06:16 PM

4月24日のニュースによると、テスラは本日2024年第1四半期の財務報告書を公開した。報告書によると、テスラは同四半期に213億100万米ドルの収益を達成したが、これは前年同期と比べて9%減少した。この数字は市場アナリスト予想の223億ドルを若干下回った。同時に、純利益は11億2,900万米ドルとなり、前年同期比55%の大幅な減少となった。テスラは自動車販売で大きな成功を収めている。第1四半期の全世界での納車台数は38万6,800台で、市場の事前予想である約43万台を大幅に下回った。配送量は前年同期比8.3%減、前期比20.1%減と大幅に減少した。テスラにとって納車台数が前年比で減少するのは2020年以来初めて。速度を落とすために

テスラの上海エネルギー貯蔵ギガファクトリーは年内に試運転開始され、エネルギー貯蔵規模は40GWh近くと推定される

Mar 22, 2024 pm 12:32 PM

テスラの上海エネルギー貯蔵ギガファクトリーは年内に試運転開始され、エネルギー貯蔵規模は40GWh近くと推定される

Mar 22, 2024 pm 12:32 PM

上海未来産業実験区の建設は「1周年」を迎え、臨港新区管理委員会ハイテク部門責任者の陸裕氏が主催した記者会見で、待望のテスラエネルギー貯蔵装置に関する重要な情報が発表された。プロジェクトが明らかになりました。 Lu Yu氏によると、プロジェクトは年内に試作を完了する予定で、生産規模は40GWh近くになる見込みだという。このニュースは広く注目を集めており、テスラのエネルギー貯蔵プロジェクトは地元産業の発展と再生可能エネルギーの利用にとって非常に重要な意味を持つ。世界的に有名な電気自動車メーカーとして、テスラのエネルギー貯蔵分野への参加は大きな注目を集めています。上海と協力することで、臨港新区におけるテスラのエネルギー貯蔵プロジェクトの建設は、地元の産業レベルと技術革新能力の向上に貢献します。 Lu Yu氏はさらに、新エネルギー分野における臨港市の他の進歩についても紹介した。彼は言及した

テスラ サイバートラックの量産は明るい兆し、テキサス工場の航空写真で壮大な生産状況が明らかに

Mar 15, 2024 pm 12:04 PM

テスラ サイバートラックの量産は明るい兆し、テキサス工場の航空写真で壮大な生産状況が明らかに

Mar 15, 2024 pm 12:04 PM

テスラの最新の純電気ピックアップトラック「サイバートラック」の生産進捗が注目を集めている。テスラは目立たないようにしていたが、ジェフ・ロバーツというテスラ観察者が撮影したテキサス・ギガファクトリーの最近の航空ビデオは、サイバートラック生産の前向きな兆候を外の世界に明らかにしているようだ。ビデオによると、テキサス州のテスラ ギガファクトリーにはすでに 300 台以上のサイバートラックがさまざまなエリアに分散されています。今回の台数の多さは、同工場でこれまでに見つかったサイバートラックの中で最多であり、同モデルの量産が急速に進んでいることを示している。これは、テスラがサイバートラックの生産において大幅な進歩を遂げたことを示しています。テスラは以前、Cybertr について懸念を表明していましたが、