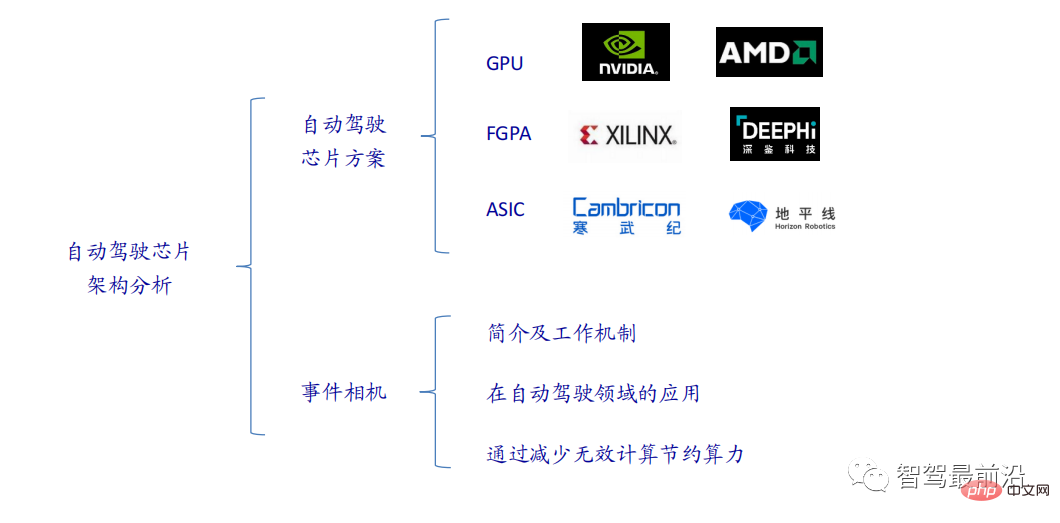

自動運転用の 3 つの主流チップ アーキテクチャの概要を 1 つの記事でまとめたもの

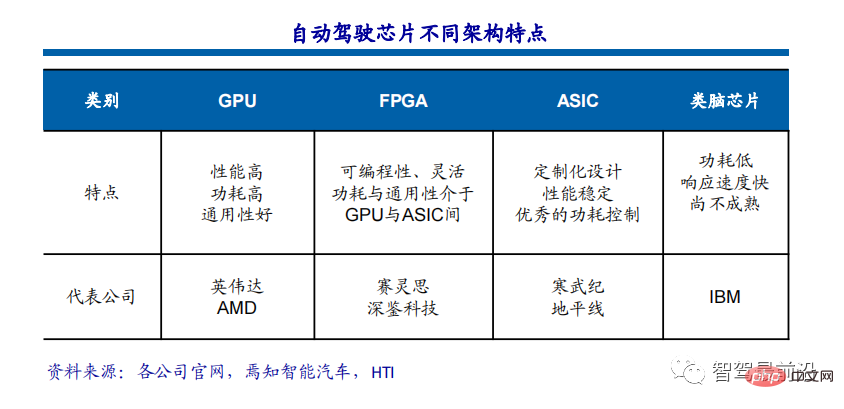

現在主流のAIチップは主にGPU、FPGA、ASICの3つに分類されます。 GPU と FPGA はどちらも比較的成熟した初期段階のチップ アーキテクチャであり、汎用チップです。 ASIC は、特定の AI シナリオ向けにカスタマイズされたチップです。業界は、CPU が AI コンピューティングには適していないことを確認していますが、CPU は AI アプリケーションにも不可欠です。

GPUソリューション

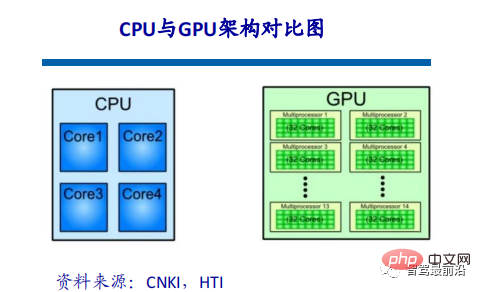

GPUとCPUのアーキテクチャ比較

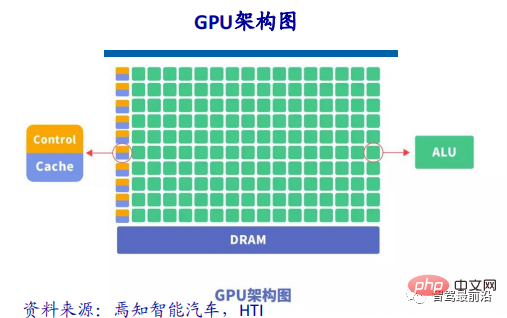

CPUは、格納されたプログラム/データとシリアル逐次実行を核とするフォン・ノイマン・アーキテクチャに従っています。したがって、CPU アーキテクチャは、記憶装置 (キャッシュ) と制御装置 (コントロール) を配置するために大量のスペースを必要としますが、対照的に、演算装置 (ALU) が占める割合は小さいため、CPU の使用できるスペースは大きく制限されます。スケール並列コンピューティングは、論理制御の処理に比較的優れています。

GPU (Graphics Processing Unit)、つまりグラフィックプロセッサは、多数の演算ユニットで構成される大規模な並列計算アーキテクチャであり、元々は CPU から分離されており、特に画像の並列計算データを処理するために使用されていました。複数の画像を同時に処理するように設計されています。 GPU には基本的なコンピューティング ユニット、制御ユニット、ストレージ ユニットも含まれていますが、GPU のアーキテクチャは CPU のアーキテクチャとは大きく異なります。そのアーキテクチャ図を以下に示します。

CPUと比較すると、CPUチップスペースの20%未満がALUですが、GPUチップスペースの80%以上がALUです。つまり、GPU にはデータの並列処理用にさらに多くの ALU が搭載されています。

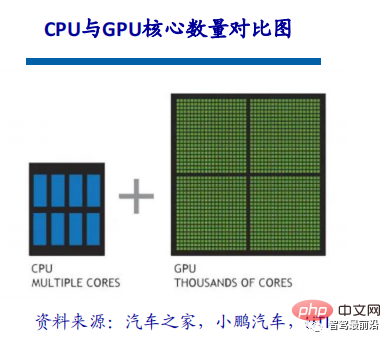

GPUとCPUの違い

CPUは逐次シリアル処理用に最適化された複数のコアで構成されていますが、GPUは数千のより小型で強力なコアで構成された超並列コンピューティングアーキテクチャですこれらの小さなコアは、複数のタスクを同時に処理できるように設計されています。

CPU と GPU が大きく異なる理由は、それぞれ 2 つの異なるアプリケーション シナリオを対象としているためです。 CPU にはさまざまなデータ型を扱うための高い汎用性が必要ですが、同時に論理的な判断が必要となり、分岐ジャンプや割り込み処理が多く発生します。これらすべてにより、CPU の内部構造は非常に複雑になります。 GPU は、型が高度に統一され、相互に依存しない大規模なデータと、中断する必要のない純粋なコンピューティング環境に直面します。

GPUアクセラレーションテクノロジーの簡単な説明

ディープラーニングの場合、現在のハードウェアアクセラレーションは主にグラフィックスプロセッシングユニットの使用に依存しています。従来の CPU と比較して、GPU はコアのコンピューティング能力が数桁高く、並列計算の実行が容易です。

GPU のメニーコア アーキテクチャには数千のストリーム プロセッサが含まれており、演算を並列実行してモデルの計算時間を大幅に短縮できます。 NVIDIA、AMD、その他の企業が自社の GPU の大規模並列アーキテクチャのサポートを推進し続けるにつれて、一般的なコンピューティング用の GPU は並列アプリケーションを高速化する重要な手段となっています。

現在、GPUは比較的成熟した段階まで発展しています。 GPU を使用してディープ ニューラル ネットワークをトレーニングすると、数千のコンピューティング コアの効率的な並列コンピューティング機能を最大限に活用でき、膨大なトレーニング データが使用されるシナリオでは、費やす時間が大幅に短縮され、占有されるサーバーが少なくなります。適切なディープ ニューラル ネットワーク向けに適切に最適化されている場合、GPU カードは数十、さらには数百の CPU サーバーの計算能力と同等になる可能性があるため、GPU はディープ ラーニング モデルのトレーニングに業界で推奨されるソリューションとなっています。

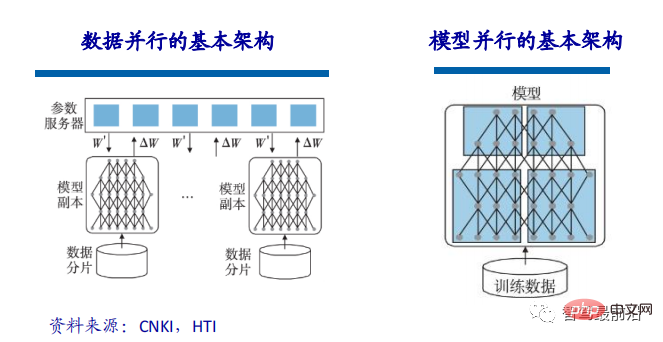

トレーニングされたモデルの規模が比較的大きい場合、データ並列処理によってモデルのトレーニングを高速化できます。データ並列処理により、トレーニング データをセグメント化し、複数のモデル インスタンスを使用して複数のデータ チャンクを同時にトレーニングできます。データ並列処理の実装では、同じモデルと異なるデータがトレーニングに使用されるため、モデルのパフォーマンスに影響を与えるボトルネックは、複数の CPU または複数の GPU 間のパラメーター交換にあります。パラメータ更新式によれば、すべてのモデルで計算された勾配をパラメータ サーバーに送信して、対応するパラメータに更新する必要があるため、データ スライスの分割とパラメータ サーバーの帯域幅がボトルネックとなり、効率が制限される可能性があります。データの並列性。

データの並列処理に加えて、モデルの並列処理を使用してモデルのトレーニングを高速化することもできます。モデルの並列処理とは、大規模なモデルを複数のシャードに分割し、各トレーニング ユニットがそれぞれ保持して、大規模なモデルのトレーニングを完了することを指します。

GPU アクセラレーション コンピューティング

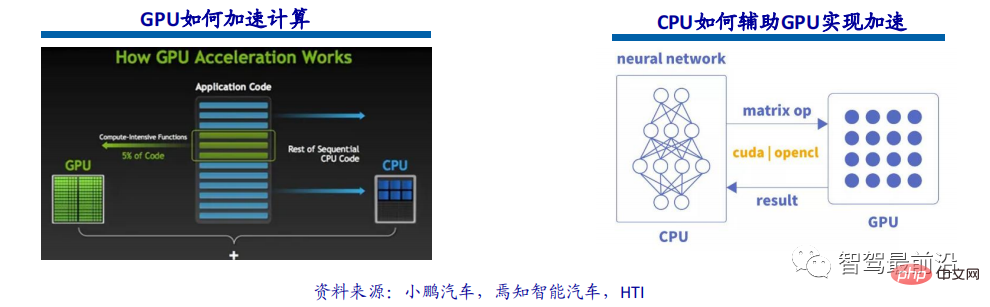

GPU アクセラレーション コンピューティングとは、グラフィックス プロセッシング ユニット (GPU) と CPU を同時に使用して、科学、分析、エンジニアリング、コンシューマーおよびエンタープライズ アプリケーションを高速化することを指します。 2007 年に NVIDIA によって初めて導入された GPU アクセラレータは、現在、政府研究所、大学、企業、中小企業のエネルギー効率の高いデータ センターをサポートするために世界中で使用されています。 GPU は、自動車、電話、タブレットからドローンやロボットに至るまで、さまざまなプラットフォーム上のアプリケーションを高速化します。

GPU アクセラレーション コンピューティングは、アプリケーションの計算集中部分のワークロードを GPU にオフロードしながら、残りのプログラム コードを CPU に実行させることで、並外れたアプリケーション パフォーマンスを提供できます。ユーザーの観点から見ると、アプリケーションは大幅に高速に実行されます。

GPU は現在、単純な行列の乗算と加算の単純な演算のみを実行します。ニューラル ネットワーク モデルの構築とデータ ストリームの送信は引き続き CPU 上で実行されます。 CPU と GPU 間の対話プロセス: GPU 情報の取得、GPU ID の構成、ニューロン パラメーターの GPU へのロード、GPU によるニューラル ネットワーク計算の高速化、GPU 計算結果の受信。

自動運転の分野で GPU が重要な理由

自動運転技術における最も重要な技術カテゴリの 1 つは、深層学習アーキテクチャに基づく人工知能です。コンピュータビジョン、自然言語処理、センサーフュージョン、目標認識、自動運転などの自動車業界のさまざまな分野で、自動運転スタートアップからインターネット企業、大手OEMまで、GPUの使用が積極的に検討されています。自動操縦の最終目標を達成するためのニューラル ネットワークを構築します。

GPU アクセラレーション コンピューティングの誕生後、エンタープライズ データ用のマルチコア並列コンピューティング アーキテクチャを提供し、以前の CPU アーキテクチャでは処理できなかったデータ ソースをサポートします。比較によると、同じ深層学習トレーニング タスクを完了するために、GPU コンピューティング クラスターを使用するコストは、CPU コンピューティング クラスターのコストのわずか 1/200 です。

GPU は自動運転とディープラーニングの鍵です

GPU により、車がリアルタイムで周囲の環境を認識できるようになったり、運転ルートや行動を迅速に計画したりできるようになりますが、これらすべてには車の脳が迅速に反応することはコンピューターにとって非常に重要です。自動運転のプロセスでは、人工知能の急速な発展に対処するために、ディープラーニングまたは人工知能アルゴリズムが常に必要とされています。 、ディープラーニングと無人運転は、GPU コンピューティング開発の黄金時代をもたらしました。

GPU のもう 1 つの重要なパラメータは、浮動小数点演算能力です。浮動小数点カウントでは、浮動小数点を使用して、固定小数点数に対応する、異なる長さの 2 進数を使用して数値を表します。自動運転アルゴリズムを反復する場合、精度要件は高く、浮動小数点演算のサポートが必要です。

FPGAソリューション

FPGAチップの定義と構造

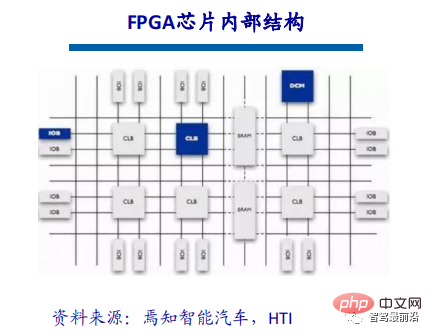

FPGA (フィールドプログラマブルゲートアレイ) は、フィールドプログラマブルゲートアレイであり、PAL、GAL、CPLD などのプログラマブルデバイスをベースにしたさらなる開発製品です。これは、特定用途向け集積回路の分野におけるセミカスタム回路として登場し、カスタム回路の欠点を解決するだけでなく、オリジナルのプログラマブルデバイスのゲート回路の数が限られているという欠点も克服します。

FPGA チップは主に 6 つの部分で完成します。すなわち、プログラマブル入出力ユニット、基本的なプログラマブル ロジック ユニット、完全なクロック管理、組み込みブロック RAM、豊富な配線リソース、組み込み基礎機能ユニット、および内部組み込み特殊ハードウェア モジュールです。現在主流のFPGAは依然としてルックアップテーブル技術をベースにしており、以前のバージョンの基本性能をはるかに超えており、ハードコア(ASICタイプ)モジュールと共通機能(RAM、クロック管理、DSPなど)を統合しています。 。

FPGAの動作原理

FPGAは繰り返しプログラムする必要があるため、その組み合わせロジックの基本構造はASICのような固定NANDゲートでは完成できず、何度でも簡単に設定できます。ルックアップ テーブルは、この要件を十分に満たすことができます。現在、主流の FPGA はすべて、SRAM テクノロジに基づくルックアップ テーブル構造を使用しています。また、フラッシュまたはヒューズおよびアンチヒューズ テクノロジに基づくルックアップ テーブル構造を使用する一部の FPGA もあります。 FPGA の繰り返しコンフィギュレーションは、ファイルを書き込んでルックアップ テーブルの内容を変更することによって実現されます。

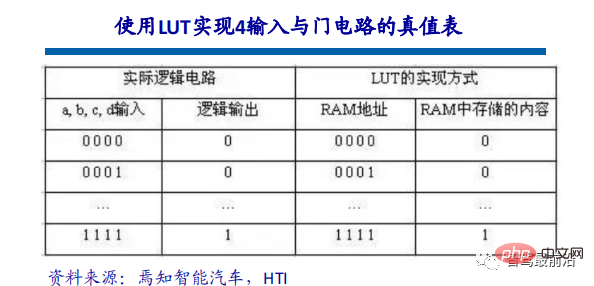

Look-Up-Table は LUT と呼ばれ、LUT は本質的には RAM です。現在、FPGA では 4 入力 LUT が主に使用されているため、各 LUT は 4 ビットのアドレス ラインを持つ RAM とみなすことができます。ユーザーが回路図や HDL 言語で論理回路を記述すると、PLD/FPGA 開発ソフトウェアが論理回路の考えられるすべての結果を自動的に計算し、真理値表 (結果) を RAM に事前に書き込みます。信号が入力されるたびに論理演算を行うことは、アドレスを入力してテーブルを参照し、アドレスに対応する内容を見つけて出力することと同じです。

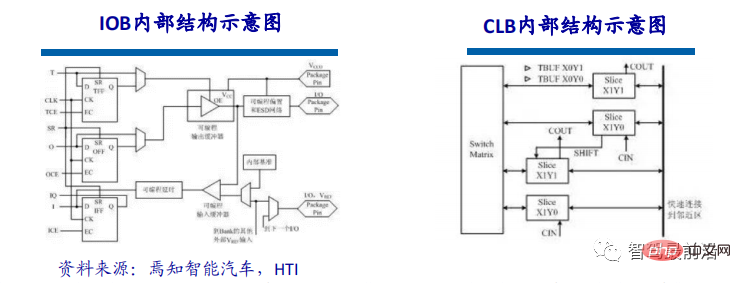

I/Oユニットと呼ばれるプログラマブル入出力ユニットは、チップと外部回路の間のインターフェース部分であり、さまざまな条件下での入出力信号の駆動およびマッチング要件を完了します。電気的特性。 FPGA 内の I/O はグループに分類されており、各グループは異なる I/O 規格を独立してサポートできます。ソフトウェアの柔軟な構成により、さまざまな電気規格や I/O の物理特性に適応し、駆動電流を調整し、プルアップ抵抗とプルダウン抵抗を変更できます。現在、I/O ポートの周波数はますます高くなっており、一部のハイエンド FPGA は DDR レジスタ テクノロジを通じて最大 2Gbps のデータ レートをサポートできます。

CLB は FPGA 内の基本的なロジック ユニットです。 CLB の実際の数と特性はデバイスによって異なりますが、各 CLB には、4 つまたは 6 つの入力、いくつかの選択回路 (マルチプレクサなど)、およびフリップフロップ構成で構成される構成可能なスイッチ マトリックスが含まれています。スイッチ マトリクスは柔軟性が高く、組み合わせロジック、シフト レジスタ、または RAM を処理するように構成できます。ザイリンクスの FPGA デバイスでは、CLB は複数 (通常は 4 または 2) の同一のスライスと追加のロジックで構成されます。各 CLB モジュールは、組み合わせロジックおよび順序ロジックの実装に使用できるだけでなく、分散 RAM および分散 ROM として構成することもできます。

自動運転の「中核的」キラー

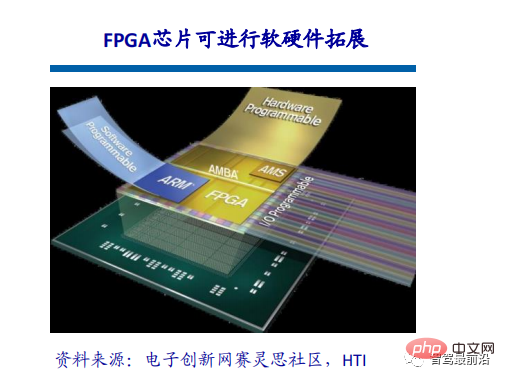

自動運転と先進運転支援システム(ADAS)の市場セグメントは変革を遂げており、コンピューティングとセンサーに対して新たで複雑な要件を突きつけています能力。 FPGA には他のチップ ソリューションにはない独自の利点があり、自動運転業界の継続的な発展と変化に対応するための優れた選択肢です。 FPGA はチップ分野の特殊なテクノロジである一方で、ソフトウェア ツールを使用して繰り返し構成できます。また、豊富な IO インターフェイスとコンピューティング ユニットを備えています。したがって、FPGA は、アプリケーション シナリオの特定のニーズに応じてパイプライン並列処理とデータ並列処理を同時に処理でき、高いコンピューティング パフォーマンス、低遅延、低消費電力という固有の利点を備えています。

FPGA には、高スループット、高エネルギー効率、リアルタイム処理などの多くの利点があり、自動運転の技術要件に非常に適しています。先進運転支援システム (ADAS) および車載エクスペリエンス (IVE) アプリケーションの標準と要件は急速に進化しており、システム設計者の主な関心事は、より高い性能対電力比を維持しながら、優れた柔軟性と開発サイクルの高速化を実現することです。再プログラム可能な FPGA と増え続ける自動車グレード製品のポートフォリオを組み合わせることで、自動車設計者は設計要件を満たし、常に変化する自動車業界の先を行くことができます。

より適応性の高いプラットフォーム

自動運転チップの真の価値は、計算エンジンの利用、つまり理論上の性能と実際の性能の違いにあります。 FPGA には、多数の配線リンクと大量の小型ストレージが含まれています。これらのリソースを組み合わせることで、設計者はコンピューティング エンジン用にカスタマイズされたデータ フィード ネットワークを作成して、使用率を高めることができます。プログラマブル ロジックは、ADAS や自動運転などの新たなアプリケーション分野の変化するニーズに適応するための高度な柔軟性を顧客に提供します。改善されたインターフェイス標準、アルゴリズムの革新、新しいセンサー技術を活用するには、ソフトウェアの変更だけでなくハードウェアの変更もサポートできる適応性のあるプラットフォームが必要であり、そこがFPGAチップが優れている点です。

FPGAチップはスケーラブルです。スケーラブルなチップは、主にピン互換のパッケージでプログラマブル ロジックの量を変更します。これは、開発者が低、中、高バージョンの ADAS 機能パッケージをホストする単一の ECU プラットフォームを作成し、必要な最小密度のチップを選択することで必要に応じてコストを拡張できることを意味します。

差別化ソリューション

FPGAチップを使用すると、開発者は特定のアプリケーションやセンサー向けに最適化できる独自の差別化された処理ソリューションを作成できます。これは ASSP チップでは不可能であり、専用アクセラレータを提供するチップであっても使用方法が限られており、基本的にすべての競合他社が利用できます。たとえば、ザイリンクスの長年の顧客は、自分たちだけがアクセスできる高価値 IP のライブラリを作成しており、それらの機能は同社のさまざまな製品で使用できます。 90nm ノードから始まったザイリンクス チップは、大量生産の車載アプリケーションにとって非常にコスト効率が高く、業界で 1 億 6,000 万個を超えるザイリンクス チップが使用されています。

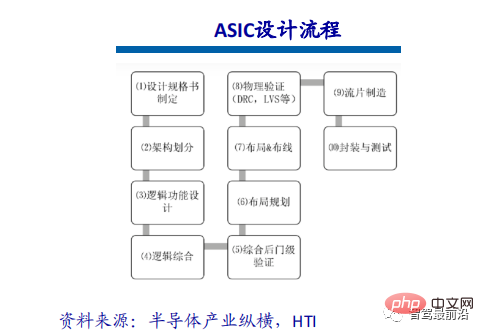

ASICソリューション

ASICの定義と特性

ASICチップは、さまざまな端末機能に応じてTPUチップ、DPUチップ、NPUチップに分類できます。その中でもTPUは機械学習専用のテンソルプロセッサです。たとえば、Google は 2016 年 5 月に Tensorflow プラットフォーム用のプログラム可能な AI アクセラレータを開発しました。その内部命令セットは、Tensorflow プログラムが変更されたり、アルゴリズムが更新されたときに実行できます。 DPU はデータ処理ユニットであり、データ センターなどのコンピューティング シナリオにエンジンを提供できます。 NPU は、人間のニューロンとシナプスを回路レベルでシミュレートし、深層学習命令セットを使用して大規模な電子ニューロンとシナプス データを直接処理するニューラル ネットワーク プロセッサです。

ASICにはフルカスタマイズとセミカスタマイズの2つの設計方法があります。フルカスタマイズは、集積回路設計プロセス全体を完全に独立した方法で完了するために多大な労力と時間のコストを必要としますが、セミカスタマイズ ASIC よりも柔軟で優れていますが、開発効率はセミカスタマイズに比べて非常に低くなります。

明らかなパフォーマンスの向上

ASIC チップは、人工知能アプリケーションのシナリオに非常に適しています。たとえば、ディープ ラーニング用にゼロから設計された NVIDIA の最初のチップである Tesla P100 は、2014 年に発売された GPU シリーズの 12 倍のデータ処理速度を備えています。 Google が機械学習用にカスタマイズしたチップ TPU は、ムーアの法則の開発から 7 年後にハードウェアのパフォーマンスを現在のチップと同等のレベルに向上させました。 CPU が過去の巨大コンピューターを変えたのと同じように、人工知能 ASIC チップも今日の AI ハードウェア デバイスの外観を大きく変えるでしょう。たとえば、有名な AlphaGo は約 170 個のグラフィックス処理装置 (GPU) と 1,200 個の中央処理装置 (CPU) を使用しており、これらのデバイスにはコンピューター室、高出力の空調設備、およびシステム保守のための複数の専門家が必要です。そして、すべて専用チップを使用すれば、必要なスペースは通常の保管箱程度で済む可能性が高く、消費電力は大幅に削減されます。

ASIC テクノロジーのルートは限られており、オープンであるため、チップ企業は、運転に関連する主流のネットワーク、モデル、オペレーター向けに開発する必要があります。同じ性能であれば、チップ面積が小さくなり、コストが安くなり、消費電力も低くなります。 ASIC テクノロジーのルートには、将来的に大きな可能性があります。ASIC ルートの選択は、モデルごとに異なる ASIC を開発したり、異なる検証を実行したりすることを意味するものではありません。異なるモデルで実装する必要がある機能はほぼ同じであり、チップがモデルや演算子にアクセスできる範囲は限られているため、アルゴリズムを高速に反復しても、チップの上位層機能のサポートには影響しません。自動車メーカーはチップ設計会社と協力して、差別化されたカスタマイズ、つまりより良い選択を実行します。なぜなら、カスタマイズが差別化されていても、チップの内部部品の 50% は汎用だからです。チップ設計会社は、オリジナルのバージョンに基づいて差別化された設計を実行して、いくつかの差別化された機能を実現できます。

主流アーキテクチャソリューションの比較: 3つの主流アーキテクチャ

FPGAは、PALやGALなどのプログラマブルデバイスに基づいてさらに開発された製品です。これは、特定用途向け集積回路の分野におけるセミカスタム回路として登場し、カスタム回路の欠点を解決するだけでなく、オリジナルのプログラマブルデバイスのゲート回路の数が限られているという欠点も克服します。利点: 無制限のプログラミング、低遅延、パイプライン並列処理とデータ並列処理、最強のリアルタイム パフォーマンス、最高の柔軟性。短所: 開発が難しく、固定小数点演算のみに適しており、比較的高価です。

グラフィックス プロセッシング ユニット (GPU) は、ディスプレイ コア、ビジュアル プロセッサ、ディスプレイ チップとも呼ばれ、パーソナル コンピューター、ワークステーション、ゲーム機、一部のモバイル デバイス (など) での画像と処理に特化したグラフィックス プロセッシング ユニットの一種です。 (タブレット、携帯電話など) グラフィックス関連の操作を実行するマイクロプロセッサ。利点: マルチコア並列コンピューティングの基本構造を提供し、非常に多くのコアを備えているため、大量のデータの並列コンピューティングをサポートでき、より高い浮動小数点コンピューティング能力を備えています。短所: 管理制御能力 (最も弱い)、消費電力 (最も高い)。

ASIC、または特定用途向け集積回路とは、特定のユーザー要件および特定の電子システムのニーズに応じて設計および製造された集積回路を指します。現在、ASIC を設計する最も一般的な方法の 1 つは、CPLD (Complex Programmable Logic Device) と FPGA (Field Programmable Logic Array) を使用するものです。利点: 集積回路技術と、特定のユーザーの完全なマシンまたはシステム技術の製品として、汎用集積回路と比較して、サイズが小さく、軽量で、消費電力が低く、信頼性が向上し、パフォーマンスと機密性が向上します。コスト削減やその他の利点。欠点: 柔軟性が不十分で、FPGA よりも高価です。

コンピューティングパワー理論の限界: TOPS のコンピューティングパワーは実際のパフォーマンスと完全に等しいわけではありません

ADAS、自動運転技術の台頭、そしてソフトウェアデファインドカーの段階的な深化に伴い、スマートカー コンピューティングパワーと大規模なデータ処理能力の需要が急増しており、従来の自動車のチップ「スタッキング」ソリューションでは、自動運転のコンピューティングパワーのニーズを満たすことができなくなりました。チップは最終的に自動車会社の車載コンピューティング プラットフォームとして機能します。「ソフトウェア デファインド カー」の場合、インテリジェント ドライビング システム コンピューティング プラットフォームのサポート問題は、チップのコンピューティング パワーを積み重ねるだけでは解決できません。

チップはソフトウェアの舞台です。チップの品質を測定する基準は、チップ上のソフトウェアがその機能を最大限に発揮できるかどうかによって決まります。コンピューティング能力とソフトウェアが効果的に一致している必要があります。同じ計算能力を持つ 2 つのチップを比較した場合、ソフトウェアをより効率的に実行できるチップが「良いチップ」となります。コンピューティング能力の真の値を決定する最も重要な要素は、メモリ (SRAM および DRAM) の帯域幅、実際の動作周波数 (つまり、供給電圧または温度)、およびアルゴリズムのバッチ サイズです。

シングルチップの計算能力TOPSは重要な指標ですが、自動運転は車両と道路、クラウドエッジの連携を必要とする複雑なシステムです。したがって、コアに加えて、その競合にはソフトウェアとハードウェアの相乗効果、プラットフォーム、ツールチェーンなどが含まれます。チップのコンピューティング能力と組み込みハードウェアの無限の拡大は将来のトレンドではなく、ハードウェアも現実の状況に適合する必要があります。この高さの背後には、高消費電力と低使用率の問題があります。

イベントカメラの紹介

概要と動作メカニズム

イベントカメラは人間の目や動物の視覚からインスピレーションを得ており、シリコン網膜と呼ぶ人もいます。生物視覚は変化のある領域のみを感知し、イベント カメラはイベントの発生や変化を捉えます。 ,

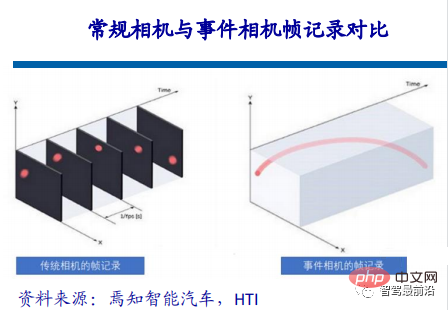

従来の視覚フィールドでは、カメラから返される情報は同期しています。いわゆる同期とは、特定の時間 t でカメラが露光を実行し、その時点ですべてのピクセルを塗りつぶすことを意味します。マトリックスを作成して写真を送信します。写真内のすべてのピクセルは同じ瞬間に対応します。ビデオに関して言えば、それは単なる多数のフレームの画像です。これはフレーム レート (フレーム レート) であり、時間遅延 (時間遅延) とも呼ばれます。イベント カメラは人間の脳や目に似ており、無関係な背景をスキップしてシーンの核心を直接感知し、データではなく純粋なイベントを作成します。

イベント カメラの動作メカニズムは、特定のピクセルの明るさが特定のしきい値に変化すると、カメラは上記の形式でイベントを返します。最初の 2 つの項目はイベントのピクセル座標です。 3番目の項目はイベントのタイムスタンプで、最後の項目は極性(極性)0、1(または-1、1)で、明るさが低から高、または高から低かを表します。

このように、カメラの視野全体でピクセル値に変化がある限り、これらのイベントはすべて非同期で発生します (時間間隔がどんなに短くても、発生することはありません)。完全に同時であるため、イベントのタイムスタンプは異なります。単純なリターンのため、従来のカメラと比較して遅延が短く、短い時間間隔でピクセルの変化をキャプチャできます。

自動運転分野での応用

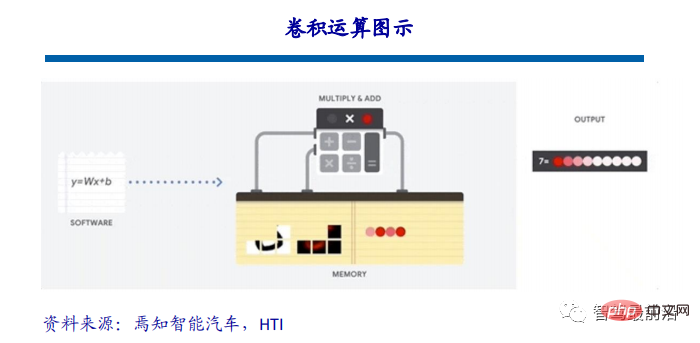

今日の自動運転分野で使用される視覚認識アルゴリズムは、基本的に畳み込みニューラルネットワークに基づいており、視覚アルゴリズムの動作は基本的には畳み込み演算を繰り返します。この種の計算は本質的には、乗算、累積演算の一種である加算、減算、乗算、除算を行うだけであり、複雑ではありません。ただし、畳み込みニューラル ネットワークにはこのような単純な演算が大量に存在するため、プロセッサのパフォーマンスに高い要求が生じます。

ResNet-152 を例に挙げます。これは 152 層の畳み込みニューラル ネットワークであり、このネットワークが 1080P の画像を処理する場合、計算量は約 226 億回になります。 30 フレームのカメラの場合、必要な計算能力は 1 秒あたり 33 兆回にも及び、非常に膨大です。

無効な計算を減らしてコンピューティングパワーを節約

自動運転分野の視覚データの99%はAI処理のバックグラウンドとして役に立たない。たとえば、ゴーストプローブを検出する場合、変化した領域はごく一部ですが、従来の視覚処理では依然として変化しない背景領域の 99% を処理する必要があり、大量の計算能力を浪費するだけでなく、時間も浪費します。 。あるいは、砂利の中にダイヤモンドがある場合、AI チップと従来のカメラは砂の粒を 1 つずつ識別してダイヤモンドを取り除く必要がありますが、人間は砂粒を観察するだけでダイヤモンドを検出できます。従来のカメラは人間の 100 倍または 1000 倍の時間がかかります。

イベントカメラの利点は、冗長な情報が減り、遅延がほとんどないという利点に加えて、高速オブジェクトを撮影する場合、従来のカメラでは露光時間によるブレが発生することもあります。イベントカメラにはほとんどブレがありません。さらに、イベント カメラは非常に高いダイナミック レンジを備えています。イベント カメラの特性により、従来のカメラは光の強さが強い環境でも弱い環境でも「ブラインド」になりますが、ピクセルの変化は依然として存在するため、イベント カメラは可能です。まだ物がはっきり見えます。

以上が自動運転用の 3 つの主流チップ アーキテクチャの概要を 1 つの記事でまとめたものの詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。

ホットAIツール

Undresser.AI Undress

リアルなヌード写真を作成する AI 搭載アプリ

AI Clothes Remover

写真から衣服を削除するオンライン AI ツール。

Undress AI Tool

脱衣画像を無料で

Clothoff.io

AI衣類リムーバー

AI Hentai Generator

AIヘンタイを無料で生成します。

人気の記事

ホットツール

メモ帳++7.3.1

使いやすく無料のコードエディター

SublimeText3 中国語版

中国語版、とても使いやすい

ゼンドスタジオ 13.0.1

強力な PHP 統合開発環境

ドリームウィーバー CS6

ビジュアル Web 開発ツール

SublimeText3 Mac版

神レベルのコード編集ソフト(SublimeText3)

ホットトピック

7491

7491

15

15

1377

1377

52

52

77

77

11

11

19

19

41

41

なぜ自動運転ではガウス スプラッティングが非常に人気があるのに、NeRF は放棄され始めているのでしょうか?

Jan 17, 2024 pm 02:57 PM

なぜ自動運転ではガウス スプラッティングが非常に人気があるのに、NeRF は放棄され始めているのでしょうか?

Jan 17, 2024 pm 02:57 PM

上記と著者の個人的な理解 3 次元ガウシアンプラッティング (3DGS) は、近年、明示的な放射線フィールドとコンピューター グラフィックスの分野で出現した革新的なテクノロジーです。この革新的な方法は、数百万の 3D ガウスを使用することを特徴とし、主に暗黙的な座標ベースのモデルを使用して空間座標をピクセル値にマッピングする神経放射線場 (NeRF) 方法とは大きく異なります。明示的なシーン表現と微分可能なレンダリング アルゴリズムにより、3DGS はリアルタイム レンダリング機能を保証するだけでなく、前例のないレベルの制御とシーン編集も導入します。これにより、3DGS は、次世代の 3D 再構築と表現にとって大きな変革をもたらす可能性のあるものとして位置付けられます。この目的を達成するために、私たちは 3DGS 分野における最新の開発と懸念について初めて体系的な概要を提供します。

自動運転シナリオにおけるロングテール問題を解決するにはどうすればよいでしょうか?

Jun 02, 2024 pm 02:44 PM

自動運転シナリオにおけるロングテール問題を解決するにはどうすればよいでしょうか?

Jun 02, 2024 pm 02:44 PM

昨日の面接で、ロングテール関連の質問をしたかと聞かれたので、簡単にまとめてみようと思いました。自動運転のロングテール問題とは、自動運転車におけるエッジケース、つまり発生確率が低い考えられるシナリオを指します。認識されているロングテール問題は、現在、単一車両のインテリジェント自動運転車の運用設計領域を制限している主な理由の 1 つです。自動運転の基礎となるアーキテクチャとほとんどの技術的問題は解決されており、残りの 5% のロングテール問題が徐々に自動運転の開発を制限する鍵となってきています。これらの問題には、さまざまな断片的なシナリオ、極端な状況、予測不可能な人間の行動が含まれます。自動運転におけるエッジ シナリオの「ロング テール」とは、自動運転車 (AV) におけるエッジ ケースを指します。エッジ ケースは、発生確率が低い可能性のあるシナリオです。これらの珍しい出来事

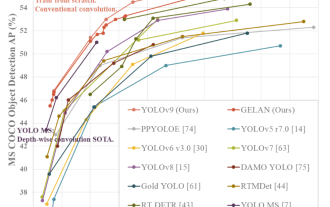

YOLOは不滅です! YOLOv9 がリリースされました: パフォーマンスとスピード SOTA~

Feb 26, 2024 am 11:31 AM

YOLOは不滅です! YOLOv9 がリリースされました: パフォーマンスとスピード SOTA~

Feb 26, 2024 am 11:31 AM

現在の深層学習手法は、モデルの予測結果が実際の状況に最も近くなるように、最適な目的関数を設計することに重点を置いています。同時に、予測に十分な情報を取得するには、適切なアーキテクチャを設計する必要があります。既存の方法は、入力データがレイヤーごとの特徴抽出と空間変換を受けると、大量の情報が失われるという事実を無視しています。この記事では、ディープネットワークを介してデータを送信する際の重要な問題、つまり情報のボトルネックと可逆機能について詳しく説明します。これに基づいて、深層ネットワークが複数の目的を達成するために必要なさまざまな変化に対処するために、プログラマブル勾配情報 (PGI) の概念が提案されています。 PGI は、目的関数を計算するためのターゲット タスクに完全な入力情報を提供することで、ネットワークの重みを更新するための信頼できる勾配情報を取得できます。さらに、新しい軽量ネットワーク フレームワークが設計されています。

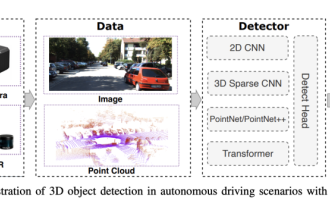

カメラかライダーを選択しますか?堅牢な 3D オブジェクト検出の実現に関する最近のレビュー

Jan 26, 2024 am 11:18 AM

カメラかライダーを選択しますか?堅牢な 3D オブジェクト検出の実現に関する最近のレビュー

Jan 26, 2024 am 11:18 AM

0.前面に書かれています&& 自動運転システムは、さまざまなセンサー (カメラ、ライダー、レーダーなど) を使用して周囲の環境を認識し、アルゴリズムとモデルを使用することにより、高度な知覚、意思決定、および制御テクノロジーに依存しているという個人的な理解リアルタイムの分析と意思決定に。これにより、車両は道路標識の認識、他の車両の検出と追跡、歩行者の行動の予測などを行うことで、安全な運行と複雑な交通環境への適応が可能となり、現在広く注目を集めており、将来の交通分野における重要な開発分野と考えられています。 。 1つ。しかし、自動運転を難しくしているのは、周囲で何が起こっているかを車に理解させる方法を見つけることです。これには、自動運転システムの 3 次元物体検出アルゴリズムが、周囲環境にある物体 (位置を含む) を正確に認識し、記述することができる必要があります。

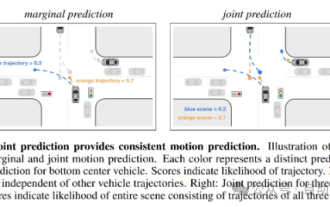

自動運転と軌道予測についてはこの記事を読めば十分です!

Feb 28, 2024 pm 07:20 PM

自動運転と軌道予測についてはこの記事を読めば十分です!

Feb 28, 2024 pm 07:20 PM

自動運転では軌道予測が重要な役割を果たしており、自動運転軌道予測とは、車両の走行過程におけるさまざまなデータを分析し、将来の車両の走行軌跡を予測することを指します。自動運転のコアモジュールとして、軌道予測の品質は下流の計画制御にとって非常に重要です。軌道予測タスクには豊富な技術スタックがあり、自動運転の動的/静的知覚、高精度地図、車線境界線、ニューラル ネットワーク アーキテクチャ (CNN&GNN&Transformer) スキルなどに精通している必要があります。始めるのは非常に困難です。多くのファンは、できるだけ早く軌道予測を始めて、落とし穴を避けたいと考えています。今日は、軌道予測に関するよくある問題と入門的な学習方法を取り上げます。関連知識の紹介 1. プレビュー用紙は整っていますか? A: まずアンケートを見てください。

SIMPL: 自動運転向けのシンプルで効率的なマルチエージェント動作予測ベンチマーク

Feb 20, 2024 am 11:48 AM

SIMPL: 自動運転向けのシンプルで効率的なマルチエージェント動作予測ベンチマーク

Feb 20, 2024 am 11:48 AM

原題: SIMPL: ASimpleandEfficientMulti-agentMotionPredictionBaselineforAutonomousDriving 論文リンク: https://arxiv.org/pdf/2402.02519.pdf コードリンク: https://github.com/HKUST-Aerial-Robotics/SIMPL 著者単位: 香港科学大学DJI 論文のアイデア: この論文は、自動運転車向けのシンプルで効率的な動作予測ベースライン (SIMPL) を提案しています。従来のエージェントセントとの比較

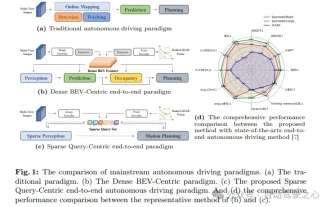

nuScenes の最新 SOTA | SparseAD: スパース クエリは効率的なエンドツーエンドの自動運転に役立ちます。

Apr 17, 2024 pm 06:22 PM

nuScenes の最新 SOTA | SparseAD: スパース クエリは効率的なエンドツーエンドの自動運転に役立ちます。

Apr 17, 2024 pm 06:22 PM

先頭と開始点に書かれている エンドツーエンドのパラダイムでは、統一されたフレームワークを使用して自動運転システムのマルチタスクを実現します。このパラダイムの単純さと明確さにも関わらず、サブタスクにおけるエンドツーエンドの自動運転手法のパフォーマンスは、依然としてシングルタスク手法に比べてはるかに遅れています。同時に、以前のエンドツーエンド手法で広く使用されていた高密度鳥瞰図 (BEV) 機能により、より多くのモダリティやタスクに拡張することが困難になります。ここでは、スパース検索中心のエンドツーエンド自動運転パラダイム (SparseAD) が提案されています。このパラダイムでは、スパース検索は、高密度の BEV 表現を使用せずに、空間、時間、タスクを含む運転シナリオ全体を完全に表します。具体的には、統合されたスパース アーキテクチャが、検出、追跡、オンライン マッピングなどのタスク認識のために設計されています。さらに、重い

エンドツーエンドおよび次世代の自動運転システムと、エンドツーエンドの自動運転に関する誤解について話しましょう。

Apr 15, 2024 pm 04:13 PM

エンドツーエンドおよび次世代の自動運転システムと、エンドツーエンドの自動運転に関する誤解について話しましょう。

Apr 15, 2024 pm 04:13 PM

この 1 か月間、いくつかのよく知られた理由により、私は業界のさまざまな教師やクラスメートと非常に集中的な交流をしてきました。この交換で避けられない話題は当然、エンドツーエンドと人気の Tesla FSDV12 です。この機会に、現時点での私の考えや意見を整理し、皆様のご参考とご議論に役立てたいと思います。エンドツーエンドの自動運転システムをどのように定義するか、またエンドツーエンドで解決することが期待される問題は何でしょうか?最も伝統的な定義によれば、エンドツーエンド システムとは、センサーから生の情報を入力し、関心のある変数をタスクに直接出力するシステムを指します。たとえば、画像認識では、従来の特徴抽出 + 分類子方式と比較して、CNN はエンドツーエンドと言えます。自動運転タスクでは、各種センサー(カメラ/LiDAR)からのデータを入力