NVIDIA は AI を使用して GPU 演算回路を設計し、最先端の EDA と比較して面積を 25% 削減し、高速化と効率化を実現しています。

膨大な数の演算回路が NVIDIA GPU を強化し、AI、ハイパフォーマンス コンピューティング、コンピューター グラフィックスのかつてない高速化を可能にします。したがって、GPU のパフォーマンスと効率を向上させるには、これらの演算回路の設計を改善することが重要です。 AI がこれらの回路の設計を学習したらどうなるでしょうか?最近の NVIDIA の論文「PrefixRL: 深層強化学習を使用した並列プレフィックス回路の最適化」では、研究者は、AI がこれらの回路をゼロから設計できるだけでなく、AI で設計された回路が最新の技術で設計された回路よりも優れていることを実証しました。最先端の電子設計自動化 (EDA) ツールにより、回路がより小さく、より高速になります。

論文アドレス: https://arxiv.org/pdf/2205.07000.pdf

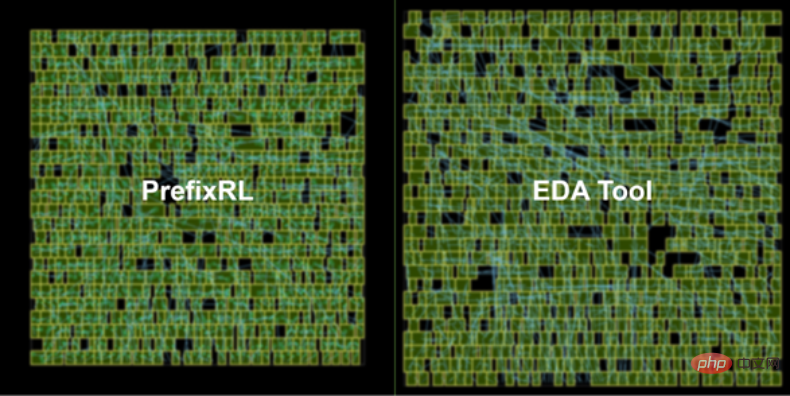

#最新の NVIDIA Hopper GPU アーキテクチャには、AI によって設計された回路サンプルが 13,000 近くあります。下の図 1: 左側の PrefixRL AI によって設計された 64b 加算器回路は、図 1 の右側の最先端の EDA ツールによって設計された回路より 25% 小型です。

回路設計の概要

回路設計の概要

- 小規模: 面積が小さく、より多くの回路をチップ上にパッケージ化できます。

- 高速: 遅延が短くなり、チップのパフォーマンスが向上し、

- 消費電力が低くなります。

したがって、PrefixRL では、研究者は人気のあるクラスの算術回路、つまり並列プレフィックス回路に焦点を当てています。アクセラレータ、インクリメント、エンコーダなど、GPU 内のさまざまな重要な回路はプレフィックス回路であり、上位レベルでプレフィックス グラフとして指定できます。

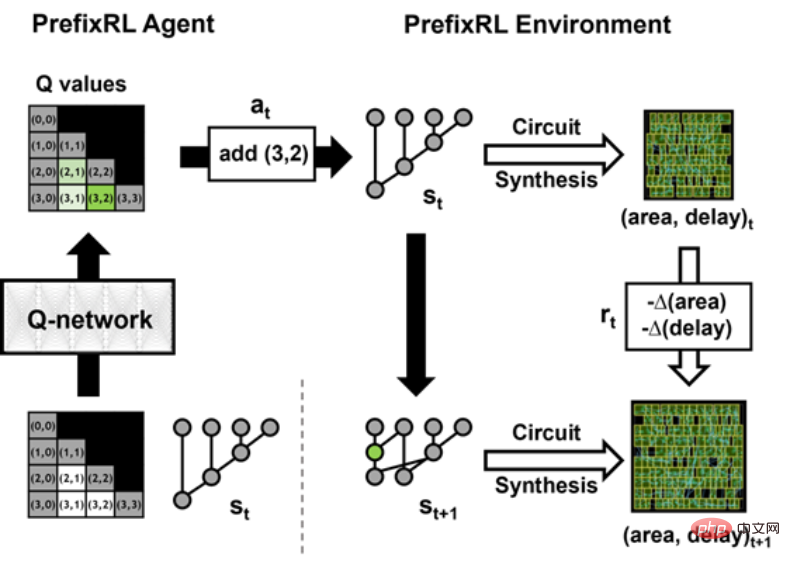

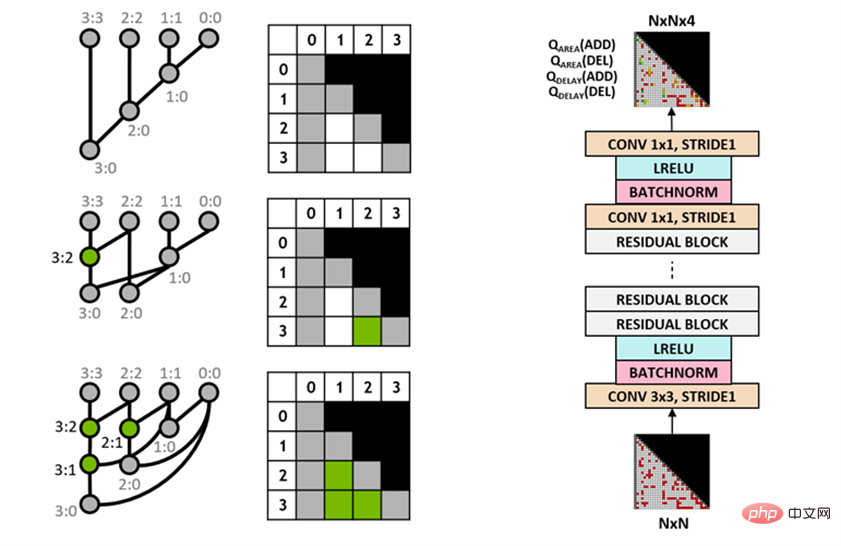

そこで問題は、AI エージェントは優れたプレフィックス マップを設計できるかということです。すべての接頭辞グラフの状態空間は非常に大きい O(2^n^n) であり、総当り的な方法を使用して探索することはできません。以下の図 2 は、4b 回線インスタンスを使用した PrefixRL の反復を示しています。

これらの物理合成の最適化により、最終的な回路プロパティ (遅延、面積、電力) は、元のプレフィックス グラフのプロパティ (レベルやノード数など) から直接変換されません。これが、AI エージェントがプレフィックス グラフの設計を学習しながら、プレフィックス グラフから生成された最終回路のプロパティを最適化する理由です。

研究者は、

算術回路設計を強化学習(RL)タスクとして扱い、エージェントは算術回路領域を最適化するように訓練されます。そして遅延特性。プレフィックス回線については、RL エージェントがプレフィックス グラフ内のノードを追加または削除し、次の手順を実行できる環境を設計しました。

- プレフィックス グラフは次のように正規化されます。常に正しいプレフィックス合計計算を維持します;

- #正規化されたプレフィックス グラフから回路を生成します;

- 物理合成ツールを使用して回路の物理合成最適化を実行します ;

- #回路の面積と遅延特性を測定します。

- 次のアニメーションでは、RL エージェントはノードを追加または削除することによって、プレフィックス グラフを段階的に構築します。各ステップで、エージェントは回路面積と遅延が改善されるという恩恵を受けます。

#元の画像はインタラクティブ バージョンです。

完全畳み込み Q 学習エージェント

研究者らは、Q 学習 (Q ラーニング) アルゴリズムを使用して、エージェントの回路設計をトレーニングします。以下の図 3 に示すように、プレフィックス グラフをグリッド表現に分解します。グリッド内の各要素はプレフィックス ノードに一意にマッピングされます。このグリッドは、Q ネットワークに使用される入力と出力を表します。入力グリッドの各要素は、ノードが存在するかどうかを表します。出力グリッドの各要素は、ノードの追加または削除の Q 値を表します。

Q 学習エージェントの入力と出力はグリッド表現であるため、研究者は完全な畳み込みニューラル ネットワーク アーキテクチャを使用しています。エリアと遅延の報酬はトレーニング中に個別に観察できるため、エージェントはエリアと遅延の属性の Q 値を個別に予測します。

図 3: 4b プレフィックス グラフ表現 (左) と完全畳み込み Q 学習エージェント アーキテクチャ (右)。

分散トレーニング用の Raptor

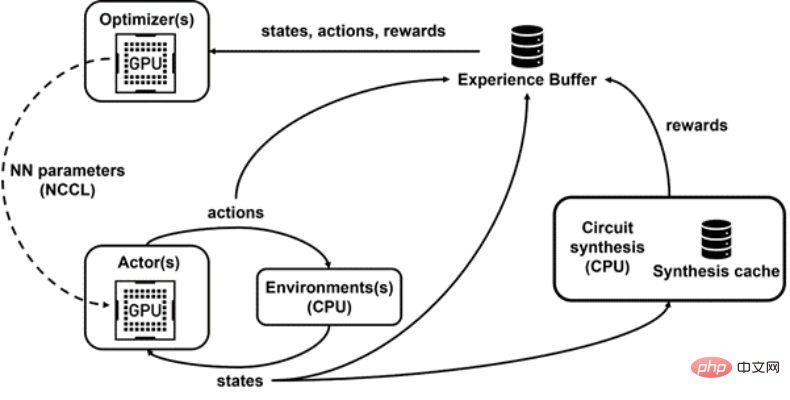

PrefixRL では多くの計算が必要です。物理シミュレーションでは、各 GPU に 256 個の CPU が必要で、64b タスクのトレーニングには 32,000 以上の CPU が必要です。 GPU時間。今回、NVIDIA は、NVIDIA のハードウェアの利点を最大限に活用し、この種の産業レベルの強化学習を実行できる分散強化学習プラットフォームである Raptor を社内で開発しました (下図 4)。

Raptor には、ジョブ スケジューリング、カスタム ネットワーク、GPU 対応データ構造など、トレーニング モデルのスケーラビリティと速度を向上させる機能があります。 PrefixRL のコンテキストでは、Raptor は CPU、GPU、スポット インスタンスにわたるハイブリッド割り当てを可能にします。この強化学習アプリケーションのネットワークは多様であり、次の利点があります:

- Raptor はモデルのピアツーピア転送のために NCCL 間を切り替えます パラメータは学習者から直接転送されますGPU から推論 GPU へ;

- #Redis は、報酬や統計などの非同期で小規模なメッセージに使用されます;

- JIT コンパイル済み RPC の場合、使用されますエクスペリエンス データのアップロードなど、大量かつ低遅延のリクエストを処理します。

最後に、Raptor は、マルチスレッド サービスを備えたリプレイ バッファーなどの GPU 対応のデータ構造を提供し、複数のワーカーからエクスペリエンスを受け取り、データを並列にバッチ処理して GPU にプリロードします。 。

以下の図 4 は、PrefixRL フレームワークが同時トレーニングとデータ収集をサポートし、NCCL を利用して参加者 (以下の図のアクター) に最新のパラメーターを効率的に送信することを示しています。

図 4: 研究者は、回路合成の遅延を克服するために、分離された並列トレーニングと報酬計算に Raptor を使用しています。

報酬計算研究者は、トレードオフの重み w (範囲は [0,1]) を使用して、面積目標と遅延目標を組み合わせます。彼らは、パレート フロンティアを取得するためにさまざまな重みを使用してさまざまなエージェントをトレーニングし、それによってエリアのバランスをとり、トレードオフを遅らせます。

RL 環境での物理合成最適化により、エリアとレイテンシをトレードオフするさまざまなソリューションを生成できます。研究者は、特定のエージェントのトレーニングに使用されるのと同じトレードオフの重みを使用して物理合成ツールを駆動します。

報酬計算のループ内で物理合成最適化を実行すると、次の利点があります:

- RL エージェントは、ターゲット テクノロジの最終回路特性を直接最適化する方法を学習します。ノードとライブラリ ;

- RL エージェントには、物理合成プロセス中にターゲット アルゴリズム回路の周辺ロジックが含まれるため、ターゲット アルゴリズム回路とその周辺ロジックのパフォーマンスを共同で最適化します。

ただし、物理合成の実行には時間がかかり (64b 加算器の場合は約 35 秒)、RL のトレーニングと探索が大幅に遅くなる可能性があります。

研究者らは、エージェントがアクションを実行するために必要なのは回路合成や以前の報酬ではなく、現在のプレフィックス グラフの状態のみであるため、報酬の計算を状態の更新から切り離しています。 Raptor のおかげで、アクター エージェントは待機することなく環境内で実行できる一方で、長時間の報酬計算を CPU ワーカーのプールにオフロードして物理合成を並行して実行できます。

CPU ワーカーが報酬を返すと、変換をリプレイ バッファーに埋め込むことができます。包括的な報酬は、状態が再び発生した場合の冗長な計算を避けるためにキャッシュされます。

結果と見通し

以下の図 5 は、PrefixRL と最先端の EDA ツールのパレート支配加算器回路を使用して設計された 64b 加算器回路の面積と遅延を示しています。

最高の PrefixRL 加算器は、同じレイテンシで EDA ツール加算器よりも 25% 少ない面積を達成します。物理合成の最適化後にパレート最適加算器回路にマッピングされたこれらのプレフィックス グラフは、不規則な構造を持っています。

図 5: PrefixRL によって設計された演算回路は、最新の技術によって設計された回路よりも小さい-art EDA ツールとより高速。

(左) 回路アーキテクチャ、(右) 対応する 64b 加算器回路特性図

ここまでご存知のとおり、これは深層強化学習エージェントを使用して算術回路を設計する最初の方法です。 NVIDIA は、AI を現実世界の回路設計の問題に適用し、アクション スペース、状態表現、RL エージェント モデルを構築し、複数の競合する目標に合わせて最適化し、報酬計算の遅さを克服するための青写真を構想しています。

以上がNVIDIA は AI を使用して GPU 演算回路を設計し、最先端の EDA と比較して面積を 25% 削減し、高速化と効率化を実現しています。の詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。

ホットAIツール

Undresser.AI Undress

リアルなヌード写真を作成する AI 搭載アプリ

AI Clothes Remover

写真から衣服を削除するオンライン AI ツール。

Undress AI Tool

脱衣画像を無料で

Clothoff.io

AI衣類リムーバー

Video Face Swap

完全無料の AI 顔交換ツールを使用して、あらゆるビデオの顔を簡単に交換できます。

人気の記事

ホットツール

メモ帳++7.3.1

使いやすく無料のコードエディター

SublimeText3 中国語版

中国語版、とても使いやすい

ゼンドスタジオ 13.0.1

強力な PHP 統合開発環境

ドリームウィーバー CS6

ビジュアル Web 開発ツール

SublimeText3 Mac版

神レベルのコード編集ソフト(SublimeText3)

ホットトピック

7677

7677

15

15

1393

1393

52

52

1207

1207

24

24

91

91

11

11

Web3トレーディングプラットフォームranking_web3グローバル交換トップ10の概要

Apr 21, 2025 am 10:45 AM

Web3トレーディングプラットフォームranking_web3グローバル交換トップ10の概要

Apr 21, 2025 am 10:45 AM

Binanceは、グローバルデジタルアセット取引エコシステムの大君主であり、その特性には次のものが含まれます。1。1日の平均取引量は1,500億ドルを超え、500の取引ペアをサポートし、主流の通貨の98%をカバーしています。 2。イノベーションマトリックスは、デリバティブ市場、Web3レイアウト、教育システムをカバーしています。 3.技術的な利点は、1秒あたり140万のトランザクションのピーク処理量を伴うミリ秒のマッチングエンジンです。 4.コンプライアンスの進捗状況は、15か国のライセンスを保持し、ヨーロッパと米国で準拠した事業体を確立します。

WorldCoin(WLD)価格予測2025-2031:WLDは2031年までに4ドルに達しますか?

Apr 21, 2025 pm 02:42 PM

WorldCoin(WLD)価格予測2025-2031:WLDは2031年までに4ドルに達しますか?

Apr 21, 2025 pm 02:42 PM

WorldCoin(WLD)は、独自の生体認証とプライバシー保護メカニズムを備えた暗号通貨市場で際立っており、多くの投資家の注目を集めています。 WLDは、特にOpenai人工知能技術と組み合わせて、革新的なテクノロジーを備えたAltcoinsの間で驚くほど演奏しています。しかし、デジタル資産は今後数年間でどのように振る舞いますか? WLDの将来の価格を一緒に予測しましょう。 2025年のWLD価格予測は、2025年にWLDで大幅に増加すると予想されています。市場分析は、平均WLD価格が1.31ドルに達する可能性があり、最大1.36ドルであることを示しています。ただし、クマ市場では、価格は約0.55ドルに低下する可能性があります。この成長の期待は、主にWorldCoin2によるものです。

通貨サークルでのレバレッジされた交換のランキングは

Apr 21, 2025 pm 11:24 PM

通貨サークルでのレバレッジされた交換のランキングは

Apr 21, 2025 pm 11:24 PM

2025年のレバレッジド取引、セキュリティ、ユーザーエクスペリエンスで優れたパフォーマンスを持つプラットフォームは次のとおりです。1。OKX、高周波トレーダーに適しており、最大100倍のレバレッジを提供します。 2。世界中の多通貨トレーダーに適したバイナンス、125倍の高いレバレッジを提供します。 3。Gate.io、プロのデリバティブプレーヤーに適し、100倍のレバレッジを提供します。 4。ビットゲットは、初心者やソーシャルトレーダーに適しており、最大100倍のレバレッジを提供します。 5。Kraken、安定した投資家に適しており、5倍のレバレッジを提供します。 6。Altcoinエクスプローラーに適したBybit。20倍のレバレッジを提供します。 7。低コストのトレーダーに適したKucoinは、10倍のレバレッジを提供します。 8。ビットフィネックス、シニアプレイに適しています

クロスチェーントランザクションとはどういう意味ですか?クロスチェーントランザクションとは何ですか?

Apr 21, 2025 pm 11:39 PM

クロスチェーントランザクションとはどういう意味ですか?クロスチェーントランザクションとは何ですか?

Apr 21, 2025 pm 11:39 PM

クロスチェーントランザクションをサポートする交換:1。Binance、2。Uniswap、3。Sushiswap、4。CurveFinance、5。Thorchain、6。1inchExchange、7。DLNTrade、これらのプラットフォームはさまざまな技術を通じてマルチチェーン資産トランザクションをサポートします。

なぜ仮想通貨価格の上昇または下落があるのですか?なぜ仮想通貨価格の上昇または下落があるのですか?

Apr 21, 2025 am 08:57 AM

なぜ仮想通貨価格の上昇または下落があるのですか?なぜ仮想通貨価格の上昇または下落があるのですか?

Apr 21, 2025 am 08:57 AM

仮想通貨価格の上昇の要因には、次のものが含まれます。1。市場需要の増加、2。供給の減少、3。刺激された肯定的なニュース、4。楽観的な市場感情、5。マクロ経済環境。衰退要因は次のとおりです。1。市場需要の減少、2。供給の増加、3。ネガティブニュースのストライキ、4。悲観的市場感情、5。マクロ経済環境。

カーネルエアドロップ報酬を獲得する方法バイナンスフルプロセス戦略

Apr 21, 2025 pm 01:03 PM

カーネルエアドロップ報酬を獲得する方法バイナンスフルプロセス戦略

Apr 21, 2025 pm 01:03 PM

暗号通貨の賑やかな世界では、新しい機会が常に現れます。現在、Kerneldao(Kernel)Airdropアクティビティは多くの注目を集め、多くの投資家の注目を集めています。それで、このプロジェクトの起源は何ですか? BNBホルダーはそれからどのような利点を得ることができますか?心配しないでください、以下はあなたのためにそれを一つ一つ明らかにします。

トップ10の暗号通貨交換プラットフォーム世界最大のデジタル通貨交換リスト

Apr 21, 2025 pm 07:15 PM

トップ10の暗号通貨交換プラットフォーム世界最大のデジタル通貨交換リスト

Apr 21, 2025 pm 07:15 PM

交換は、今日の暗号通貨市場で重要な役割を果たしています。それらは、投資家が取引するためのプラットフォームであるだけでなく、市場の流動性と価格発見の重要なソースでもあります。世界最大の仮想通貨交換はトップ10にランクされており、これらの交換は取引量がはるかに先を行っているだけでなく、ユーザーエクスペリエンス、セキュリティ、革新的なサービスに独自の利点を持っています。リストの上にある交換は通常、ユーザーベースが大きく、広範な市場の影響力があり、その取引量と資産タイプは、他の取引所で到達するのが難しいことがよくあります。

ハイブリッドブロックチェーン取引プラットフォームとは何ですか?

Apr 21, 2025 pm 11:36 PM

ハイブリッドブロックチェーン取引プラットフォームとは何ですか?

Apr 21, 2025 pm 11:36 PM

暗号通貨交換を選択するための提案:1。流動性の要件については、優先度は、その順序の深さと強力なボラティリティ抵抗のため、Binance、gate.ioまたはokxです。 2。コンプライアンスとセキュリティ、Coinbase、Kraken、Geminiには厳格な規制の承認があります。 3.革新的な機能、Kucoinのソフトステーキング、Bybitのデリバティブデザインは、上級ユーザーに適しています。