TeslaのスーパーコンピューティングチップはGPGPUを超えることができるでしょうか?

著者: Chen Wei 博士、ストレージとコンピューティング/GPU アーキテクチャと AI の専門家、上級専門職の称号。中関村クラウドコンピューティング産業同盟、中国光学工学協会の専門家、国際コンピュータ連盟(ACM)の会員、中国コンピュータ連盟(CCF)の専門会員。かつては AI 企業のチーフサイエンティストや、大手メモリチップメーカーの 3D NAND 設計責任者を務めたこともあり、主な業績には、国内初の高出力再構成可能ストレージおよびコンピューティング プロセッサ製品アーキテクチャが含まれます (プロトタイプの社内テストを完了しました)。大手インターネットメーカー)、初の医療用ドメイン特化AIプロセッサ(実装済み)、初のRISC-V/x86/ARMプラットフォーム対応AI加速コンパイラ(Alibaba Pingtouge/Xinlaiとの協力で実装済み)、中国初の3D NANDチップアーキテクチャとデザイン チームが設立され (Samsung とベンチマーク)、中国初の組み込みフラッシュ メモリ コンパイラ (TSMC とベンチマークされ、プラットフォーム レベルで適用されています)。

2022年9月の最終日、テスラの人工知能デーに、テスラの「オプティマスプライム」ロボットが正式にデビューしました。テスラのエンジニアによると、2022 年の人工知能の日は、テスラのロボットが外部サポートなしで「リリース」された初めての日です。 「彼は威厳を持って歩き、聴衆に向かって大まかな方向に向かって挨拶した。動作が若干もたつくことを除けば、その他は非常に自然です。

1 テスラロボットの力はその「内核」にある?

テスラは、オフィスの周りで「働く」ロボットのビデオを公開しています。オプティマス・プライムという名前のロボットは、物品を運んだり、植物に水を与えたり、工場内でしばらくの間自律的に働いたりもしました。テスラは「我々の目標は、有用な人型ロボットをできるだけ早く作ることだ」と述べ、ロボットを2万ドル未満、つまりテスラの電気自動車よりも安価にすることが目標だと付け加えた。

テスラのロボットが非常に強力である理由は、テスラ自身の AI 技術の蓄積だけではなく、主にテスラの強力な自社開発 AI チップによるものです。この AI チップは従来の CPU ではなく、ましてや GPU ではなく、より複雑な AI 計算に適した形式です。

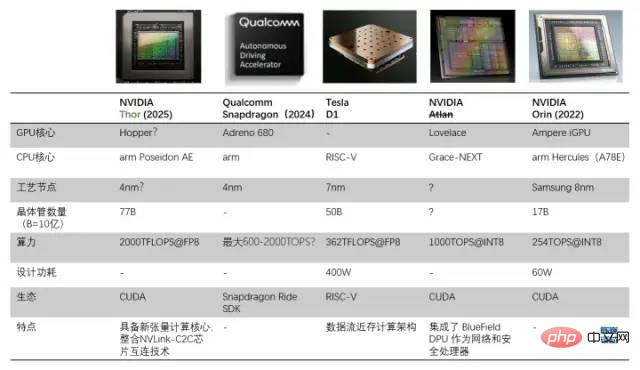

D1プロセッサと他の自動運転/ロボットプロセッサとの比較

1.1 データフローニアメモリアーキテクチャに基づき、GPUを超える汎用AIチップを作成

テスラは独自に構築このチップを使用する理由は、GPU がディープ ラーニング トレーニングを処理するように特別に設計されていないため、コンピューティング タスクにおいて GPU の効率が比較的低いためです。 Tesla と Dojo (Dojo はトレーニング モジュールの名前であり、カーネル アーキテクチャの名前でもあります) の目標は、「最高の AI トレーニング パフォーマンスを達成することです。より大規模で複雑なニューラル ネットワーク モデルを有効にして、高いエネルギー効率とコストを達成することです。テスラの標準は、将来的には GPU を使用する必要がなくなるように、他のどのコンピューターよりも人工知能コンピューティングに優れたコンピューターを構築することです。

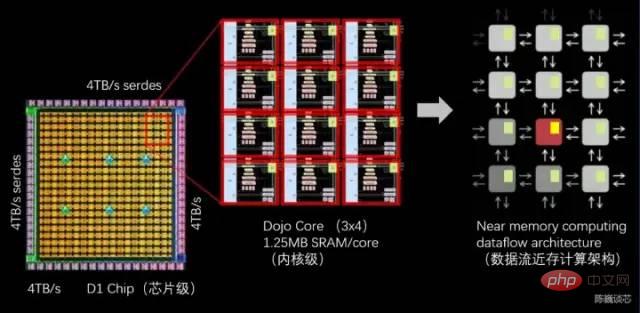

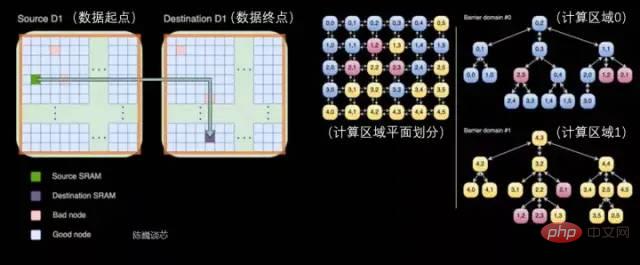

スーパーコンピューターを構築する際の重要なポイントは、高帯域幅 (困難) と低遅延 (非常に困難) を維持しながらコンピューティング能力を拡張する方法です。 Tesla が提供するソリューションは、強力なチップと独自のグリッド構造で構成される分散 2D アーキテクチャ (平面)、またはデータ フロー ニアメモリ コンピューティング アーキテクチャです。

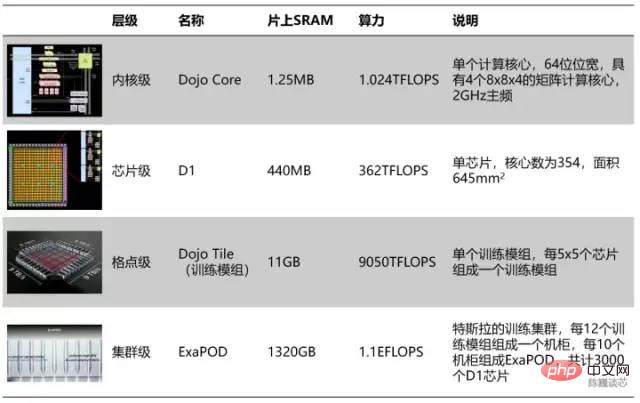

Tesla コンピューティング ユニットの階層分割

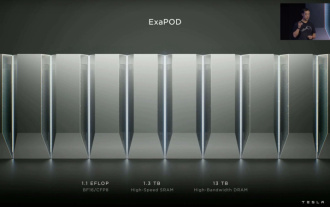

階層分割によると、354 個の Dojo コアごとに D1 チップが形成され、25 個のチップごとにトレーニング モジュールが形成されます。最後の 120 個のトレーニング モジュールは、合計 3,000 個の D1 チップを備えた一連の ExaPOD コンピューティング クラスターを形成します。

Tesla Dojo チップ トレーニング モジュールは 6 グループの GPU サーバーのパフォーマンスを達成できますが、コストは単一グループの GPU サーバーよりも低くなります。単一の Dojo サーバーの計算能力は 54PFLOPS に達することもありました。わずか 4 つの Dojo キャビネットで、4,000 個の GPU で構成される 72 個の GPU ラックを置き換えることができます。 Dojo は、通常数か月から 1 週間かかる AI コンピューティング (トレーニング) 作業を削減します。このような「大きなコンピューティング能力が奇跡を生む」という考え方は、テスラの自動運転スタイルと一致しています。明らかに、このチップはテスラの AI 技術の進歩も大きく加速します。

もちろん、このチップモジュールはまだ「完璧」のレベルに達していませんが、データフローニアメモリコンピューティングのアイデアを採用していますが、その計算能力とエネルギー効率の比率はそれを超えません。 GPU。 1 台のサーバーは電流が 2000A に達するなど、大量の電力を消費するため、特別にカスタマイズされた電源装置が必要です。 Tesla D1 チップはすでにニアメモリ コンピューティング アーキテクチャの構造的限界に達しています。テスラが「インメモリ コンピューティング」または「インメモリ ロジック」アーキテクチャを採用すると、おそらくチップのパフォーマンスまたはエネルギー効率が大幅に向上するでしょう。

Tesla Dojo チップサーバーは、12 個の Dojo トレーニング モジュール (2 層、各層に 6 個) で構成されています

1.2 Tesla の Dojo アーキテクチャ設計哲学

Dojo コアは、高スループットと 4-ウェイ行列計算ユニット (8x8) と 1.25 MB のローカル SRAM。ただし、Dojo コアのサイズは大きくありません。これに比べ、富士通の A64FX は同じプロセス ノード上で 2 倍以上の領域を占有します。

Dojo コアの構造を通して、一般的な AI プロセッサーに関する Tesla の設計哲学がわかります。

- 面積削減: Tesla は、AI のスループットを最大化するために、チップに多数のコンピューティング コアを統合します。コンピューティングを実現するには、計算能力を確保しながら単一コアの面積を可能な限り小さくし、スーパーコンピューティング システムにおける計算能力のスタックと遅延の間の矛盾をより適切に妥協する必要があります。

- キャッシュとレイテンシーの合理化: 領域のコンピューティング効率を最大化するために、Dojo カーネルは比較的控えめな 2 GHz (保守的なクロック回路は占有する領域が少なくなる傾向があります) で実行され、基本的な分岐予測子と小規模な命令のキャッシュのみを使用します。このような合理化されたアーキテクチャでは、必要なコンポーネントのみが保持されます。残りの領域は可能な限りベクトル計算ユニットと行列計算ユニットに任せられます。もちろん、カーネル プログラムのコード フットプリントが大きい場合、または分岐が多数ある場合、この戦略ではパフォーマンスがある程度犠牲になる可能性があります。

- 機能の合理化: 内部計算の実行に必要のないプロセッサー機能を削除することで、消費電力と面積の使用量をさらに削減します。 Dojo コアはデータ側のキャッシュを実行せず、仮想メモリーをサポートせず、正確な例外もサポートしません。

Tesla と Musk の場合、Dojo は道場のように形や配置されているだけでなく、その設計哲学も道場の精神と密接に関連しており、「少ないほど豊かである」プロセッサーの設計美学を完全に体現しています。

2 D1 コアは RISC-V アーキテクチャですか?

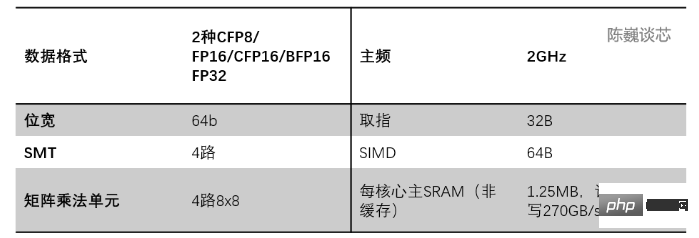

まずは各道場の構造と特徴を見てみましょう。

各 Dojo コアは、ベクトル計算/行列計算機能を備えたプロセッサーであり、完全な命令フェッチ、デコード、および実行コンポーネントを備えています。 Dojo コアは CPU に似たスタイルを持ち、GPU よりもさまざまなアルゴリズムやコードの分岐に適応できるようです。 D1 の命令セットは RISC-V に似ており、プロセッサは 2GHz で動作し、4 セットの 8x8 行列乗算演算ユニットを備えています。 AI 計算の高速化に重点を置いた一連のカスタム ベクトル命令も備えています。

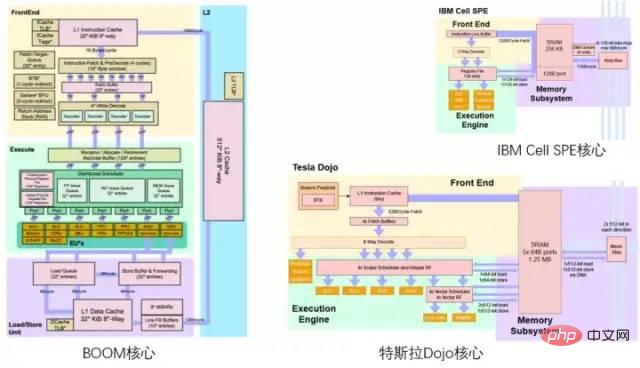

RISC-V 分野に詳しい人なら、Tesla の Dojo アーキテクチャ図の配色がバークレーの BOOM プロセッサ アーキテクチャ図に敬意を表しているようで、上部が黄色、下部が緑、上部が紫であることがおそらくわかるでしょう。ボトム。

Tesla DojoコアとBerkeley BOOM/IBM Cellコアの比較

2.1 D1コア全体のアーキテクチャ

D1コアの構造(青色の部分が追加/変更) ) 詳細)

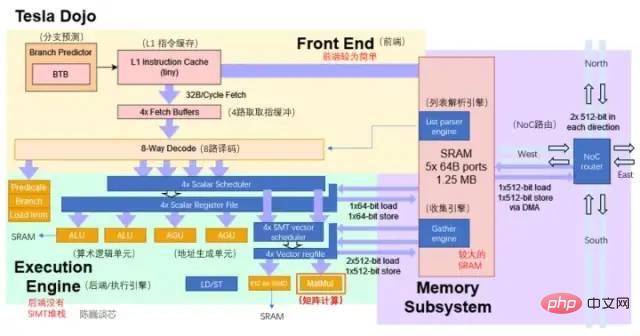

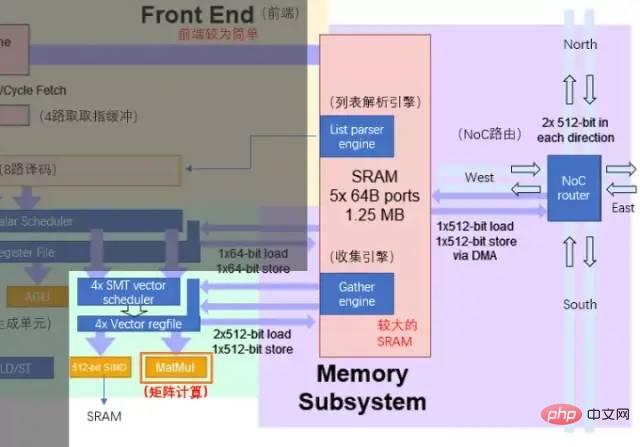

現在のアーキテクチャ図から判断すると、Dojo コアはフロントエンド、実行ユニット、SRAM、NoC ルーティングの 4 つの部分で構成されており、CPU と GPU の両方よりも少ない制御コンポーネントを備えています。 Tensor コアの行列演算ユニット。

Dojo のコア構造は BOOM よりも合理化されており、実行コンポーネントの使用率を向上させるための Rename などのコンポーネントがなく、仮想メモリのサポートも困難です。ただし、この設計の利点は、制御部分が占有する領域を削減し、チップ上のより多くの領域を演算実行ユニットに割り当てることができることです。各 Dojo コアは 1.024TFLOPS のコンピューティング能力を提供します。それぞれの計算能力のほぼすべてが行列計算ユニットによって提供されていることがわかります。したがって、マトリックス演算ユニットと SRAM は共同して D1 プロセッサの演算エネルギー効率比を決定します。

Dojoコアの主なパラメータ

- 分岐予測: GPU などの SIMT アーキテクチャと比較して、Dojo コアにはマルチスレッド分岐タスクを割り当てるための SIMT スタック コアがありません。ただし、Dojo コアには BTB (分岐ターゲット バッファ) があるため、D1 は単純な分岐予測を通じてパフォーマンスを向上させることができます。

BTB は、成功した分岐命令のアドレスとその分岐先アドレスをバッファに保存します。バッファは分岐命令のアドレスによって識別されます。パイプライン プロセッサにおけるブランチのパフォーマンス ペナルティは、ブランチのパスを予測し、ブランチで使用される情報をキャッシュすることで軽減できます。 - 命令キャッシュ: 小さい L1 命令キャッシュはコア内の SRAM に直接接続され、計算命令を取得します。

- 命令フェッチ: 各 Dojo カーネルには 32 B の命令フェッチ ウィンドウがあり、最大 8 つの命令に対応できます。

- デコーディング: 8 ウェイ デコーダーは、サイクルごとに 2 つのスレッドを処理できます。デコード フェーズでは、フェッチ バッファから命令を取得してデコードし、各命令の要件に従って必要な実行リソースを割り当てます。

- スレッド スケジューリング: より広範な 8 ウェイ デコードの後に、ベクトル スケジューラ (Scheduler) とレジスタ ファイル (Register File) があります。こちらはブランチ集約のマスク判定がないようで、実際のブランチ実行効率はGPUより若干低い可能性があります。 Tesla が強力なコンパイラを持っていることを願っています。

- 実行ユニット: 2 ウェイ ALU および 2 ウェイ AGU、ベクトル/行列計算用の 512 ビット SIMD および行列計算ユニット (それぞれ 512 ビットのベクトル計算と 4 ウェイ 8x8 行列乗算を実行) 。マトリックス演算ユニットは、D1 チップの主要な演算能力です。 (次項で詳しく紹介します)

- ALUとAGUは主に行列計算以外の少量の論理計算を担当します。 AGU はアドレス生成ユニットであり、主に SRAM を動作させ、他のコアのアドレスにアクセスするために必要なアドレスを生成するために使用されます。アドレス計算を残りの CPU と並行して実行することによって。

通常のCPUがさまざまな演算を実行するとき、メモリ(またはSRAM)からデータをフェッチするために必要なメモリアドレスを計算する必要があります。たとえば、CPU コアが実際のメモリ位置からデータを取得する前に、配列要素のメモリ位置を計算する必要があります。これらのアドレス生成計算には、加算、減算、モジュロ演算、ビット シフトなどのさまざまな整数演算が含まれます。メモリ アドレスの計算は、複数の一般的な機械語命令をコンパイルすることも、Tesla Dojo のような AGU ハードウェア回路を通じて直接実行することもできます。このようにして、さまざまなアドレス生成計算を ALU からオフロードできるため、AI 計算の実行に必要な CPU サイクル数が削減され、コンピューティング パフォーマンスが向上します。 - SIMD は主に、データの起動や蓄積などの特別な関数の計算を担当します。

- 行列計算ユニットは、Dojo の主要な計算コンポーネントであり、2 次元行列計算を担当し、畳み込み、Transformer およびその他の計算を実装します。

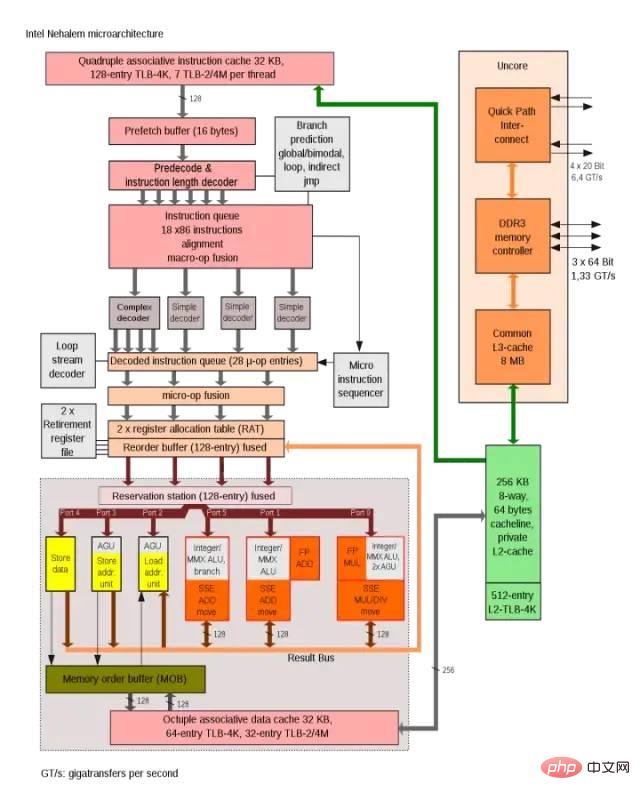

Intel Nehalem アーキテクチャは、AGU を使用してシングルサイクル アドレス アクセス効率を向上させています

Dojo コアの接続方法は、IBM の Cell プロセッサの SPE コア接続方法によく似ています。主な類似点は次のとおりです。

- D1 または SPE で実行されるコードはどちらもシステム メモリに直接アクセスできず、アプリケーションは主にローカル SRAM で動作します。

- メイン メモリ (DDR または HBM) からのデータが必要な場合は、DMA 操作が必要です。 D1 も Cell の SPE も仮想メモリをサポートしていません。

- 以下では、計算および行列乗算モジュールとカーネルのストレージを紹介します。

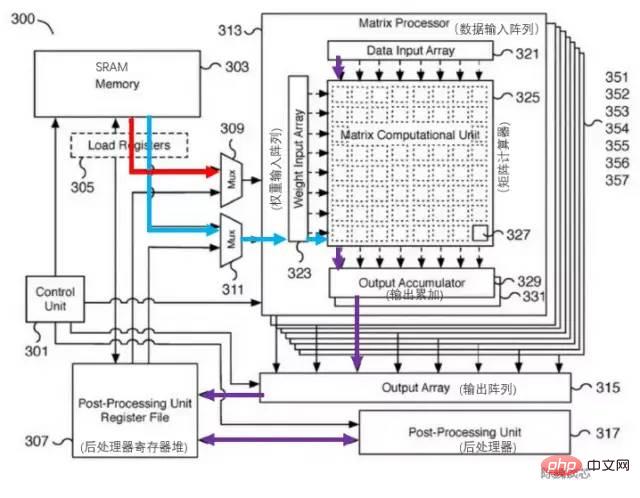

2.2 コンピューティングコア行列コンピューティングユニットとオンチップストレージ

Dojo アーキテクチャーのコンピューティング能力強化の中核は、行列コンピューティングユニットです。マトリックス演算ユニットとコア SRAM の間のデータ対話は、メイン コアのデータ転送電力消費を構成します。テスラ行列演算器の該当特許は以下の通りです。このモジュールの主要なコンポーネントは、8x8 行列-行列乗算ユニット (図では行列計算機と呼ばれます) です。入力はデータ入力配列と重み入力配列です。行列の乗算を計算した後、出力は直接累積されます。各 Dojo コアには、4 ウェイ 8x8 行列乗算ユニットが含まれています。

テスラ行列計算ユニットの特許

テスラ行列計算ユニットの特許

アーキテクチャ図には L1 キャッシュと SRAM が 1 つしかないため、Tesla がキャッシュ領域を節約し、レイテンシを短縮するために RISC-V のキャッシュ構造を合理化したのではないかと推測します。コアあたり 1.25MB の SRAM ブロックは、SIMD および行列コンピューティング ユニットに対して 2x512 ビット読み取り (AI 計算の重みとデータに対応) と 512 ビット書き込み帯域幅を提供できるほか、整数に対して 64 ビット読み取りおよび書き込み機能を提供します。レジスタファイル。計算の主なデータ フローは、SRAM から SIMD および行列乗算ユニットへです。

行列計算ユニットの主な処理フローは次のとおりです:

マルチプレクサ (Mux) を介して SRAM から重み入力配列 (Weight input array) に重みをロードし、SRAM からデータ入力配列 (データ入力) にデータをロードします。配列)。

入力データと重みは行列演算器(行列演算器)で乗算(内積か外積?)されます。

乗算演算結果は出力アキュムレータ(Output Accumulator)に出力され、累積されます。ここで計算する場合、行列の分割と結合により 8x8 を超える行列計算が可能になります。

蓄積された出力は、キャッシュ用のポストプロセッサーのレジスターファイルに渡され、後処理されます (アクティブ化、プーリング、パディングなどの操作を実行できます)。

計算プロセス全体は、CPUの介入なしに制御ユニット(Control Unit)によって直接制御されます。

実行ユニットとSRAM/NoC間のデータ対話

Dojoコア内のSRAMは非常に広い読み取りおよび書き込み帯域幅を備えており、400 GB/秒でロードでき、270 GB/秒でロードできます。書き込み速度。 Dojo コア命令セットには、NoC 経由でルーティングされる専用のネットワーク転送命令があり、D1 チップまたは Dojo トレーニング モジュール内の他のコアの SRAM メモリとの間でデータを直接移動できます。

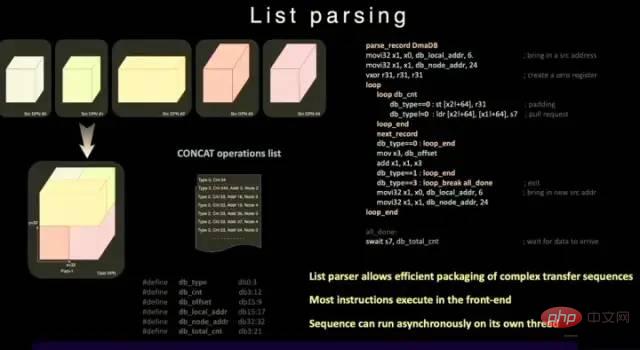

通常の SRAM とは異なり、Dojo の SRAM にはリスト パーサー エンジンと収集エンジンが含まれています。リスト解析機能は、D1 チップの重要な機能の 1 つです。リスト解析エンジンは、さまざまなデータ型の複雑な送信シーケンスをパッケージ化して、送信効率を向上させることができます。

リスト解析関数

演算遅延、面積、複雑さをさらに削減するために、D1は仮想メモリをサポートしていません。通常のプロセッサでは、プログラムが使用するメモリアドレスは物理メモリアドレスに直接アクセスするのではなく、オペレーティングシステムが設定したページング構造を利用してCPUによって物理アドレスに変換されます。

D1 コアでは、4 ウェイ SMT 機能により計算における明示的な並列処理が可能になり、AGU とアドレッシング計算方法が簡素化され、Tesla が十分に低いレイテンシで SRAM にアクセスできるようになります。その利点は、中間 L1 データ キャッシュを回避できることです。待ち時間。

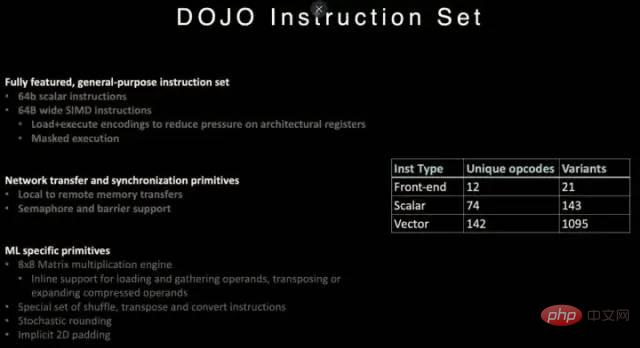

2.3 Dojo 命令セット

D1 プロセッサ命令セット

D1 は、RISC-V アーキテクチャの命令を参照し、いくつかの命令、特にベクトル計算に関連する命令をカスタマイズします。

D1 命令セットは、64 ビットのスカラー命令と 64 バイトの SIMD 命令、同期プリミティブを使用したネットワーク送信、および機械学習/深層学習 (8x8 行列計算など) に関連する特殊なプリミティブをサポートします。

ネットワークデータ送信と同期プリミティブに関しては、ローカルストレージ (SRAM) からリモートストレージにデータを送信するための命令プリミティブ (Primitives) に加え、セマフォ (Semaphore) とバリア制約 (Barrier Constraints) もサポートしています。これにより、D1 はマルチスレッドをサポートし、そのメモリ操作命令を複数の D1 コアで実行できるようになります。

機械学習と深層学習用に、Tesla はシャッフル、転置、変換などの数学的演算や、確率的丸めやパディング関連の命令を含む命令を定義しています。

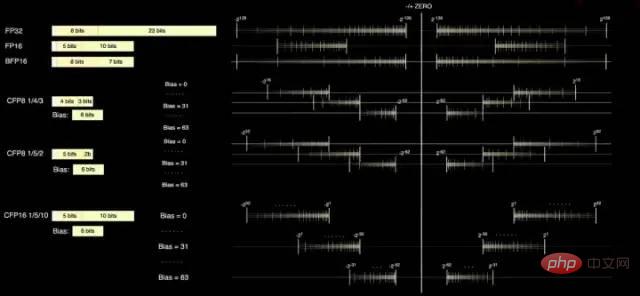

2.4 データ形式

D1 コアには、FP32 と FP16 という 2 つの標準的な計算形式があり、推論により適した BFP16 形式もあります。混合精度コンピューティングのパフォーマンス向上を達成するために、D1 は精度を低くし、スループットを高めるために 8 ビット CFP8 形式も使用します。

CFP8 を使用する利点は、ほぼ同じ計算能力を達成するためにより多くの乗算器スペースを節約できることであり、これは D1 の計算能力密度を高めるのに非常に役立ちます。

Dojo コンパイラーは、より広い範囲と精度をカバーするために、仮数部の精度を調整できます。いつでも最大 16 の異なるベクトル形式を使用できるため、コンピューティング能力を柔軟に向上できます。

D1プロセッサデータフォーマット

Teslaによって提供された情報によると、CFP8は行列乗算ユニット(CFP16フォーマットで保存)内の計算に使用できます。

3 Dojo アーキテクチャ プロセッサは GPU を超えることができますか?

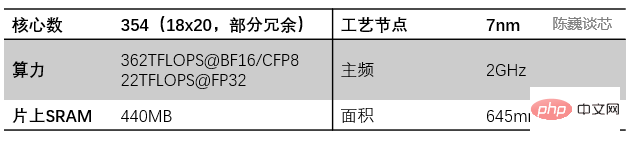

D1 プロセッサは TSMC によって製造され、7 ナノメートルの製造プロセスを使用しており、500 億個のトランジスタと 645mm² のチップ面積を持ち、これは NVIDIA の A100 (826 mm²) や AMD Arcturus (750 mm²) よりも小さいです。 。

3.1 Dojo データフローのニアメモリーコンピューティングアーキテクチャ

D1 プロセッサー構造

各 D1 プロセッサーは、18 x 20 Dojo コアのスプライシングで構成されています。各 D1 プロセッサーで使用できる Dojo コアは 354 個あります。 (360 個のコアのうち 354 個のみが使用される理由は、歩留まりとプロセッサーごとのコアの安定性を考慮したためです) TSMC によって製造され、7nm 製造プロセスを使用し、500 億個のトランジスターと 645mm² のチップ面積を備えています。

各 Dojo コアには、メインの重みおよびデータ ストレージとして 1.25MB SRAM が搭載されています。異なる Dojo コアはオンチップ ネットワーク ルーティング (NoC ルーティング) を介して接続され、異なる Dojo コアはデータ キャッシュを共有する代わりに、複雑な NoC ネットワークを介してデータ同期を実行します。 NoC は、ノード境界を越えて 4 方向 (南東、北西) で 8 パケットを各方向で 64 B/クロック サイクルで処理できます。つまり、4 方向すべてでメッシュに 1 つのパケット入力と 1 つのパケット出力を処理できます。各隣接する Dojo コア。 NoC ルーターは、サイクルごとに 1 回、コア内の SRAM への 64B 双方向読み取りおよび書き込みを実行することもできます。

D1 プロセッサー内のプロセッサー間転送とタスク分割

各 Dojo コアは、行列計算機能を備えた比較的完全な CPU のようなクラスです (各コアには個別の行列計算ユニットがあるため) 、フロントエンドは比較的小さいため、ここでは CPU ライクと呼ばれます)。そのデータ フロー アーキテクチャは、SambaNova の 2 次元データ フロー グリッド構造に似ています。データはメモリに戻ることなく、各処理コア間を直接流れます。

D1 チップは 2GHz で動作し、440MB の巨大な SRAM を搭載しています。 Tesla は、コンピューティング グリッド内の分散 SRAM に設計を集中させ、より高速でより近い多数のオンチップ ストレージとオンチップ ストレージ間の転送を通じてメモリへのアクセス頻度を減らし、それによってシステム全体のパフォーマンスを向上させます。データ フロー ストレージとコンピューティングの統合アーキテクチャ (データ フロー ニアメモリ コンピューティング) の明らかな特徴があります。

各 D1 チップには 576 個の双方向 SerDes チャネルが分散されており、片側帯域幅 4 TB/秒で他の D1 チップに接続できます。

D1プロセッサチップの主なパラメータ

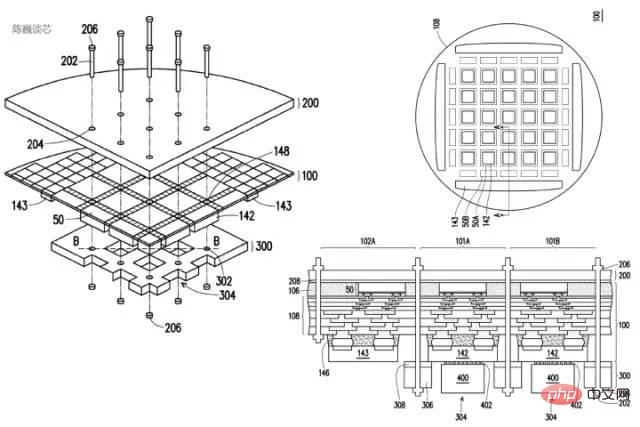

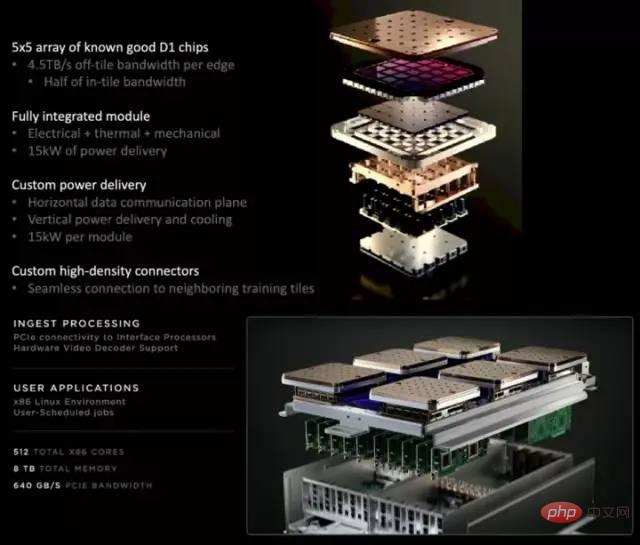

3.2 Dojoトレーニングモジュールのチップレットパッケージング相互接続技術

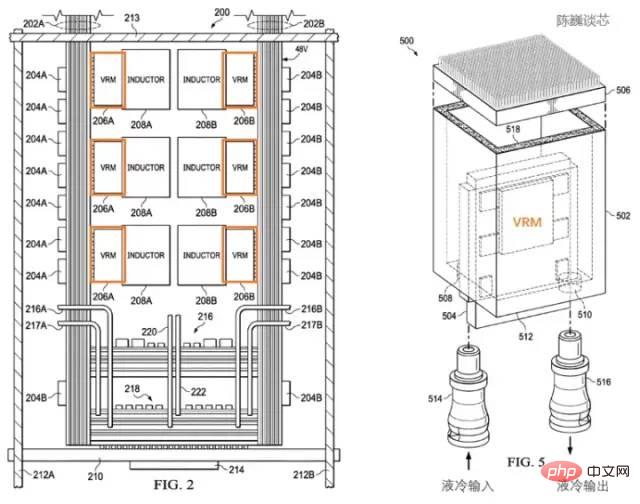

各D1トレーニングモジュールは、2つの相互接続された5x5 D1チップアレイによって配置されます。立体的なメッシュ構造。オンチップのクロスコアSRAMは驚異の11GBに達し、当然消費電力も驚異の15kWに達します。エネルギー効率比は0.6TFLOPS/W@BF16/CFP8です。 (計算が間違っていればいいのですが、そうでない場合、このエネルギー効率比は実際には理想的ではありません)。外部 32GB 共有 HBM メモリ。 (HBM2e または HBM3)

Tesla D1プロセッサーの特許取得済みの放熱構造

Teslaは、専用の電力調整モジュール(VRM)と放熱構造を使用して消費電力を管理しています。ここでの電力消費管理の主な目的は 2 つあります:

不必要な電力損失を削減し、エネルギー効率を向上させることです。

熱変形によるプロセッサモジュールの故障を軽減します。

テスラの特許によると、電力調整モジュールがチップ自体に対して垂直になっており、これによりプロセッサープレーンが占有する面積が大幅に削減され、液体冷却を通じてプロセッサーの温度のバランスを迅速に調整できることがわかります。

Tesla D1プロセッサの特許取得済みの放熱とパッケージング構造

トレーニングモジュールはInFO_SoW(シリコンオンウェハー)パッケージングを使用してチップ間の相互接続密度を高めます。 TSMC の INFO_SoW テクノロジーに加えて、このパッケージはプロセッサ モジュールの故障を軽減するために Tesla 独自の機械的パッケージング構造も使用しています。

各トレーニング モジュールの外側エッジにある 40 個の I/O チップは、合計 36 TB/秒の帯域幅、または 10 TB/秒のスパン帯域幅を実現します。トレーニング モジュールの各層は、超高速ストレージ システムに接続されています。640 GB の実行メモリは、18 TB/秒を超える帯域幅に加えて、1 TB/秒を超えるネットワーク スイッチング帯域幅を提供できます。

データ伝送方向はチップ平面と平行で、電源と液冷の方向はチップ平面と垂直です。これは非常に美しい構造設計であり、さまざまなトレーニング モジュールを相互接続できます。 3次元構造により、チップモジュールの電源領域が節約され、コンピューティングチップ間の距離が可能な限り短縮されます。

Dojo POD キャビネットは、コンピューティング トレイとストレージ システムの 2 層で構成されます。パレットの各レベルには 6 つの D1 トレーニング モジュールがあります。 2 つのフロアにある 12 個のトレーニング モジュールで構成されるキャビネットは、108PFLOPS のディープラーニング コンピューティング能力を提供できます。

Dojo モジュールと Dojo POD キャビネット

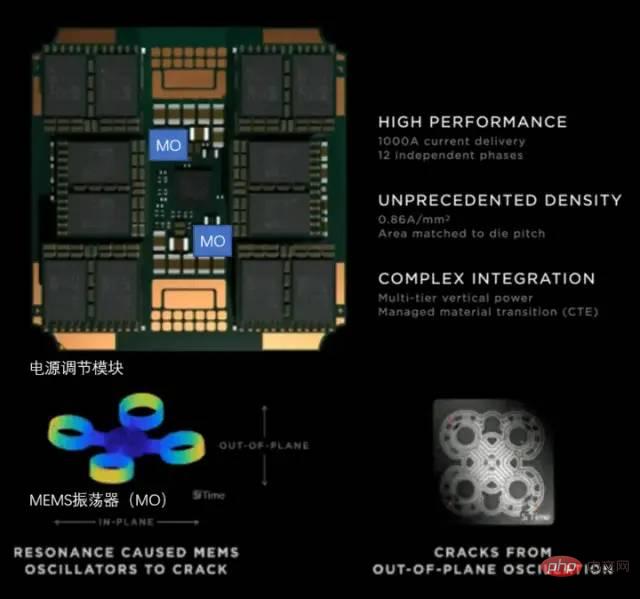

3.3 電源管理と放熱制御

スーパーコンピューティング プラットフォームの放熱は、スーパーコンピューティング システムのレベルを測る上で常に重要な要素でした。

D1 チップの熱設計能力

Tesla は、Dojo POD 上で完全に自社開発した VRM (電圧調整モジュール) を使用しており、単一の VRM で 52 V の電圧と 1000 A を超える巨大な電流を供給できます。現在の目標は 0.86 A です。平方ミリメートルあたり、合計 12 の独立した電源フェーズを備えています。

Tesla のパワーコンディショニングモジュール

高密度チップの熱放散では、熱膨張係数 (CTE) の制御に重点が置かれています。 Dojo システムのチップ密度は非常に高いため、CTE がわずかに制御不能になると、構造の変形や破損が発生し、接続障害が発生する可能性があります。

Tesla の自社開発 VRM は、過去 2 年間で 14 のバージョンを繰り返し、MEMS 発振器 (MO) を使用して電力調整モジュールの熱変形を検知し、最終的に CTE インジケーターの内部要件を完全に満たしました。 MEMS技術を利用して電源をアクティブに調整するこの方法は、ロケット本体の振動を制御するアクティブ調整方法と似ています。

3.4 Dojo アーキテクチャー・プロセッサーのコンパイル・エコロジー

D1 プロセッサー・ソフトウェア・スタック

D1 などの AI チップの場合、コンパイル・エコロジーはチップ自体と同じくらい重要です。

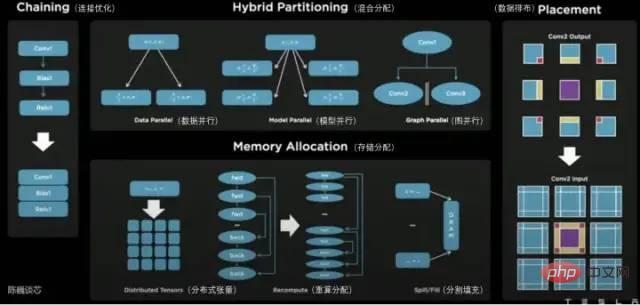

D1 プロセッサ プレーンでは、D1 は行列演算ユニットに分割されます。コンパイル ツール チェーンは、タスクの分割とデータ ストレージの構成を担当し、さまざまな方法できめ細かい並列コンピューティングを実行してストレージの使用量を削減します。

Dojo コンパイラーによってサポートされる並列メソッドには、データ並列処理、モデル並列処理、およびグラフ並列処理が含まれます。サポートされているストレージ割り当て方法には、分散テンソル、再計算された割り当て、分割フィルが含まれます。

コンパイラー自体は、ループやグラフ最適化アルゴリズムなど、さまざまな CPU で一般的に使用される動的制御フローを処理できます。 Dojo コンパイラーを使用すると、ユーザーは Dojo 大規模分散システムを全体的な設計とトレーニングのアクセラレーターとして扱うことができます。

ソフトウェア エコシステム全体の最上位層は PyTorch に基づいており、最下位層は Dojo ドライバーに基づいており、Dojo コンパイラーと LLVM は中間で使用されてコンパイル層を形成しています。ここに LLVM を追加すると、Tesla はコンパイルの最適化のために LLVM 上のさまざまな既存のコンパイル エコシステムをより適切に利用できるようになります。

Tesla Dojo Compiler

4 結論

Tesla AI Day を通して、私たちは Tesla AI Day を通して、Tesla ロボットの真の本体とその強力な「内核」をより多くの認識で見ました。

Tesla の Dojo コアは、これまでの CPU や GPU のアーキテクチャとは異なり、CPU の特性を組み合わせた合理化された GPU と言え、そのコンパイルも CPU と GPU とは大きく異なるものになると思います。コンピューティング密度を高めるために、テスラは非常に効率的な最適化を行い、アクティブに調整される電力管理メカニズムを提供しました。

Tesla Dojo アーキテクチャは単に道場と呼ばれるだけでなく、その設計は手段としてのシンプルさ、より少ないものよりも多くのものに基づいています。このアーキテクチャは、CPU と GPU に次ぐ、コンピューティング チップ アーキテクチャのもう 1 つの典型的な形式になるでしょうか?様子を見ましょう。

以上がTeslaのスーパーコンピューティングチップはGPGPUを超えることができるでしょうか?の詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。

ホットAIツール

Undresser.AI Undress

リアルなヌード写真を作成する AI 搭載アプリ

AI Clothes Remover

写真から衣服を削除するオンライン AI ツール。

Undress AI Tool

脱衣画像を無料で

Clothoff.io

AI衣類リムーバー

AI Hentai Generator

AIヘンタイを無料で生成します。

人気の記事

ホットツール

メモ帳++7.3.1

使いやすく無料のコードエディター

SublimeText3 中国語版

中国語版、とても使いやすい

ゼンドスタジオ 13.0.1

強力な PHP 統合開発環境

ドリームウィーバー CS6

ビジュアル Web 開発ツール

SublimeText3 Mac版

神レベルのコード編集ソフト(SublimeText3)

ホットトピック

7445

7445

15

15

1374

1374

52

52

76

76

11

11

14

14

6

6

Tesla Dojo のスーパーコンピューティング デビュー、マスク氏: 年末までに AI をトレーニングするためのコンピューティング能力は、NVIDIA H100 GPU 8,000 個とほぼ同等になるでしょう

Jul 24, 2024 am 10:38 AM

Tesla Dojo のスーパーコンピューティング デビュー、マスク氏: 年末までに AI をトレーニングするためのコンピューティング能力は、NVIDIA H100 GPU 8,000 個とほぼ同等になるでしょう

Jul 24, 2024 am 10:38 AM

7 月 24 日のこの Web サイトのニュースによると、テスラ CEO イーロン マスク (イーロン マスク) は、本日の決算電話会議で、同社が 2,000 台の NVIDIA H100 を搭載するこれまでで最大の人工知能トレーニング クラスターを完成させようとしていると述べました。 GPU。マスク氏はまた、同社の決算会見で投資家に対し、NvidiaのGPUは高価であるため、テスラはDojoスーパーコンピューターの開発に取り組むと語った。このサイトは、マスク氏のスピーチの一部を次のように翻訳しました: Dojo を通じて NVIDIA と競争する道は困難ですが、私たちは今、NVIDIA に過度に依存しています。 NVIDIA の観点からすると、市場が耐えられるレベルまで GPU の価格を引き上げるのは必然ですが、

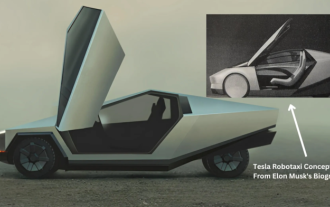

テスラがついに行動を起こす!自動運転タクシーは間もなく発表されるでしょうか? !

Apr 08, 2024 pm 05:49 PM

テスラがついに行動を起こす!自動運転タクシーは間もなく発表されるでしょうか? !

Apr 08, 2024 pm 05:49 PM

4月8日のニュースによると、テスラのCEOイーロン・マスク氏は最近、テスラが自動運転車技術の開発に取り組んでいることを明らかにし、待望の無人自動運転タクシー「ロボタクシー」が8月8日に正式デビューすると発表した。データ編集者は、マスク氏の発言が次のことであることを知った。以前ロイターは、テスラの自動車運転計画はロボタクシーの生産に焦点を当てていると報じた。しかし、マスク氏はこれに反論し、ロイター通信が低価格車の開発計画を中止し、再び虚偽の報告書を発表したと非難し、一方、低価格車のモデル2とロボタックスの開発は明らかになったと明らかにした。

テスラ サイバートラックが崖から飛び降りて挑む、限界を超えたパワーショー!

Mar 07, 2024 pm 09:28 PM

テスラ サイバートラックが崖から飛び降りて挑む、限界を超えたパワーショー!

Mar 07, 2024 pm 09:28 PM

3月7日のニュースによると、アメリカのユタ州の小さな町でテスラ・サイバートラックが「地獄の復讐への道」に挑戦する動画がこのほどインターネット上で公開された。クリフは米国ユタ州ソルトレイクシティにあり、アウトドア愛好家に人気の場所です。ここには 30 以上のオフロードロードがあり、険しい険しい岩壁に多くのエクストリーム オフロード愛好家が挑戦します。動画では、テスラ サイバートラックが45度近いV字渓谷に挑戦した際、3つのモーターの強力なパワーを頼りに着実に坂道を登り、ついに頂上に到達することに成功した様子が収められています。登りでは、滑りやすい岩の表面にもかかわらず、サイバートラックは滑ることなく順調に走行しました。編集者の理解によると、テスラ サイバートラックのモデルはシングルモーターのリアに分けられます。

テスラの新型モデル3高性能バージョンが韓国認証を通過、パワーパラメータが公開され注目を集めた

Mar 06, 2024 pm 08:49 PM

テスラの新型モデル3高性能バージョンが韓国認証を通過、パワーパラメータが公開され注目を集めた

Mar 06, 2024 pm 08:49 PM

3月6日のニュースによると、メディアは最近、テスラの新しいモデル3高性能バージョンが韓国の関連認証に合格し、一連の注目すべきパワーパラメータを公開したことを明らかにした。この新型車には、フロントに3D3誘導非同期モーター、リアに4D2永久磁石同期モーターを搭載した先進のデュアルモーターシステムが搭載され、これら2つが連携して驚異的なパワーを発揮するという。具体的には、フロントモーターは 215 馬力、リアモーターは最大 412 馬力を供給し、車両の総出力は驚異的な 461kW になります。リアの 4D2 モーターだけの出力は約 303kW です。この新型車のモーター設計は、速度が 110km/h に達するとピーク出力に達することができるため、高速走行時の新型モデル 3 のパフォーマンスが向上します。

テスラのFSD技術がドイツを驚かせ、自動運転は将来有望

Apr 29, 2024 pm 01:20 PM

テスラのFSD技術がドイツを驚かせ、自動運転は将来有望

Apr 29, 2024 pm 01:20 PM

4月29日のニュースによると、テスラは最近、待望の完全自動運転FSD技術をドイツで初めて公の場でデモンストレーションし、FSD技術の欧州市場への正式参入を示した。デモンストレーションイベント中に、スウェーデン運輸省上級顧問のリカルド・フレドリクソン氏が体験する機会がありました。彼はテスラ モデル Y に乗り、FSD(完全自動運転)の利便性を自ら体験しました。ドイツの道路でのパフォーマンス。フレドリクソン氏は、Apple の自動車プロジェクトで製品安全関連の役職を歴任しており、自動運転技術について深い理解を持っています。フレドリクソンの運転支援システムを体験してみると、FSD+12の運転はスムーズで自然だ。彼はまた、ミュンヘン市内中心部から空港に移動するときのことについても特に言及しました。

テスラ サイバートラックの量産は明るい兆し、テキサス工場の航空写真で壮大な生産状況が明らかに

Mar 15, 2024 pm 12:04 PM

テスラ サイバートラックの量産は明るい兆し、テキサス工場の航空写真で壮大な生産状況が明らかに

Mar 15, 2024 pm 12:04 PM

テスラの最新の純電気ピックアップトラック「サイバートラック」の生産進捗が注目を集めている。テスラは目立たないようにしていたが、ジェフ・ロバーツというテスラ観察者が撮影したテキサス・ギガファクトリーの最近の航空ビデオは、サイバートラック生産の前向きな兆候を外の世界に明らかにしているようだ。ビデオによると、テキサス州のテスラ ギガファクトリーにはすでに 300 台以上のサイバートラックがさまざまなエリアに分散されています。今回の台数の多さは、同工場でこれまでに見つかったサイバートラックの中で最多であり、同モデルの量産が急速に進んでいることを示している。これは、テスラがサイバートラックの生産において大幅な進歩を遂げたことを示しています。テスラは以前、Cybertr について懸念を表明していましたが、

テスラの2024年第1四半期財務報告書が発表:収益減少、低価格モデルの生産が議題に

Apr 24, 2024 pm 06:16 PM

テスラの2024年第1四半期財務報告書が発表:収益減少、低価格モデルの生産が議題に

Apr 24, 2024 pm 06:16 PM

4月24日のニュースによると、テスラは本日2024年第1四半期の財務報告書を公開した。報告書によると、テスラは同四半期に213億100万米ドルの収益を達成したが、これは前年同期と比べて9%減少した。この数字は市場アナリスト予想の223億ドルを若干下回った。同時に、純利益は11億2,900万米ドルとなり、前年同期比55%の大幅な減少となった。テスラは自動車販売で大きな成功を収めている。第1四半期の全世界での納車台数は38万6,800台で、市場の事前予想である約43万台を大幅に下回った。配送量は前年同期比8.3%減、前期比20.1%減と大幅に減少した。テスラにとって納車台数が前年比で減少するのは2020年以来初めて。速度を落とすために

テスラの上海エネルギー貯蔵ギガファクトリーは年内に試運転開始され、エネルギー貯蔵規模は40GWh近くと推定される

Mar 22, 2024 pm 12:32 PM

テスラの上海エネルギー貯蔵ギガファクトリーは年内に試運転開始され、エネルギー貯蔵規模は40GWh近くと推定される

Mar 22, 2024 pm 12:32 PM

上海未来産業実験区の建設は「1周年」を迎え、臨港新区管理委員会ハイテク部門責任者の陸裕氏が主催した記者会見で、待望のテスラエネルギー貯蔵装置に関する重要な情報が発表された。プロジェクトが明らかになりました。 Lu Yu氏によると、プロジェクトは年内に試作を完了する予定で、生産規模は40GWh近くになる見込みだという。このニュースは広く注目を集めており、テスラのエネルギー貯蔵プロジェクトは地元産業の発展と再生可能エネルギーの利用にとって非常に重要な意味を持つ。世界的に有名な電気自動車メーカーとして、テスラのエネルギー貯蔵分野への参加は大きな注目を集めています。上海と協力することで、臨港新区におけるテスラのエネルギー貯蔵プロジェクトの建設は、地元の産業レベルと技術革新能力の向上に貢献します。 Lu Yu氏はさらに、新エネルギー分野における臨港市の他の進歩についても紹介した。彼は言及した