Microsoft AR/VR 特許は、時間多重共振ドライブを使用してバイポーラ電源を生成することを提案しています

(Nweon 2023 年 7 月 5 日) XR ヘッドセットの顔追跡ソリューションを使用して、ユーザーの皮膚の小さな動きを感知できます。解決策の一例では、ヘッドセットは、異なる場所に配置された複数の感知アンテナ用の回路を備えていてもよい。アンテナ信号は LC 共振回路に入力され、LC ドライバーによって共振するように駆動されます。 LC共振回路の出力はセンスアンプに供給され、適切な信号をアナログデジタルコンバータADCに提供し、アナログデジタルコンバータADCは、さらなる処理のために検知信号をデジタル領域に変換できます。

しかし、LC共振駆動回路の従来の実装では、携帯機器の一般的なバッテリーと比較して比較的高い電力レベルが必要になる場合があります。 LC 共振回路の検出信号の振幅は、アナログ - デジタル変換プロセス中に可能な全体的なダイナミック レンジと分解能を最大化するために、可能な限り大きくする必要があるためです。

また、インダクタは回路内でかさばる部品であるため、コンパクトなフォームファクタを実現するには、システム全体で使用される部品の総数を減らす必要があります。

さらに最適化するために、Microsoft は、「双極性電源を生成するための時間多重共振駆動方式」という特許出願で、時間多重共振駆動方式を使用して双極性電源を生成できることを提案しました。

LC 共振駆動回路は常に動作する必要はなく、特定の動作モードでのみ動作する必要があります。たとえば、RF顔検出方式では、センサーが感知信号を取得すると、LC共振駆動回路をある期間でアクティブにし、その後別の期間でインダクタをバイポーラ電源に再利用できます。 、それによってインダクタの時間多重化スキームを採用します。時間多重化方式は、ハーフブリッジ共振器と同じ回路モジュールを共有するのに役立ちます。

センサー ソリューション用の従来の LC 共振駆動回路では、より高い電源電圧が必要です。これは、より高い分解能を達成するには、検出信号の振幅をできるだけ大きくする必要があるためです。したがって、マイクロソフトは、バイポーラ電源を生成する時間多重共振駆動スキームがセンサーを実装する最良の方法の 1 つである可能性があると考えています。

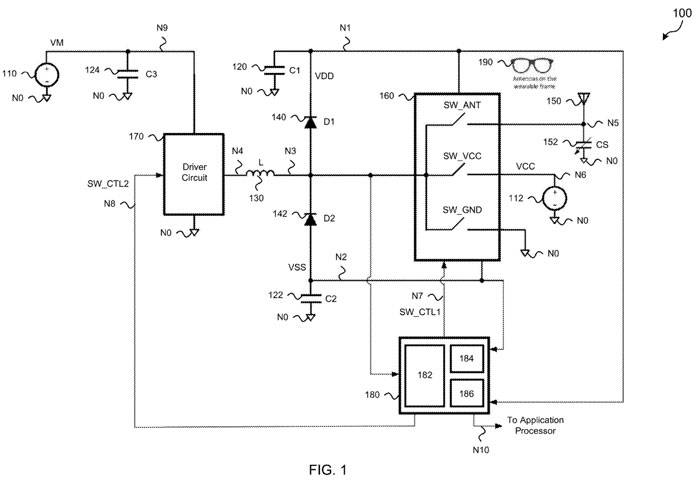

####バッテリ110は、ノードN9とノードN0との間に結合され、ノードN9のVMに対応するバッテリ電圧を供給する。 DC電源112は、ノードN6とノードN0との間に結合され、ノードN6に電圧VCCを供給する。第1の容量回路120は、C1で示されるノードN1とノードNOとの間に結合される。第2の容量回路122は、ノードN2とノードN0との間に接続され、ノードN0はC2に設定される。第3の容量回路124は、C3で示されるノードN9とノードN0との間に結合される。

####インダクタ回路130は、ノードN3とノードN4との間に結合され、1と名付けられる。第1のダイオード回路140は、ノードN3とノードN1との間に結合され、D1で示される。第2のダイオード回路142は、ノードN2とノードN3との間に結合され、D2で示される。アンテナ150はノードN5に結合され、感知コンデンサ152に対応する特性容量を有する。#### 検出コンデンサ152は、ノードN5とノードN0との間に結合され、CSで示される。 MUX160は、ノードN3に入力ポート、ノードN5に第1出力ポート、ノードN6に第2出力ポート、ノードN0に第3出力ポート、ノードN1に第1電力ポート、ノードN2に第1電力ポートを含む。ノード N7 の電源ポートと制御ポート。

#### 駆動回路170は、ノードN4の出力ポート、ノードN9の第1の電力ポート、ノードN0の第2の電力ポート、およびノードN8の制御ポートを含む。コントローラ回路180は、ノードN1に第1の入力ポート、ノードN2に第2の入力ポート、ノードN3に第3の入力ポート、ノードN7に第1の出力ポート、ノードN8に第2の出力ポート、ノードN8に第3の出力ポートを含む。 N10。MUX 160は、駆動回路170と協働して、ノードN3のインダクタ回路130の、ノードN7のアンテナ150、ノードN6のDC電源112、または回路接地への充電および放電時間を効果的に多重化する。ノードNO.

#### 検出コンデンサ152は、ノードN5とノードN0との間に結合された可変容量値CSを有するコンデンサとして表される。物理的な容量成分として示されているが、感知容量152はアンテナ150の特性容量に対応する。アンテナはウェアラブルフレーム900上に物理的に配置されているため、アンテナの実際の静電容量値は、ユーザーの皮膚への近接度に基づいて変化することになる。

####誘導回路130は、ドライバ回路170の出力とアンテナ150との間に事実上直列に結合される。ノードN4からインダクタ回路130を通って感知コンデンサ152まで、LCフィルタ回路を識別することができる。####コントローラ回路180は、マイクロコントローラユニットMCUとして実装され得る。 MCUは、ソフトウェアまたはファームウェア命令を通じて構成することができ、時分割多重方式に従って回路100の動作を制御する。このソリューションには、正方向充電 (第 1 モード)、負方向充電 (第 2 モード)、およびアンテナを顔の動き検出用のセンサーとして動作させる (第 3 モード) という 3 つの基本モードが含まれています。

###第1のモードでは、コントローラ回路180は、第2の制御信号SW_CTL2を通じて駆動回路170の第1の構成を活性化する。第2の制御信号は、ノードN4がバッテリ電圧VMに効果的に対応するようにノードN4をノードN9に結合する。### また、この第1のモードでは、コントローラ回路180は、第1の制御信号SW_CTL1をパルスして、MUX160の第3のスイッチ回路を介してノードN3を選択的に結合するMUX160の第1のスイッチ構成を変調する。パルスハイ期間中、ノードN3をノードN0に接続する回路は接地され、ノードN4からノードN3までのインダクタ回路130を正方向に充電させる。

パルスロー期間中、ノードN3はノードNOから切り離され、インダクタ回路130からの蓄積電流が第1ダイオード回路140を通って流れ、電荷が第1コンデンサ回路120(C1)に転送される。時間の経過とともに、繰り返されるパルスにより、ノードN1に正の電源電圧VDDを生成するのに十分な電荷が第1のコンデンサ回路120(C1)に蓄積される。

####第2のモード中、コントローラ回路180は、第2の制御信号SW_CTL2を通じて駆動回路170の第2の駆動構成を活性化する。制御信号は、ノードN4が回路接地に効果的に対応するように、ノードN4をノードN0に結合する。### さらに、第2のモードでは、コントローラ回路180は、第1の制御信号SW_CTL1を通じてMUX160の第2のスイッチ構成をパルス変調し、スイッチは、MUX160内の第2のスイッチ回路を通じてMUX160を選択的に切り替える。ノードN3はノードN6に結合される。パルスハイ期間中、ノードN3はノードN6でDC電源112に結合され、インダクタ回路130をノードN3からノードN4へ負の方向に充電させる。

パルスのロー期間中、ノードN3はノードN6から切り離され、インダクタ回路130からの蓄積電流が第2ダイオード回路140を通って流れ、第2コンデンサ回路122(C2)に電荷を供給する。時間の経過とともに、反復パルスにより、ノードN2に負の電源電圧VSSを生成するのに十分な電荷が第2のコンデンサ回路122(C2)に蓄積される。

###第3のモードでは、コントローラ回路180は、第1の制御信号SW_CTL1を通じてMUX160の第3のスイッチ構成を選択する。スイッチは、MUX160内の第1のスイッチ回路スイッチを介してノードN3をノードN5に結合する。### また、第3のモードにおいて、コントローラ回路180は、第2の制御信号SW_CTL2を通じて駆動回路170を選択的に活性化する。第2の制御信号は、ノードN9とノードN0との間に結合された変調ノードN4をパルス化する。この第3のモードでは、誘導回路130はアンテナ150およびその特性検知コンデンサ152(CS)に結合され、LC共振回路を形成する。

ノード N9 とノード NO の間のノード N4 の結合をパルス変調することにより、LC 共振回路が励起されて、ノード N3 で観察可能な発振信号を生成します。この発振信号は、顔の追跡に使用できます。第 1 および第 2 モードで事前に生成された二重電源電圧 (VDD、VSS) はさまざまな回路の動作に使用され、LC 共振回路は第 3 モードで励起されます。 LC フィルタの High-Q 共振特性に基づいて、過渡応答はノード N3 の AC 信号に対応します。

####コントローラ回路180は、ノードN3から感知された信号を捕捉するように構成することができ、その後、この信号をデジタル信号としてノードN10に提供し、さらなる処理のために他のシステムに提供することができる。 LC フィルタの高 Q 特性により、検出信号のピークツーピーク電圧が大きくなる場合があります。したがって、コントローラ回路180によって評価される前に信号サイズをスケールダウンするために追加の回路が必要になる場合がある。図 1 は、DC 電圧供給の生成と、バッテリ電源を使用するポータブル システムに適した RF 顔動き検出用の DC-AC コンバータの両方として使用される二重目的のインダクタ構成を示しています。

Microsoft は、提案されたシステムには高品質係数の LC フィルター (または共振器) が含まれており、LC フィルターはユーザーの感知アンテナと顔の皮膚によって形成される感知コンデンサーと組み合わせた直列誘導回路を使用していると述べています。 LCフィルタは、無線周波数顔追跡システムの共振周波数でAC電源のAC電圧を増幅するように構成されている。

説明したスキームの重要な側面は、顔追跡システムが回路の複雑さの軽減によって恩恵を受けることです。

LC フィルターの共振周波数は、アンテナの検出容量が変化すると変化します。これは、アンテナの位置に対する顔の動きに応じて変化します。特定の固定入力周波数の場合、LC フィルター出力信号のゲインと位相は、検出された静電容量の変化の関数として変化します。 LC フィルタの共振周波数におけるピーク ゲインと高い Q により、比較的小さな入力信号で非常に大きな出力信号を実現できます。

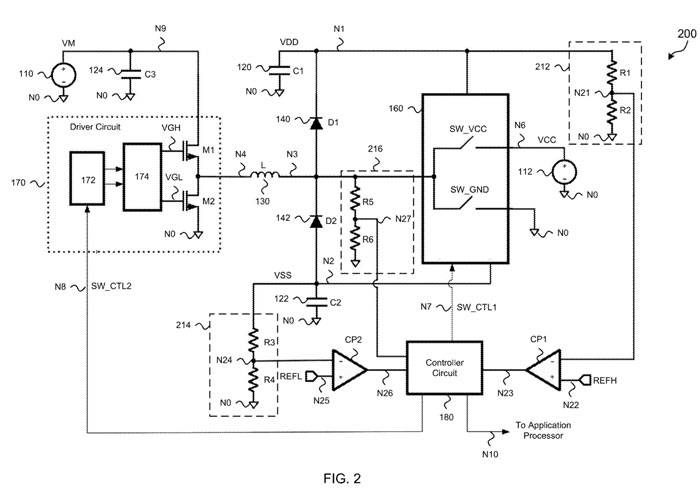

図 1 と比較すると、図 2 のシステムには 2 つの比較器 CP1 および CP2 と、3 つの分圧器またはスケーリング回路 (212、214、および 216) が含まれています。第1分圧回路212は、ノードN1とノードN0との間に直列に接続された2つの抵抗R1、R2を含み、第1分圧回路の出力はノードN21に相当する。

####第1の比較器CP1は、ノードN21に結合された反転入力(-)、ノードN22に結合された非反転入力()、およびノードN23に結合された出力を含む。第2の分圧回路214は、ノードN2とノードN0との間に直列に接続された2つの抵抗器R3、R4を含み、第2の分圧回路の出力はノードN24に対応する。

第2の比較器CP2は、ノードN24に結合された反転入力(-)、ノードN25に結合された非反転入力()、およびノードN26に結合された出力を含む。第3の分圧回路216は、ノードN3とノードN0との間に直列に接続された2つの抵抗器R5、R6を含み、第2の分圧回路の出力はノードN27に対応する。

上で説明した分圧回路は、入力ノードの対応する 1 つからの電圧を、さらなる処理に適したレベルまで下げるように構成されています。例えば、抵抗器R1およびR2からなる第1の分圧回路は、ノードN1の電圧を検出し、ノードN21で検出された電圧のスケーリングされたバージョンを生成する。

同様に、抵抗 R3 と R4 で構成される 2 番目の分圧回路はノード N2 で電圧を検出し、検出された電圧のスケーリングされたバージョンをノード N24 に生成しますが、抵抗 R5 と R6 で構成される 3 番目の分圧回路はコンバータ回路です。ノードN3の電圧を感知し、感知された電圧のスケーリングされたバージョンをノードN27に生成する。

コンパレータ CP1 および CP2 は、入力の対応する電圧が目標電圧に達したときを検出するように構成されています。例えば、第1比較器CP1は、ノードN21の感知電圧と第1基準電圧REFHを比較し、ノードN23に信号を生成する。

同様に、ノードN24の感知電圧を第2の基準電圧REFLと比較し、ノードN26に信号を生成するように第2の比較器CP2を構成する。

コントローラ回路180は、ノードN23およびN26からの信号を入力として使用して、インダクタ回路130の充電時間およびデューティサイクルを制御する。

###第3の分圧回路216の出力は、ノードN27においてコントローラ回路180の入力に結合されることが示されている。この入力は、ノード N3 で検出された電圧のスケーリングされたバージョンに対応します。動作中、ノードN3の電圧は、図1に示すようなインダクタ130と感知コンデンサ152から構成されるLC共振回路などのLC共振回路の応答を表すことができる。ノードN27で測定されるLC共振回路の応答は、コントローラ回路180内のADC184によってデジタル値に変換され得る。### 駆動回路170の詳細な実装も図2に示されており、論理ブロック172、ゲート駆動ブロック174、電界効果トランジスタM1、および電界効果トランジスタM2を含む。論理ブロック172は、ノードN8に結合された入力ポートと、ゲートドライバブロック174に結合された一対の出力とを含む。ゲートドライバブロック177は、FET M1のゲートに結合された第1の出力(VGH)と、FET M2のゲートに結合された第2の出力(VGL)とを含む。

FET M1は、ノードN9に結合されたドレインとノードN4に結合されたソースの両方を含む。 FET M2は、ノードN4に結合されたドレインと、ノードN0に結合されたソースの両方を含む。動作上、ノードN8の信号は、駆動回路170を介したインダクタの充電のタイミングおよびデューティサイクルを制御する単一の制御信号または複数の制御信号を表すことができる。

#### 図3は、図1および図2に使用される例示的なシステムなど、例示的な時間多重共振駆動スキームの過渡応答を示す。図3には、二重電源(VDD、VSS)の電圧波形、駆動回路170のハイおよびローゲート制御信号(VGH、VGL)、多重化回路160の第1および第2のスイッチ制御信号、およびフローが含まれる。インダクタ回路130の電流波形。

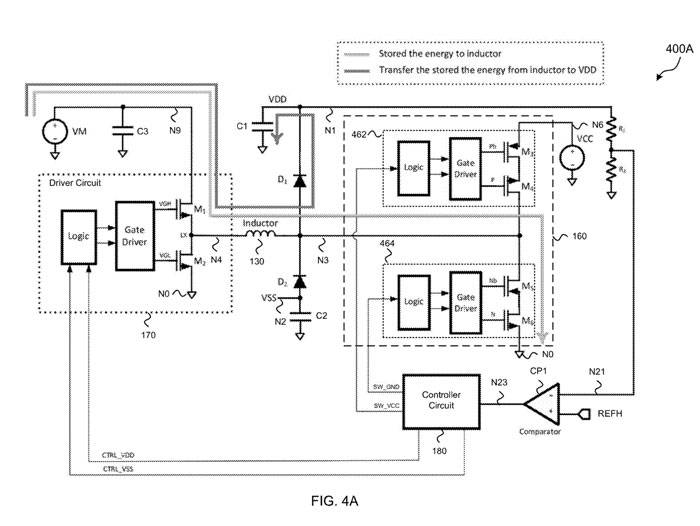

図4Aは、LC共振回路でバイポーラ電力を生成するための時間多重共振駆動方式の第3の例の動作の最初の部分を示しています。

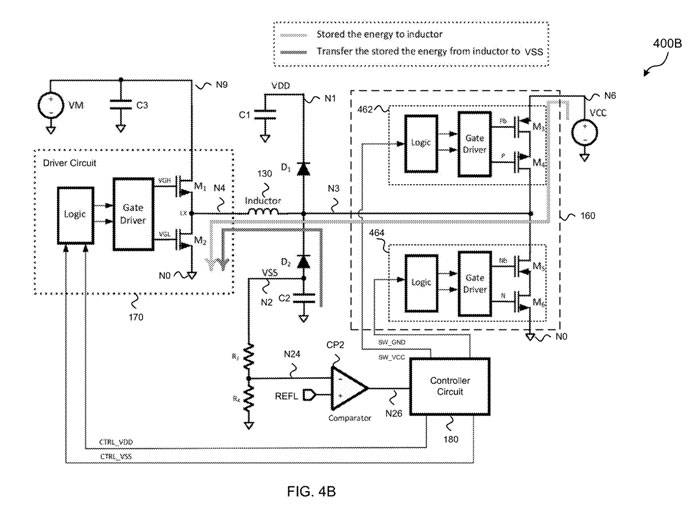

図4Bは、LC共振回路においてバイポーラ電力を生成するための時間多重共振駆動方式の第3の例の動作の第2の部分を示す。

#### 図2、図4Aおよび図4Bは、第1の電界効果トランジスタおよび第2の電界効果トランジスタがn型電界効果トランジスタを含むことを示している。バイポーラ電源(VDD、VSS)は、マルチプレクサの動作によってDC電圧源および接地に接続された2つのスイッチを備えたハーフブリッジ共振器としてのドライバ回路170の動作によって生成することができる。当初、コンデンサ C1 または C2 は電荷を蓄積できない可能性があるため、ノード N1 および N2 の電源電圧 VDD および VSS は要件を満たさない可能性があります。比較器CP1は、ノードN21の第1分圧器(R1、R2)の出力を介してノードN1の電圧を正の基準電圧REFHと比較し、ノードN23に比較器出力を生成する。

コンパレータ CP2 (ノード N24 の第 2 分圧器 (R3、R4) の出力を介して、ノード N2 の電圧を負の基準電圧 REFL と比較し、ノード N26 にコンパレータ出力を生成します。 ####コントローラ回路180は、ノードN23およびN26の電圧を評価し、電圧が期待値にあるかどうかを判断し、電源の充電プロセスを開始するための1つまたは複数の制御信号を生成する。

図 4A に示すように、ノード N1 の電源 VDD が低すぎる場合、ハーフブリッジ共振器のハイサイド FET M2 がアクティブになり (VGH がハイなど)、ローサイド FET M2 がアクティブになります。が非アクティブ化され、それによって正の電源が生成されます。次に、制御信号は、スイッチング回路464を制御して、インダクタ回路130のノードN3をノードN0に結合する回路接地に使用される。

####スイッチ回路464が閉状態にあるとき、電流はバッテリVMから駆動回路を通ってノードN4でインダクタ回路130に流れ、ノードN3はスイッチを介してノードN0で回路グランドに結合される。インダクタ回路130は事実上順方向であり、電流を蓄積する。

スイッチ回路464が開回路状態にあるとき、インダクタ回路130の電流に蓄えられたエネルギーはダイオード回路D1を介してノードN1に流れ、コンデンサC1はノードN1に電荷を蓄え、それに応じて電源電圧 VDD が増加します。この変調の複数のサイクルにわたって、正電源VDDの値は、所望の正電圧レベルに達するまで増加し、コンパレータCP1がトリップして、所望のレベルに到達したことをコントローラ回路180に通知する。正電源VDDが所望の値に達すると、ドライバ回路170のハイサイドスイッチングFET M1がコントローラ回路180によって非活性化される。

図 4B に示すように、ノード N2 の電力 VSS が高すぎると、ハーフブリッジ共振器のローサイド FET M2 がアクティブになり、ハイサイド FET M1 が非アクティブになり、負の電力が発生します。供給。次に、制御信号は、スイッチング回路462をインダクタ回路130のノードN3からノードN6のDC電源またはVCCに変調するために使用される。

####スイッチ回路462が閉状態にあるとき、電流はノードN6のDC電源VCCからノードN3のインダクタ回路130を通って流れ、ノードN4は駆動回路170およびインダクタ回路130を介してノードN0の回路接地に結合される。効果的に反転して電流を蓄積します。####スイッチ回路462が開回路状態にあるとき、インダクタ回路130の蓄積電流は、接地ノードN0から流れ、コンデンサC2およびダイオード回路D1を通ってノードN3に到達する。ノード N3 では、インダクタのエネルギーがコンデンサ C2 に伝達され、それによって電源電圧 VSS が低下します。

この変調の複数のサイクルにわたって、負電源VSSの値は、必要な負電圧供給レベルに達するまで減少し、コンパレータCP2がトリップして、必要レベルに達したことをコントローラ回路180に通知する。負電源VSSが所望の値になると、ドライバ回路170のローサイドスイッチングFET M2がコントローラ回路180によって非活性化される。

関連特許

: Microsoft 特許 | 双極性電源を生成する時間多重共振駆動スキーム

「双極性電源を生成するための時間多重共振駆動スキーム」というタイトルの Microsoft 特許出願は、もともと 2021 年 12 月に提出され、最近米国特許商標庁によって公開されました。

以上がMicrosoft AR/VR 特許は、時間多重共振ドライブを使用してバイポーラ電源を生成することを提案していますの詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。

ホットAIツール

Undresser.AI Undress

リアルなヌード写真を作成する AI 搭載アプリ

AI Clothes Remover

写真から衣服を削除するオンライン AI ツール。

Undress AI Tool

脱衣画像を無料で

Clothoff.io

AI衣類リムーバー

AI Hentai Generator

AIヘンタイを無料で生成します。

人気の記事

ホットツール

メモ帳++7.3.1

使いやすく無料のコードエディター

SublimeText3 中国語版

中国語版、とても使いやすい

ゼンドスタジオ 13.0.1

強力な PHP 統合開発環境

ドリームウィーバー CS6

ビジュアル Web 開発ツール

SublimeText3 Mac版

神レベルのコード編集ソフト(SublimeText3)

ホットトピック

7467

7467

15

15

1376

1376

52

52

77

77

11

11

18

18

19

19

カーソルAIでバイブコーディングを試してみましたが、驚くべきことです!

Mar 20, 2025 pm 03:34 PM

カーソルAIでバイブコーディングを試してみましたが、驚くべきことです!

Mar 20, 2025 pm 03:34 PM

バイブコーディングは、無限のコード行の代わりに自然言語を使用してアプリケーションを作成できるようにすることにより、ソフトウェア開発の世界を再構築しています。 Andrej Karpathyのような先見の明に触発されて、この革新的なアプローチは開発を許可します

2025年2月のトップ5 Genai発売:GPT-4.5、Grok-3など!

Mar 22, 2025 am 10:58 AM

2025年2月のトップ5 Genai発売:GPT-4.5、Grok-3など!

Mar 22, 2025 am 10:58 AM

2025年2月は、生成AIにとってさらにゲームを変える月であり、最も期待されるモデルのアップグレードと画期的な新機能のいくつかをもたらしました。 Xai’s Grok 3とAnthropic's Claude 3.7 SonnetからOpenaiのGまで

オブジェクト検出にYolo V12を使用する方法は?

Mar 22, 2025 am 11:07 AM

オブジェクト検出にYolo V12を使用する方法は?

Mar 22, 2025 am 11:07 AM

Yolo(あなたは一度だけ見ています)は、前のバージョンで各反復が改善され、主要なリアルタイムオブジェクト検出フレームワークでした。最新バージョンYolo V12は、精度を大幅に向上させる進歩を紹介します

ChatGpt 4 oは利用できますか?

Mar 28, 2025 pm 05:29 PM

ChatGpt 4 oは利用できますか?

Mar 28, 2025 pm 05:29 PM

CHATGPT 4は現在利用可能で広く使用されており、CHATGPT 3.5のような前任者と比較して、コンテキストを理解し、一貫した応答を生成することに大幅な改善を示しています。将来の開発には、よりパーソナライズされたインターが含まれる場合があります

Google' s Gencast:Gencast Mini Demoを使用した天気予報

Mar 16, 2025 pm 01:46 PM

Google' s Gencast:Gencast Mini Demoを使用した天気予報

Mar 16, 2025 pm 01:46 PM

Google Deepmind's Gencast:天気予報のための革新的なAI 天気予報は、初歩的な観察から洗練されたAI駆動の予測に移行する劇的な変化を受けました。 Google DeepmindのGencast、グラウンドブレイク

chatgptよりも優れたAIはどれですか?

Mar 18, 2025 pm 06:05 PM

chatgptよりも優れたAIはどれですか?

Mar 18, 2025 pm 06:05 PM

この記事では、Lamda、Llama、GrokのようなChatGptを超えるAIモデルについて説明し、正確性、理解、業界への影響における利点を強調しています(159文字)

O1対GPT-4O:OpenAIの新しいモデルはGPT-4Oよりも優れていますか?

Mar 16, 2025 am 11:47 AM

O1対GPT-4O:OpenAIの新しいモデルはGPT-4Oよりも優れていますか?

Mar 16, 2025 am 11:47 AM

OpenaiのO1:12日間の贈り物は、これまでで最も強力なモデルから始まります 12月の到着は、世界の一部の地域で雪片が世界的に減速し、雪片がもたらされますが、Openaiは始まったばかりです。 サム・アルトマンと彼のチームは12日間のギフトを立ち上げています

クリエイティブプロジェクトのための最高のAIアートジェネレーター(無料&有料)

Apr 02, 2025 pm 06:10 PM

クリエイティブプロジェクトのための最高のAIアートジェネレーター(無料&有料)

Apr 02, 2025 pm 06:10 PM

この記事では、トップAIアートジェネレーターをレビューし、その機能、創造的なプロジェクトへの適合性、価値について説明します。 Midjourneyを専門家にとって最高の価値として強調し、高品質でカスタマイズ可能なアートにDall-E 2を推奨しています。