本サイトの 8 月 22 日のニュースによると、インテルは先進プロセスの研究開発に積極的に投資すると同時に、先進パッケージング事業も強化しており、現在マレーシアのペナンに最新のパッケージング工場を建設し、その生産性を強化しているとのことです。 2.5D/3Dパッケージレイアウト。

同社は、2025 年までに 3D Foveros パッケージングの生産能力を 4 倍にする計画だと発表しました。インテル副社長のロビン・マーティン氏は本日ペナンでのインタビューで、ペナンの新工場が将来同社最大の3D先進パッケージング拠点となることを明らかにした。

インテルは、2021年に71億米ドル(本サイト注:現在約517億5,900万元)を投資して、ペナン州バヤンレパスにインテルが運営する新たな大手半導体パッケージング工場を建設すると発表しました。

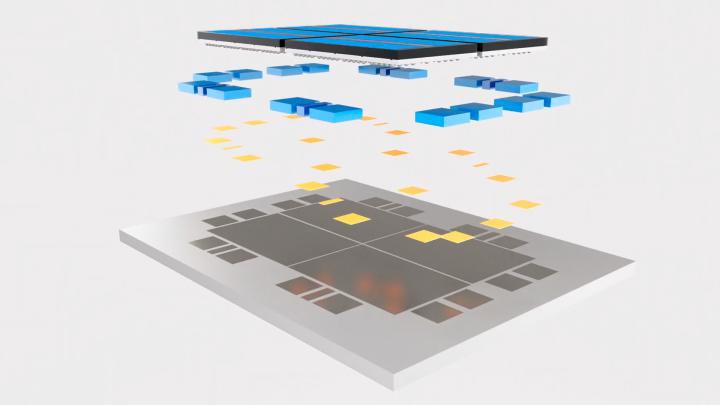

Intel によると、チップのパッケージングはプロセッサとマザーボード間の物理インターフェイスとして機能し、製品レベルのパフォーマンスにおいて重要な役割を果たします。役割。高度なパッケージング テクノロジにより、さまざまなコンピューティング エンジンによるマルチプロセス テクノロジの統合が容易になり、システム アーキテクチャにおける新しい手法の採用が容易になります。

レポートによると、インテルの Foveros パッケージング テクノロジは 3D スタックを使用して論理ペアリングを実現します。設計者は、新しいデバイス フォーム ファクタでテクノロジ IP ブロックとさまざまなメモリおよび入出力要素を柔軟に組み合わせることができます。製品は、I/O、SRAM、および電源供給回路がベースチップに製造され、その上に高性能ロジックチップレットまたはタイルが積層された、より小さなチップレットまたはタイルに分割できます。さらに、インテルの新しいパッケージング機能により、新しい設計が可能になります。 EMIB と Foveros テクノロジーを組み合わせて、さまざまなチップレットとブロックを相互接続して、基本的に単一チップと同等のパフォーマンスを実現します。 Intel は、Foveros Omni を使用することで、設計者はパッケージ内の小型チップやブロックを活用することで通信の柔軟性を高めることができると述べています。

以上がインテルは 2025 年までに 3D Foveros パッケージング能力を 4 倍にする計画の詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。