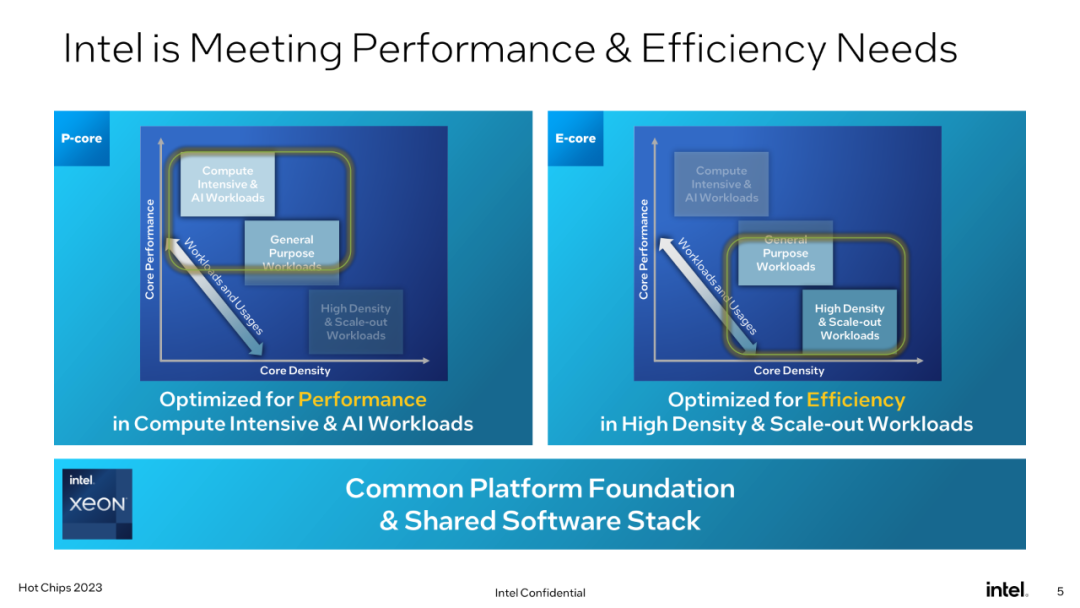

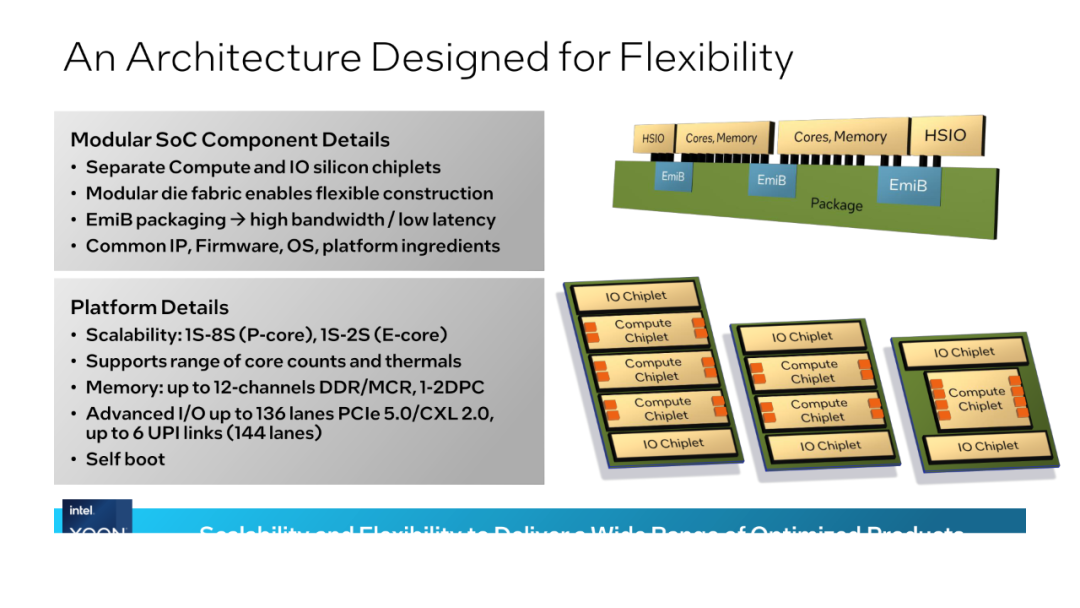

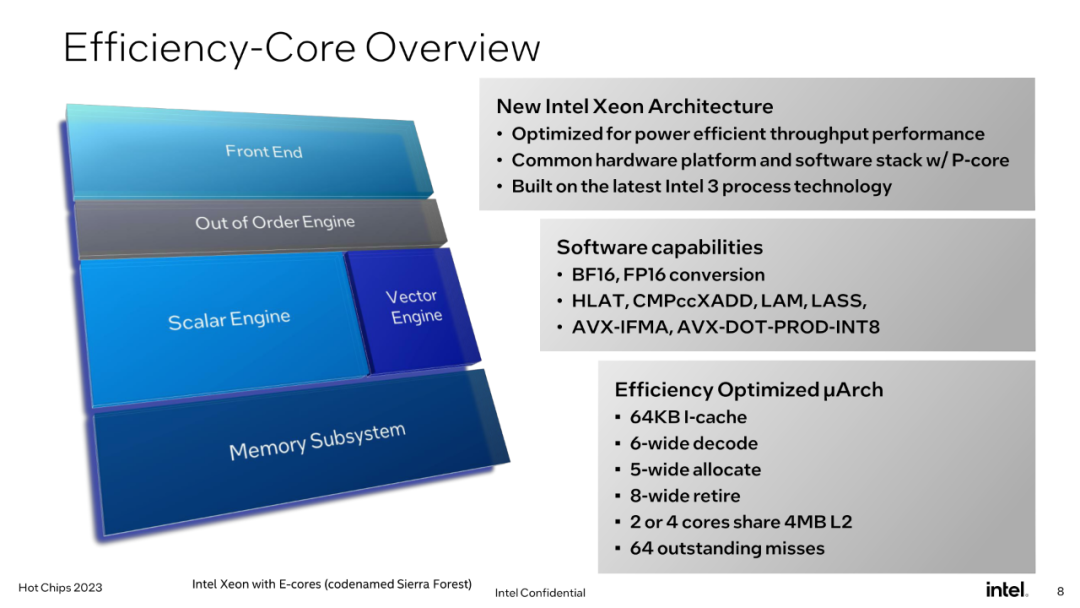

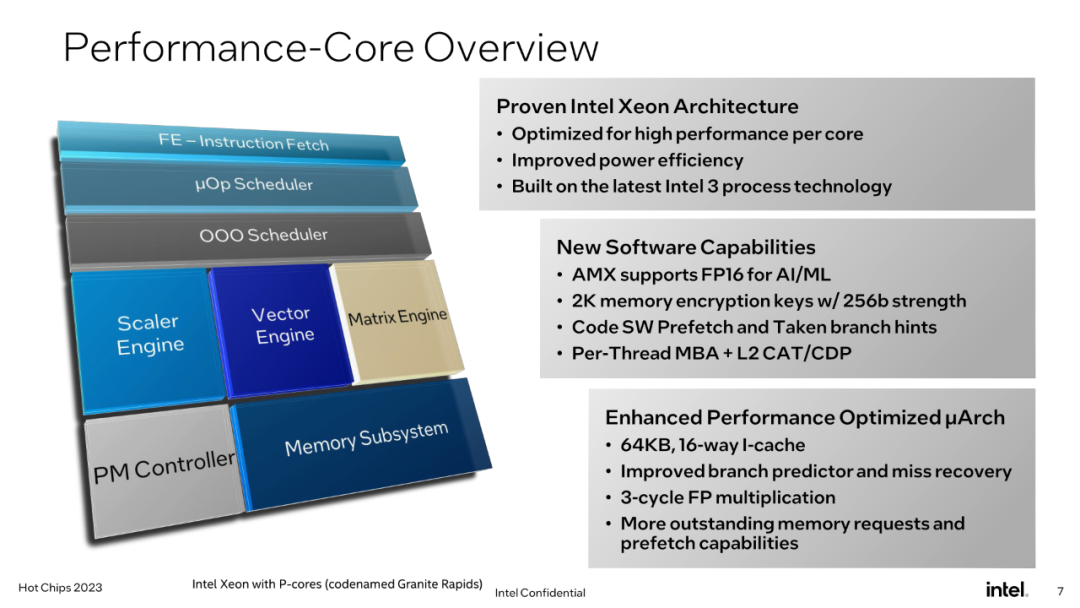

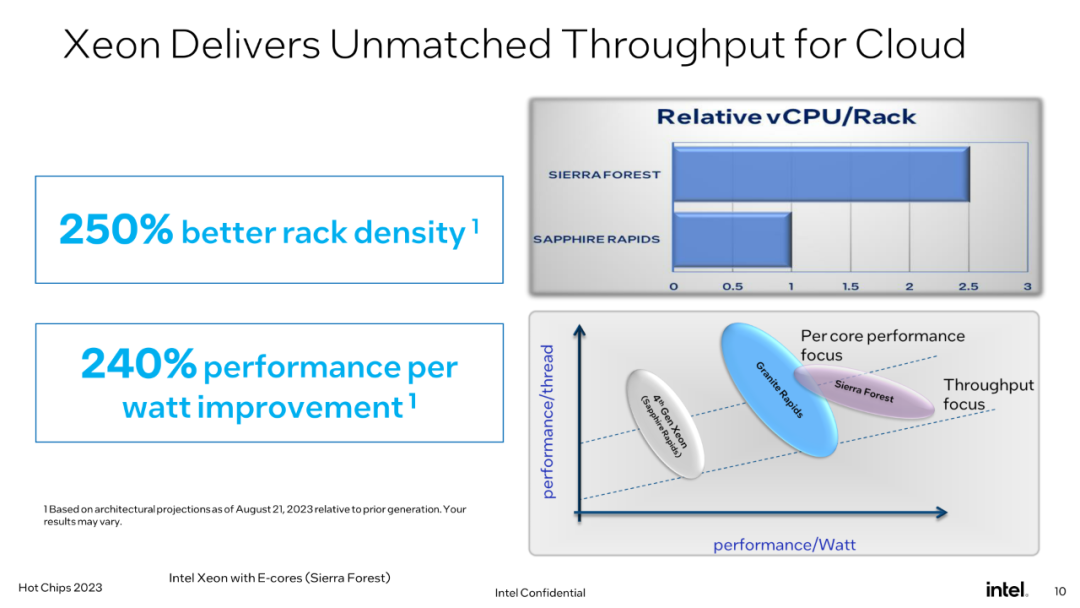

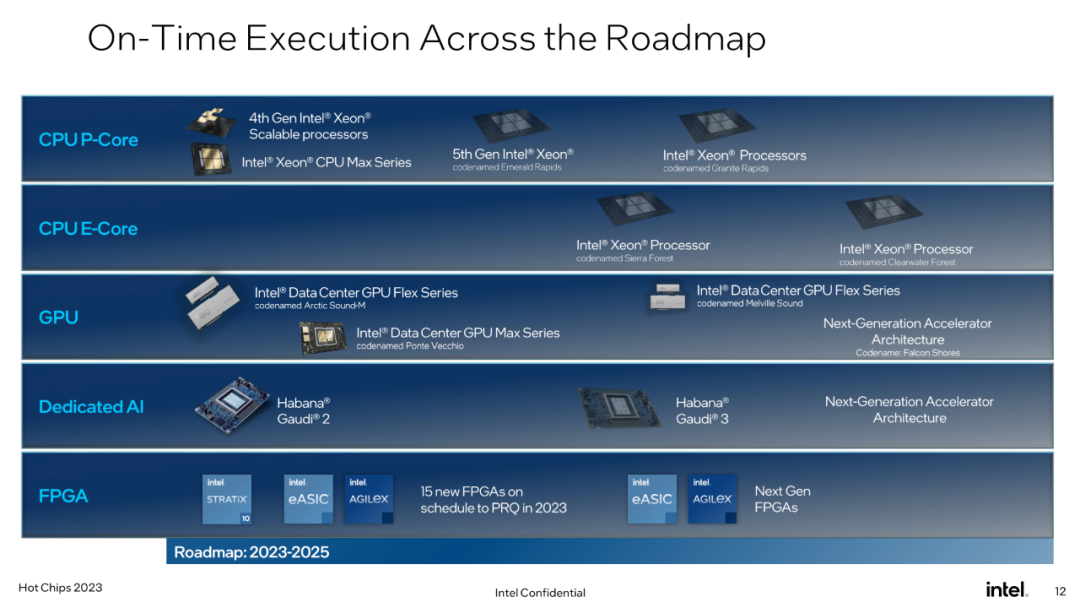

次世代の Intel チップでは、パフォーマンスが大幅に向上する必要があります。 毎年開催される Hot Chips は、半導体業界で最も重要な技術カンファレンスです。その中にはチップ分野の専門家が集まり、世界的なチップメーカーがここで新製品を発表したり、今後の開発の方向性を説明したりすることが多い。 現地時間月曜日、スタンフォード大学で開催されたHot Chips 2023において、インテルは、より高いパフォーマンスを誇る新世代のデータセンターチップ「Sierra Forest」を初公開しました。以前のチップよりもワットあたりのパフォーマンスが向上し、発電量は 240% 増加し、来年発売される予定です。 同時に、インテルはデータセンター チップを初めて 2 つのカテゴリに分類しました。1 つは高エネルギー消費と高性能に焦点を当てた Granite Rapids で、もう 1 つは Granite Rapids です。高いエネルギー効率を重視したシエラフォレストです。 2 つのデータセンター チップ、Granite Rapids と Sierra Forest の具体的な詳細を見てみましょう。 全体として、面積効率の高い E コア (エネルギー効率コア) の導入のおかげで、Granite Rapids と Sierra Forest は今のところ Intel Xeon (Xeon) になると予想されています。スケーラブルなハードウェア エコシステムにおける最も重要なアップデートをまとめました。 まずは、インテル初のデータセンター向け E コア Xeon スケーラブル チップであり、EUV ベースのインテル 3 プロセスの主要製品である Sierra Forest について見てみましょう。 Intelによると、Sierra Forestは来年前半に利用可能になる予定だという。一方、Granite Rapids も同じ Intel 3 プロセスを使用しています。 設計の面では、Granite と Sierra は両方ともチップレット設計に基づいており、Intel EMIB (Embedded Multi-Die Interconnect Bridge、組み込みマルチコア相互接続ブリッジング) テクノロジーに依存しています。は、コンピューティング チップレットと I/O チップレットがパッケージ化されたハイブリッドです。それだけでなく、このチップレットの設計もユニークであり、「完全な」Xeon チップレットをパッケージ化するのではなく、異なるコンピューティング/IO チップレットを使用しています。 これは、Granite と Sierra が、Intel 7 プロセス上に構築された汎用 I/O チップレットを共有できることを意味します。 #インテルは、プラットフォームの詳細を共有することに加えて、E コアと P コア (パフォーマンス) で使用されるアーキテクチャの高レベルの概要も初めて提供しました。芯)。現在の複数世代の Xeon の場合と同様に、Intel はコンシューマー向け部品と同じ基本的な CPU アーキテクチャを活用しています。 したがって、Granite と Sierra は分解された Meteor Lake プロセッサーと考えることができ、Granite は Redwood Cove P コアを搭載し、Sierra は Crestmont E コアを搭載します。 前述したように、これは Intel が Xeon に E コアを提供する最初の試みです。市場。 Intel にとって、これは E-Core 設計をデータセンターのワークロードに合わせて調整することを意味し、前世代の消費者中心の E-Core 設計とは大きく異なります。 Intel は、Crestmont が 6 幅の命令デコード パスと 8 幅のフォールバック バックエンドを提供していることを明らかにしました。 Intel の P コアほど強力ではありませんが、E コアは決して軽量コアではなく、Intel の設計上の決定はこれを反映しています。それでも、その設計は、チップスペースと消費電力の両方の点で、Granite の P コアよりもはるかに効率的です。 Crestmont の L1 命令キャッシュ (I キャッシュ) は 64 KB となり、以前のデザインの I キャッシュのサイズの 2 倍になります。一方、Crestmont E-core ファミリの新しいメンバーは、現在 4 コア クラスターのみを提供している Gracemont とは異なり、これらのコアを 2 コア クラスターまたは 4 コア クラスターにパッケージ化できます。最後に、シエラ/クレストモントの場合、チップは可能な限り花崗岩の急流に近い指示を提供します。これは、BF16 データ型のサポートに加え、AVX-IFMA や AVX-DOT-PROD-INT8 などのさまざまな命令セットのサポートがあることを意味します。 一方、Granite Rapids には Redwood Cove P コアがあります。 Redwood/Granite は Xeon プロセッサのレガシー コアであり、Intel にとっての変更は Sierra Forest ほど大幅ではありませんが、改善されていないという意味ではありません。 マイクロアーキテクチャの観点から見ると、Redwood Cove は Crestmont と同じ 64KB の I キャッシュを備えており、これは以前のバージョンの 2 倍の容量です。しかし最も注目すべき点は、Intel が浮動小数点乗算のレイテンシーをさらに短縮し、4/5 サイクルからわずか 3 サイクルに短縮することに成功したことです。このような基本的な命令のレイテンシの改善は珍しいため、私たちは常にそれを楽しみにしています。 これに加えて、Redwood Cove マイクロアーキテクチャには、Intel の典型的な最適化目標である分岐予測やプリフェッチなどの機能もあります。分岐予測を改善する (そしてまれな間違いによるコストを削減する) ためにできることはすべて、パフォーマンスの面で比較的大きな利益をもたらすことがよくあります。 Redwood Cove の AMX Matrix エンジンは、特に Xeon シリーズで FP16 をサポートしています。FP16 は、すでにサポートされている BF16 や INT8 ほどは使用されていませんが、一般的には改善されていますAMX の柔軟性。 #メモリ暗号化のサポートも改善されています。 Granite Rapids の Redwood Cove は 2048 個の 256 ビット メモリ キーをサポートしますが、Sapphire Rapids は 128 個のキーをサポートします。

Granite Rapids と Sierra Forest の個々の SKU について話すのは時期尚早ですが、 Intel は、コア数が全体的に増加していると明確に述べています。 Granite Rapids チップは、Sapphire Rapids よりも多くの CPU コア (SPR XCC の場合は 60) を提供します。もちろん、Sierra の 144 コアはより多くの CPU コアを提供します。

以前の Xeon の遅延と、E コア Xeon スケーラブル チップの市場投入に長い時間がかかる間、インテルはデータセンター市場でそれほどの存在感を持っていませんでした。かつてのように、支配的な位置にあるため、Granite Rapids と Sierra Forest は重要な転換点となり、インテルのデータセンター製品の将来の開発への道を指し示すことになるでしょう。

#インターネットとオンライン サービスに電力を供給するデータ センターには、膨大なコンピューティング能力が備わっていることを私たちは知っています。要件を満たしており、多くの電力を消費します。近年、AIなどの技術の発展に伴い、テクノロジー企業はコンピューティング能力の向上とエネルギー消費量の削減という課題に直面しており、これによりチップ企業は電力消費効率の向上に注力するようになりました。

現在、データセンターチップ市場におけるインテルのシェアは、AMDやAmpere(インテルの元幹部レニー・ジェームスが設立したスタートアップ)などの競合他社によって段階的に侵食されている。 #今年、Ampere と AMD は独自の高効率クラウド コンピューティング チップを発表し、Arm もこの Hot Chips 2023 で Neoverse V2 プラットフォームを提案しました。競争が激化する中、インテルが危機感を抱くのは避けられない。

https://www.anandtech.com/show/20034/hot-chips-2023-intel-details -granite-rapids-and-sierra-forest-xeonshttps://www.reuters.com/technology/intel-says-new-sierra-forest-chip-more- than-double-power-eficiency-2023-08-28/以上がインテルが次世代データセンター CPU 設計を発表: チップレット設計、性能が 240% 向上の詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。