インテルがノード進化バージョンのパフォーマンス指標を明らかに: 各 PPA の増加は 10% を超えない

IT House News 2 月 22 日、Intel は、IFS Direct Connect イベントで将来のノード進化バージョンのパフォーマンス指標を明らかにしました。各 PPA の改善は 10% を超えない予定です。

IT ホーム 注: PPA は Power/Performance/Area の略で、消費電力、パフォーマンス、面積 (ロジック密度) が総合的に高度なプロセスのパフォーマンス基準として使用されます。

インテルは、将来的に進化バージョンを発売することを確認しており、これらのバージョンを区別するために「パフォーマンスの向上」と「シリコンによる」を表す「P」、「T」、「E」の接尾辞を使用する予定です。それぞれ「3D スタッキング用ビア」。「技術」と「機能拡張」です。この動きにより、ユーザーはさまざまなニーズを満たすためのより多くの選択肢を得ることができます。

Anandtech は、「P」進化バージョンのワットあたりのパフォーマンスが向上していると報告しています。 5 ~ 10%。Intel が新機能を導入した「E」進化バージョンでも、ある程度の改善はありますが、その規模は 5% を超えません。

Anandtech は、ワットあたりのパフォーマンスを 10% 以上向上させるために、Intel は別の主要プロセス ノードを使用して呼び出しを行う予定であるとも述べています。

ドイツのメディアHardwareLuxxの編集者であるAndreas Schilling氏のレポートによると、Intel CEOのPat Gelsinger氏は、将来の「P」および「E」の進化バージョンは電力性能領域(PPA)に基づいていると述べました。 5%以上改善されました。さらに、インテルの主要プロセスノードである7nm、4nm、3nm、20A、18Aでは、各ステップでのPPA改善率は14%から15%に達します。

海外メディア Anandtech とテクノロジー ブログ More Than Moore による以前のレポートの情報に基づくと、TSMC の最近の進化ノードの改善も、おおよそこのレベルに該当します。関連情報は次のようにまとめられています。参考 (? は不明、- は変更されていないことを意味します):

| N5->N5HPC | N4->N4P | N4P->N4X | N3->N3E | ||

| ##10% | #?#- | #?? | パフォーマンス (改善) | 5% | |

| 6% | ≥4% | 5% | エリア (縮小) | - | |

| - | ? | - | これらの従来のプロセス ノードに加えて、インテルは顧客にさらに豊富な選択肢を提供します: Stu Pann、Intel Foundry Leader) とのインタビューでIFS Direct Connect イベントの前夜、海外メディア Tom's Hardware に対し、同氏は EDA パートナーと協力して | NVIDIA 4N (TSMC の 5nm プロセスに基づく) に似たカスタマイズされたノードを顧客向けに開発する意欲を表明しました。

以上がインテルがノード進化バージョンのパフォーマンス指標を明らかに: 各 PPA の増加は 10% を超えないの詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。

ホットAIツール

Undresser.AI Undress

リアルなヌード写真を作成する AI 搭載アプリ

AI Clothes Remover

写真から衣服を削除するオンライン AI ツール。

Undress AI Tool

脱衣画像を無料で

Clothoff.io

AI衣類リムーバー

AI Hentai Generator

AIヘンタイを無料で生成します。

人気の記事

ホットツール

メモ帳++7.3.1

使いやすく無料のコードエディター

SublimeText3 中国語版

中国語版、とても使いやすい

ゼンドスタジオ 13.0.1

強力な PHP 統合開発環境

ドリームウィーバー CS6

ビジュアル Web 開発ツール

SublimeText3 Mac版

神レベルのコード編集ソフト(SublimeText3)

ホットトピック

7454

7454

15

15

1375

1375

52

52

77

77

11

11

14

14

9

9

Intel Core Ultra 9 285K プロセッサーの公開: CineBench R23 マルチコアの実行スコアは i9-14900K より 18% 高い

Jul 25, 2024 pm 12:25 PM

Intel Core Ultra 9 285K プロセッサーの公開: CineBench R23 マルチコアの実行スコアは i9-14900K より 18% 高い

Jul 25, 2024 pm 12:25 PM

7月25日のこのサイトのニュースによると、情報源のJaykihn氏は昨日(7月24日)、Xプラットフォームにツイートを投稿し、Intel Core Ultra9285K「ArrowLake-S」デスクトッププロセッサの実行スコアデータを共有した結果を示した。 Core 14900K よりも 18% 高速です。このウェブサイトはツイートの内容を引用し、情報源はインテル Core Ultra9285K プロセッサーの ES2 および QS バージョンの実行スコアを共有し、Core i9-14900K プロセッサーと比較しました。レポートによると、CinebenchR23、Geekbench5、SpeedoMeter、WebXPRT4、CrossMark などのワークロードを実行する場合の ArrowLake-SQS の TD

Intel N250 低電力プロセッサを公開: 4 コア、4 スレッド、周波数 1.2 GHz

Jun 03, 2024 am 10:26 AM

Intel N250 低電力プロセッサを公開: 4 コア、4 スレッド、周波数 1.2 GHz

Jun 03, 2024 am 10:26 AM

5月16日のこのサイトのニュースによると、情報源@InstLatX64は最近、IntelがN200シリーズ「AlderLake-N」シリーズに代わる低電力プロセッサの新しいN250「TwinLake」シリーズの発売を準備しているとツイートした。出典: videocardz N200 シリーズ プロセッサは、低コストのラップトップ、シン クライアント、組み込みシステム、セルフサービスおよび POS 端末、NAS、家電製品で人気があります。 「TwinLake」は新しいプロセッサ シリーズのコード名で、リング バス (RingBus) レイアウトを使用するシングルチップ プロセッサ Die に似ていますが、コンピューティング能力を完成させるために E コア クラスタを備えています。このサイトに添付されているスクリーンショットは次のとおりです: AlderLake-N

Intel、CNVio3インターフェースをサポートするWi-Fi 7 BE201ネットワークカードを発表

Jun 07, 2024 pm 03:34 PM

Intel、CNVio3インターフェースをサポートするWi-Fi 7 BE201ネットワークカードを発表

Jun 07, 2024 pm 03:34 PM

6月1日の当サイトのニュースによると、インテルは5月27日にサポート文書を更新し、コードネーム「Fillmore Peak2」というWi-Fi7(802.11be)BE201ネットワークカードの製品詳細を発表した。上の画像の出典: Benchlife Web サイト 注: PCIe/USB インターフェイスを使用する既存の BE200 および BE202 とは異なり、BE201 は最新の CNVio3 インターフェイスをサポートします。 BE201 ネットワーク カードの主な仕様は BE200 と同様で、2x2TX/RX ストリーミングをサポートし、2.4 GHz、5 GHz、および 6 GHz をサポートします。最大ネットワーク速度は、標準の最大速度 40 Gbit よりもはるかに低い 5 Gbps に達します。 /秒。 BE201 は Bluetooth 5.4 および Bluetooth LE もサポートします。

MSI、Intel Alder Lake-N N100プロセッサを搭載した新しいMS-C918ミニコンソールを発売

Jul 03, 2024 am 11:33 AM

MSI、Intel Alder Lake-N N100プロセッサを搭載した新しいMS-C918ミニコンソールを発売

Jul 03, 2024 am 11:33 AM

本ウェブサイトは7月3日、現代企業の多様化するニーズに応えるため、MSIの子会社であるMSIIPCが産業用ミニホスト「MS-C918」を発売したと報じた。公開価格はまだ見つかっていない。 MS-C918 は、コスト効率、使いやすさ、携帯性を重視する企業向けに位置付けられており、重要でない環境向けに特別に設計されており、3 年間の耐用年数保証を提供します。 MS-C918 は、超低電力ソリューション向けに特別に調整された Intel AlderLake-NN100 プロセッサを使用したハンドヘルド産業用コンピュータです。当サイトに添付されているMS-C918の主な機能と特長は以下のとおりです。 コンパクトサイズ:80mm×80mm×36mmの手のひらサイズで、操作が簡単でモニターの後ろに隠れます。表示機能: 2 HDMI2 経由。

ASUS、Intelの第13/14世代Coreプロセッサーの不安定性の問題を軽減するため、Z790マザーボード用のBIOSアップデートをリリース

Aug 09, 2024 am 12:47 AM

ASUS、Intelの第13/14世代Coreプロセッサーの不安定性の問題を軽減するため、Z790マザーボード用のBIOSアップデートをリリース

Aug 09, 2024 am 12:47 AM

8 月 8 日のこの Web サイトのニュースによると、MSI と ASUS は本日、Intel Core 第 13 世代および第 14 世代デスクトップ プロセッサの不安定性の問題に対応して、一部の Z790 マザーボード用の 0x129 マイクロコード アップデートを含む BIOS のベータ版をリリースしました。 BIOS アップデートを提供する ASUS の最初のマザーボードには、ROGMAXIMUSZ790HEROBetaBios2503ROGMAXIMUSZ790DARKHEROBetaBios1503ROGMAXIMUSZ790HEROBTFBetaBios1503ROGMAXIMUSZ790HEROEVA-02 統合バージョン BetaBios2503ROGMAXIMUSZ790A が含まれます。

インテルはインテル 3 プロセスを詳細に説明しています。より多くの EUV リソグラフィーを適用し、同じ電力消費の周波数を最大 18% 増加させます。

Jun 19, 2024 pm 10:53 PM

インテルはインテル 3 プロセスを詳細に説明しています。より多くの EUV リソグラフィーを適用し、同じ電力消費の周波数を最大 18% 増加させます。

Jun 19, 2024 pm 10:53 PM

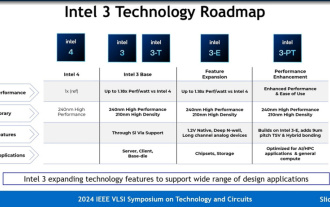

6 月 19 日のこのサイトのニュースによると、2024 IEEEVLSI セミナー活動の一環として、Intel は最近、公式 Web サイトで Intel3 プロセス ノードの技術詳細を紹介しました。 Intel の最新世代の FinFET トランジスタ テクノロジは、Intel4 と比較して、EUV を使用するための手順が追加されており、基本的な Intel3 と 3 つのバリアントを含む、ファウンドリ サービスを長期間提供するノード ファミリになります。ノード。その中で、Intel3-E はアナログ モジュールの製造に適した 1.2V の高電圧をネイティブでサポートしていますが、将来の Intel3-PT では全体のパフォーマンスがさらに向上し、より微細な 9μm ピッチの TSV とハイブリッド ボンディングがサポートされる予定です。インテルは次のように主張しています

Intel Panther Lake モバイル プロセッサの仕様を公開: 最大「4+8+4」16 コア CPU、12 Xe3 コア ディスプレイ

Jul 18, 2024 pm 04:43 PM

Intel Panther Lake モバイル プロセッサの仕様を公開: 最大「4+8+4」16 コア CPU、12 Xe3 コア ディスプレイ

Jul 18, 2024 pm 04:43 PM

7 月 16 日のこのサイトのニュースによると、ArrowLake デスクトップ プロセッサと BartlettLake デスクトップ プロセッサの仕様が明らかになった後、ブロガー @jaykihn0 が早朝に Intel PantherLake プロセッサのモバイル U および H バージョンの仕様を公開しました。 Panther Lake モバイル プロセッサは Core Ultra300 シリーズと名付けられる予定で、次のバージョンで入手可能になります: PTL-U: 4P+0E+4LPE+4Xe、15WPL1PTL-H: 4P+8E+4LPE+12Xe、25WPL1PTL-H : 4P+8E+4LPE+ 4Xe、25WPL1 ブロガーは、PantherLake プロセッサの 12Xe コア ディスプレイ バージョンもリリースしました。

イノラックスはファンアウトパネルレベルの半導体パッケージング技術を年末までに量産する計画

Aug 07, 2024 pm 06:18 PM

イノラックスはファンアウトパネルレベルの半導体パッケージング技術を年末までに量産する計画

Aug 07, 2024 pm 06:18 PM

このウェブサイトの 8 月 6 日のニュースによると、Innolux Corporation のゼネラルマネージャーである Yang Zhuxiang 氏は昨日 (8 月 5 日)、同社は半導体ファンアウトパネルレベルパッケージング (FOPLP) を積極的に導入および促進しており、今後大量の実装が期待されていると述べました。今年末までにチップファーストを生産する予定であるため、プロセス技術の収益への貢献は来年の第 1 四半期に明らかになるでしょう。 Fenye Innolux 氏は、今後 1 ~ 2 年以内に中級から高級製品向けの再配線層 (RDLFirst) プロセス技術を量産する予定であり、パートナーと協力して技術的に最も難しいガラス穴あけ加工の開発に取り組むと述べました ( TGV)プロセスにはさらに2〜3年かかりますが、1年以内に量産化できます。 Yang Zhuxiang 氏は、Innolux の FOPLP 技術は「量産の準備ができており」、ローエンドおよびミッドレンジの製品で市場に参入すると述べました。