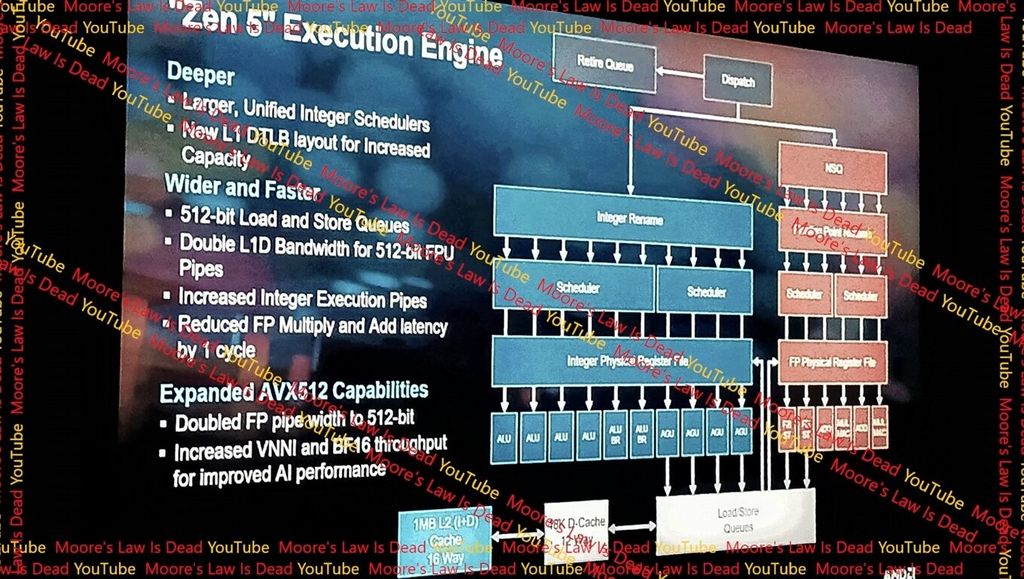

AMD Zen 5 実行エンジンを公開: 真の 512 ビット FPU を使用

このサイトの 4 月 5 日のニュースによると、ソースの Moore's Law is Dead は、最新のビデオで AMD Zen 5 プロセッサ実行エンジン (Execution Engine) に関する情報を共有し、真の 512 ビット浮動小数点を使用すると述べました。ユニット(FPU)。

ソースによって共有されたスライドによると、真の 512 ビット FPU を使用した Zen 5 の実行エンジンが詳細に説明されています。

AMD Zen 4 プロセッサーは、AVX-512 命令ワークロードの実行時にデュアルチャネル 256 ビット FPU を使用しますが、Zen 5 は実際の 512 ビット FPU を使用して 512 ビットを処理します。 AVX または VNNI 命令。

このサイトは、AMD が 512 ビット FPU に関連するコンポーネントをアップグレードし、L1 DTLB の容量を増加し、ロードストア キューを拡張し、L1 データ キャッシュの帯域幅を 2 倍にしたこともレポートから知りました。サイズが50%増加しました。 L1Dのサイズは、「Zen 4」の32KBから現在は48KBに増加しています。

FPU MADD レイテンシが 1 サイクル短縮されました。 FPU に加えて、AMD は整数実行パイプの数を 8 (Zen 4) から 10 に増やしましたが、コアあたりの専用 L2 キャッシュ サイズは依然として 1 MB です。

以上がAMD Zen 5 実行エンジンを公開: 真の 512 ビット FPU を使用の詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。

ホットAIツール

Undresser.AI Undress

リアルなヌード写真を作成する AI 搭載アプリ

AI Clothes Remover

写真から衣服を削除するオンライン AI ツール。

Undress AI Tool

脱衣画像を無料で

Clothoff.io

AI衣類リムーバー

Video Face Swap

完全無料の AI 顔交換ツールを使用して、あらゆるビデオの顔を簡単に交換できます。

人気の記事

ホットツール

メモ帳++7.3.1

使いやすく無料のコードエディター

SublimeText3 中国語版

中国語版、とても使いやすい

ゼンドスタジオ 13.0.1

強力な PHP 統合開発環境

ドリームウィーバー CS6

ビジュアル Web 開発ツール

SublimeText3 Mac版

神レベルのコード編集ソフト(SublimeText3)

ホットトピック

7715

7715

15

15

1641

1641

14

14

1395

1395

52

52

1289

1289

25

25

1232

1232

29

29

ASUS、AMD Ryzen 9 8945H と興味深いお香ディスペンサーを搭載した Adol Book 14 Air を発表

Aug 01, 2024 am 11:12 AM

ASUS、AMD Ryzen 9 8945H と興味深いお香ディスペンサーを搭載した Adol Book 14 Air を発表

Aug 01, 2024 am 11:12 AM

ASUSはすでに、Zenbook 14 OLED(Amazonで現在1,079.99ドル)を含むさまざまな14インチラップトップを提供しています。このたび、表面的には典型的な 14 インチのラップトップのように見える Adol Book 14 Air を導入することが決定しました。ただし、目立たないメタ

OneXGPU 2 の AMD Radeon RX 7800M は Nvidia RTX 4070 ラップトップ GPU を上回ります

Sep 09, 2024 am 06:35 AM

OneXGPU 2 の AMD Radeon RX 7800M は Nvidia RTX 4070 ラップトップ GPU を上回ります

Sep 09, 2024 am 06:35 AM

OneXGPU 2 は、AMD ですらまだ発表していない GPU である Radeon RX 7800M を搭載した最初の eGPU です。外部グラフィックス カード ソリューションのメーカーである One-Netbook によって明らかにされたように、新しい AMD GPU は RDNA 3 アーキテクチャに基づいており、Navi

Ryzen AI ソフトウェアが新しい Strix Halo および Kraken Point AMD Ryzen プロセッサをサポート

Aug 01, 2024 am 06:39 AM

Ryzen AI ソフトウェアが新しい Strix Halo および Kraken Point AMD Ryzen プロセッサをサポート

Aug 01, 2024 am 06:39 AM

AMD Strix Point ラップトップは市場に登場したばかりで、次世代の Strix Halo プロセッサは来年中にリリースされる予定です。ただし、同社はすでに Strix Halo および Krackan Point APU のサポートを Ryzen AI ソフトウェアに追加しています。

ハンドヘルドコンソール用AMD Z2 Extremeチップが2025年初頭の発売に向けて発表

Sep 07, 2024 am 06:38 AM

ハンドヘルドコンソール用AMD Z2 Extremeチップが2025年初頭の発売に向けて発表

Sep 07, 2024 am 06:38 AM

AMDはRyzen Z1 Extreme(およびその非Extremeバージョン)をハンドヘルドゲーム機向けにカスタマイズしたにもかかわらず、このチップが主流のハンドヘルド機に搭載されたのはAsus ROG Ally(Amazonで現在569ドル)とLenovo Legion Go(3つ)の2つだけでした。 Rを数えると

Ryzen AI 9 HX 370 を搭載した初の Minisforum ミニ PC、高額で発売されると噂

Sep 29, 2024 am 06:05 AM

Ryzen AI 9 HX 370 を搭載した初の Minisforum ミニ PC、高額で発売されると噂

Sep 29, 2024 am 06:05 AM

Aoostar は Strix Point mini PC を最初に発表した企業の 1 つであり、その後、Beelink が 999 ドルという高騰する開始価格で SER9 を発売しました。 Minisforum は、EliteMini AI370 をからかうことでパーティーに参加しました。その名前が示すように、これは会社の

AMD、数百万台のRyzenおよびEPYCプロセッサに影響する「Sinkclose」の重大度の高い脆弱性を発表

Aug 10, 2024 pm 10:31 PM

AMD、数百万台のRyzenおよびEPYCプロセッサに影響する「Sinkclose」の重大度の高い脆弱性を発表

Aug 10, 2024 pm 10:31 PM

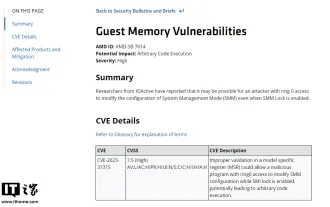

8月10日の当サイトのニュースによると、AMDは一部のEPYCおよびRyzenプロセッサにコード「CVE-2023-31315」の「Sinkclose」と呼ばれる新たな脆弱性が存在し、世界中の数百万のAMDユーザーが関与する可能性があることを正式に確認したとのこと。では、シンククローズとは何でしょうか? 『WIRED』の報道によると、この脆弱性により侵入者は「システム管理モード(SMM)」で悪意のあるコードを実行することが可能になるという。伝えられるところによると、侵入者はブートキットと呼ばれるマルウェアの一種を使用して相手のシステムを制御する可能性があり、このマルウェアはウイルス対策ソフトウェアでは検出できません。このサイトからの注: システム管理モード (SMM) は、高度な電源管理とオペレーティング システムに依存しない機能を実現するために設計された特別な CPU 動作モードです。

取引 | 120Hz OLED、64GB RAM、AMD Ryzen 7 Pro を搭載した Lenovo ThinkPad P14s Gen 5 が現在 60% オフです

Sep 07, 2024 am 06:31 AM

取引 | 120Hz OLED、64GB RAM、AMD Ryzen 7 Pro を搭載した Lenovo ThinkPad P14s Gen 5 が現在 60% オフです

Sep 07, 2024 am 06:31 AM

最近、多くの学生が学校に戻り、古いラップトップがもう役に立たないことに気づいている人もいるかもしれません。大学生の中には、ゴージャスな OLED スクリーンを備えたハイエンドのビジネス ノートブックを市場に出す人もいるかもしれません。

Beelink SER9: Radeon 890M iGPU を搭載したコンパクト AMD Zen 5 ミニ PC が発表されましたが、eGPU オプションは限られていました

Sep 12, 2024 pm 12:16 PM

Beelink SER9: Radeon 890M iGPU を搭載したコンパクト AMD Zen 5 ミニ PC が発表されましたが、eGPU オプションは限られていました

Sep 12, 2024 pm 12:16 PM

Beelink は、新しいミニ PC と付属のアクセサリを猛烈な勢いで発表し続けています。要約すると、EQi12、EQR6、EX eGPU ドックをリリースしてから 1 か月強が経過しました。現在、同社は AMD の新しい Strix に注目しています。