众核上的数据仓库并行优化

近几年众核硬件逐渐被应用到数据仓库产品当中。目前主要的众核硬件包括以Intel SCC为代表的众核CPU、以Intel志强融核系列为代表的众核协处理器、以NVIDIA和AMD为代表的众核GPU。本文第一章介绍目前的主要的众核硬件及其特性,并从性价比和通用性方面对众核硬

近几年众核硬件逐渐被应用到数据仓库产品当中。目前主要的众核硬件包括以Intel SCC为代表的众核CPU、以Intel志强融核系列为代表的众核协处理器、以NVIDIA和AMD为代表的众核GPU。本文第一章介绍目前的主要的众核硬件及其特性,并从性价比和通用性方面对众核硬件进行比较;第二章介绍目前数据仓库中典型操作符在众核硬件上的优化技术。

1. 主要众核硬件

1.1. 多核CPU

多核的CPU虽然不是严格意义上的众核,但是在目前的很多研究中都将多核CPU视为和众核具相似的硬件而进行比较研究。多核CPU目前通常认为是8核及以下的通用CPU,每个核都有独立的L2和L1 Cache,多个核之间需要通过共享的内存或者L3 Cache才能交换数据。但核心数量并不是多核与众核的严格分界线,Intel目前核数最多CPU可以达到10个核。多核与众核的主要区别在于通用性和体系结构方面。1.2. 众核CPU

众核的CPU目前并不常见,在市场上没有销售。以Intel SCC为代表的众核CPU只提供给合作的高校和科研院所作为研究用途。在近几年的论文中常可以看见SCC的身影。Intel SCC中集成了48个对等的核,即每个核的功能和性能都是一样的,且每个核都有专属的L2 Cache。每两个核集成在一个tile中,共24个tile组成一个4*6的矩阵,之间通过CPU内部的告诉总线连接。每个tile中的两个核共享一部分(16KB)L1 Cache,这部分共享的L1 Cache成为MPB(Massage Passing Buffer)。所有tile中的MPB又可以被任意一个核访问,从而构成了一个384KB L1 Cache。

SCC中的每个核具有1GHz的主频和较强的逻辑计算能力,支持的指令集和普通的CPU类似。从而在增加核数的同时保证了通用性。此外,特殊的Cache设计使得可以针对具体的计算任务做出优化。

1.3. 众核协处理器

协处理器通过高速总线和CPU连接或者PCI-E借口连接到北桥上,是辅助CPU完成特定计算任务的计算器件。ARM架构的微处理器可以支持多大数十个协处理器,在嵌入式终端和智能设备中应用非常广泛。在通用计算平台上,Intel也推出了志强融核系列的协处理产品。至强融核协处理器其实是一款搭载众核处理器、显存(GDDR5)、PCI-E16X接口的外设,通过PCI-E插槽接入主板,通过北桥和CPU、主存连接。

目前的志强融合协处理器最多继承61个核,其中一个核是处理PCI-E数据传输的,其他60个核是对等的计算单元。支持的板载内存的类型为DDR5,具有300+GB/s的访存带宽,最大可以支持16GB的板载内存。较GPU而言,协处理器支持的板载访存带宽相近,但支持的最大内存大出1-2倍,同时协处理器的核数相对较少、但逻辑计算能力更强、通用性更好。

1.4. 众核GPU

众核GPU是目前最为常见的众核硬件。主要的GPU厂商NVIDA和AMD都提供了众核的GPU产品。其中NVIDA实现的CUDA技术应用已经非常广泛。在架构上GPU和协处理器有相似之处。但众核GPU中的核心计算能力较强、逻辑能力很差,因此GPU的专用性更强,通用性更差。此外,GPU中的核心通常被分为若干个组,每个组中有几十个核心,这些核心可以同时执行同一条指令、处理不同的数据,即SIMP。1.5. 众核硬件比较

在通用性方面1、多核CPU:通用,直接通过数据总线访问系统内存,带宽20-30GB/s;

2、众核 CPU:通用性稍差,架构类似GPU和协处理器,但可以直接访问系统主存,目前还没推广

3、众核协处理器:和GPU类似,单核的计算能力和逻辑运算能力更强,通用性更好一些。

4、众核GPU: 浮点计算能力强,逻辑运算能力差,显存几GB,带宽200GB/s,但需要通过PCI-E总线从主存取数据(PCI-E 16x :4GB/s),通用性差

能耗、性价比的比较

GPGPU的性价比最高、能耗最低,但软件开发成本高,在部分算法中性能并不突出 Many-core CPU总体好于multi-core CPU Multi-core CPU在某些复杂计算中表现突出。

总结下来,除了通用的多核CPU以外,many-core并不是共享所有的主存和cache的,无论CPU还是GPU都是NUMA(Non Uniform Memory Access Architecture,非统一内存访问架构)的架构。 算法要访问数据。要提高并行度,就要提高数据访问的局部性 GPU和协处理器访问系统内存的带宽会比访问本地内存地带宽低50倍以上。

2. 众核上数据仓库优化技术

2.1. 缓存的优化

众核处理器通常在缓存方面都有着和通用的多核CPU不同的设计,比如SCC就支持L1 Cache的跨核访问。在数据仓库算法中,表扫面算法由于数据局部性不好,数据如果经过多级缓存进入核中处理势必会影响效率,因此优化时可以针对表扫描算法,将数据直接加载到MPB中,进而进入核中做谓词过滤。2.2. 连接算法的优化

数据仓库中常用的连接算法包括sort-merge连接和hash连接。Sort-merge连接由于排序和归并的过程中,多个线程(核)并不需要共享数据,因此很适合在众核硬件上实现。但是sort-merge本身有很多的局限性,比如数据仓库中的连接通常在维表和事实表之间进行,而事实表是非常大的,sort-merge要求事实表实现在连接属性上排序,排序的代价是非常大的。

更为通用的hash连接由于在hash划分数据和连接时,多个线程(核)需要访问共享的哈希表和哈希桶,如果不做优化,在众核上是不可能有明显的性能提升的。因此出现了一些优化的技术。

常见的优化技术是基于Bucket的,即先将数据划分为不相关的Bucket再做链接。那么算法就分为分桶和连接两个部分。

在分桶阶段,为了利用多核达到性能的提升,也要保证多个核心不能有共享的数据,常用的算法有两种:

1、类似quickSort的分桶算法

Step1: 将array中hash值末位为0和为1的元素分开

Step2: 对分开的两个子array分别按照hash值末两位的值分开,依次递归,直到子array中元素个数小于某个阈值

2、两阶段分桶算法

Hash桶的个数是固定的,第一阶段,各个core将数据表的一段hash到自己的桶里。 第二阶段,各个core将某一列上的桶合并。如图2.1所示。

第一种算法的复杂度较高一些(n*log n),后一种算法虽然是线性的时间复杂度,但是要求分桶的个数预先固定,在数据倾斜的情况下就会导致分桶的不均衡。

分桶之后的连接算法可以采用基于位图的连接算法。如图2.2所示,第一阶段是分桶,第二阶段是在左表的一个分桶上计算出一个位图,其实就是一个布隆过滤器,第三阶段基于左表的位图来过滤右表的分桶,避免了不必要的连接操作,也就避免的大量的内存访问。

此外,连接算法的优化方面,由于数据仓库中维表很小,可以在维表上做完谓词过滤、得到一个布尔向量,将布尔向量读入到各个核的缓冲区中,和事实表做连接。

还有一种称为Invisible Join 的连接优化技术,是一种查询重写技术。由于维表比较小,当维表和事实表连接时,将连接条件转换成事实表上的谓词。 如:事实表的一个外键连接到维表的一个主键上。如果维表的主键上的值在一个连续范围内,可以将其重写成事实表外键上的一个between谓词,从而避免了反复对维表的随机访问。

핫 AI 도구

Undresser.AI Undress

사실적인 누드 사진을 만들기 위한 AI 기반 앱

AI Clothes Remover

사진에서 옷을 제거하는 온라인 AI 도구입니다.

Undress AI Tool

무료로 이미지를 벗다

Clothoff.io

AI 옷 제거제

AI Hentai Generator

AI Hentai를 무료로 생성하십시오.

인기 기사

뜨거운 도구

메모장++7.3.1

사용하기 쉬운 무료 코드 편집기

SublimeText3 중국어 버전

중국어 버전, 사용하기 매우 쉽습니다.

스튜디오 13.0.1 보내기

강력한 PHP 통합 개발 환경

드림위버 CS6

시각적 웹 개발 도구

SublimeText3 Mac 버전

신 수준의 코드 편집 소프트웨어(SublimeText3)

뜨거운 주제

7467

7467

15

15

1376

1376

52

52

77

77

11

11

46

46

19

19

18

18

20

20

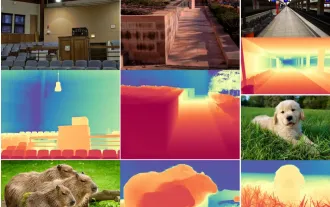

오픈 소스! ZoeDepth를 넘어! DepthFM: 빠르고 정확한 단안 깊이 추정!

Apr 03, 2024 pm 12:04 PM

오픈 소스! ZoeDepth를 넘어! DepthFM: 빠르고 정확한 단안 깊이 추정!

Apr 03, 2024 pm 12:04 PM

0. 이 글은 어떤 내용을 담고 있나요? 우리는 다재다능하고 빠른 최첨단 생성 단안 깊이 추정 모델인 DepthFM을 제안합니다. DepthFM은 전통적인 깊이 추정 작업 외에도 깊이 인페인팅과 같은 다운스트림 작업에서 최첨단 기능을 보여줍니다. DepthFM은 효율적이며 몇 가지 추론 단계 내에서 깊이 맵을 합성할 수 있습니다. 이 작품을 함께 읽어보아요~ 1. 논문 정보 제목: DepthFM: FastMoncularDepthEstimationwithFlowMatching 저자: MingGui, JohannesS.Fischer, UlrichPrestel, PingchuanMa, Dmytr

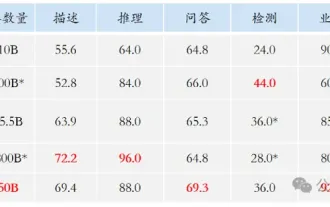

Google은 열광하고 있습니다. JAX 성능이 Pytorch와 TensorFlow를 능가합니다! GPU 추론 훈련을 위한 가장 빠른 선택이 될 수 있습니다.

Apr 01, 2024 pm 07:46 PM

Google은 열광하고 있습니다. JAX 성능이 Pytorch와 TensorFlow를 능가합니다! GPU 추론 훈련을 위한 가장 빠른 선택이 될 수 있습니다.

Apr 01, 2024 pm 07:46 PM

Google이 추진하는 JAX의 성능은 최근 벤치마크 테스트에서 Pytorch와 TensorFlow를 능가하여 7개 지표에서 1위를 차지했습니다. 그리고 JAX 성능이 가장 좋은 TPU에서는 테스트가 이루어지지 않았습니다. 개발자들 사이에서는 여전히 Tensorflow보다 Pytorch가 더 인기가 있습니다. 그러나 앞으로는 더 큰 모델이 JAX 플랫폼을 기반으로 훈련되고 실행될 것입니다. 모델 최근 Keras 팀은 기본 PyTorch 구현을 사용하여 세 가지 백엔드(TensorFlow, JAX, PyTorch)와 TensorFlow를 사용하는 Keras2를 벤치마킹했습니다. 첫째, 그들은 주류 세트를 선택합니다.

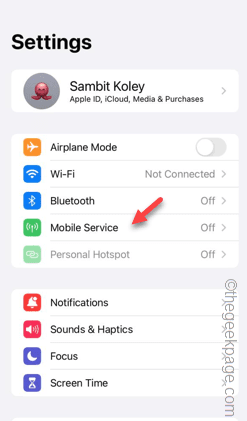

iPhone의 느린 셀룰러 데이터 인터넷 속도: 수정 사항

May 03, 2024 pm 09:01 PM

iPhone의 느린 셀룰러 데이터 인터넷 속도: 수정 사항

May 03, 2024 pm 09:01 PM

지연이 발생하고 iPhone의 모바일 데이터 연결 속도가 느립니까? 일반적으로 휴대폰의 셀룰러 인터넷 강도는 지역, 셀룰러 네트워크 유형, 로밍 유형 등과 같은 여러 요소에 따라 달라집니다. 더 빠르고 안정적인 셀룰러 인터넷 연결을 얻기 위해 할 수 있는 일이 몇 가지 있습니다. 수정 1 – iPhone 강제 다시 시작 때로는 장치를 강제로 다시 시작하면 셀룰러 연결을 포함한 많은 항목이 재설정됩니다. 1단계 – 볼륨 높이기 키를 한 번 눌렀다가 놓습니다. 그런 다음 볼륨 작게 키를 눌렀다가 다시 놓습니다. 2단계 - 프로세스의 다음 부분은 오른쪽에 있는 버튼을 누르는 것입니다. iPhone이 다시 시작되도록 하세요. 셀룰러 데이터를 활성화하고 네트워크 속도를 확인하세요. 다시 확인하세요 수정 2 – 데이터 모드 변경 5G는 더 나은 네트워크 속도를 제공하지만 신호가 약할 때 더 잘 작동합니다

초지능의 생명력이 깨어난다! 하지만 자동 업데이트 AI가 등장하면서 엄마들은 더 이상 데이터 병목 현상을 걱정할 필요가 없습니다.

Apr 29, 2024 pm 06:55 PM

초지능의 생명력이 깨어난다! 하지만 자동 업데이트 AI가 등장하면서 엄마들은 더 이상 데이터 병목 현상을 걱정할 필요가 없습니다.

Apr 29, 2024 pm 06:55 PM

세상은 미친 듯이 큰 모델을 만들고 있습니다. 인터넷의 데이터만으로는 충분하지 않습니다. 훈련 모델은 '헝거게임'처럼 생겼고, 전 세계 AI 연구자들은 이러한 데이터를 탐식하는 사람들에게 어떻게 먹이를 줄지 고민하고 있습니다. 이 문제는 다중 모드 작업에서 특히 두드러집니다. 아무것도 할 수 없던 시기에, 중국 인민대학교 학과의 스타트업 팀은 자체 새로운 모델을 사용하여 중국 최초로 '모델 생성 데이터 피드 자체'를 현실화했습니다. 또한 이해 측면과 생성 측면의 두 가지 접근 방식으로 양측 모두 고품질의 다중 모드 새로운 데이터를 생성하고 모델 자체에 데이터 피드백을 제공할 수 있습니다. 모델이란 무엇입니까? Awaker 1.0은 중관촌 포럼에 최근 등장한 대형 멀티모달 모델입니다. 팀은 누구입니까? 소폰 엔진. 런민대학교 힐하우스 인공지능대학원 박사과정 학생인 Gao Yizhao가 설립했습니다.

미 공군이 주목할만한 최초의 AI 전투기를 선보였습니다! 전 과정에 걸쳐 장관이 직접 간섭 없이 테스트를 진행했고, 10만 줄의 코드를 21차례 테스트했다.

May 07, 2024 pm 05:00 PM

미 공군이 주목할만한 최초의 AI 전투기를 선보였습니다! 전 과정에 걸쳐 장관이 직접 간섭 없이 테스트를 진행했고, 10만 줄의 코드를 21차례 테스트했다.

May 07, 2024 pm 05:00 PM

최근 군계는 미군 전투기가 이제 AI를 활용해 완전 자동 공중전을 완수할 수 있다는 소식에 충격을 받았다. 네, 얼마 전 미군의 AI 전투기가 최초로 공개되면서 그 미스터리가 드러났습니다. 이 전투기의 정식 명칭은 VISTA(Variable Stability Flight Simulator Test Aircraft)로 미 공군 장관이 직접 조종해 일대일 공중전을 모의 실험한 것이다. 5월 2일, 미 공군 장관 프랭크 켄달(Frank Kendall)이 X-62AVISTA를 타고 에드워드 공군 기지에서 이륙했습니다. 1시간의 비행 동안 모든 비행 작업은 AI에 의해 자동으로 완료되었습니다. Kendall은 "지난 수십 년 동안 우리는 자율 공대공 전투의 무한한 잠재력에 대해 생각해 왔지만 항상 도달할 수 없는 것처럼 보였습니다."라고 말했습니다. 그러나 지금은,

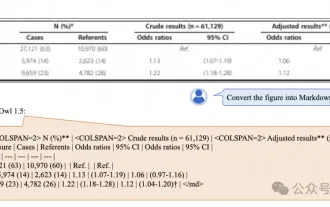

대형 모델을 이해하는 Alibaba 7B 다중 모드 문서, 새로운 SOTA 획득

Apr 02, 2024 am 11:31 AM

대형 모델을 이해하는 Alibaba 7B 다중 모드 문서, 새로운 SOTA 획득

Apr 02, 2024 am 11:31 AM

다중 모드 문서 이해 기능을 위한 새로운 SOTA! Alibaba mPLUG 팀은 최신 오픈 소스 작업인 mPLUG-DocOwl1.5를 출시했습니다. 이 작품은 고해상도 이미지 텍스트 인식, 일반 문서 구조 이해, 지침 따르기, 외부 지식 도입이라는 4가지 주요 과제를 해결하기 위한 일련의 솔루션을 제안했습니다. 더 이상 고민하지 말고 먼저 효과를 살펴보겠습니다. 복잡한 구조의 차트도 한 번의 클릭으로 인식하고 마크다운 형식으로 변환 가능: 다양한 스타일의 차트 사용 가능: 보다 자세한 텍스트 인식 및 위치 지정도 쉽게 처리 가능: 문서 이해에 대한 자세한 설명도 제공 가능: 아시다시피, " 문서 이해"는 현재 대규모 언어 모델 구현을 위한 중요한 시나리오입니다. 시장에는 문서 읽기를 지원하는 많은 제품이 있습니다. 그 중 일부는 주로 텍스트 인식을 위해 OCR 시스템을 사용하고 텍스트 처리를 위해 LLM을 사용합니다.

공장에서 일하는 테슬라 로봇, 머스크 : 올해 손의 자유도가 22도에 달할 것!

May 06, 2024 pm 04:13 PM

공장에서 일하는 테슬라 로봇, 머스크 : 올해 손의 자유도가 22도에 달할 것!

May 06, 2024 pm 04:13 PM

테슬라의 로봇 옵티머스(Optimus)의 최신 영상이 공개됐는데, 이미 공장에서 작동이 가능한 상태다. 정상 속도에서는 배터리(테슬라의 4680 배터리)를 다음과 같이 분류합니다. 공식은 또한 20배 속도로 보이는 모습을 공개했습니다. 작은 "워크스테이션"에서 따고 따고 따고 : 이번에 출시됩니다. 영상에는 옵티머스가 공장에서 이 작업을 전 과정에 걸쳐 사람의 개입 없이 완전히 자율적으로 완료하는 모습이 담겨 있습니다. 그리고 Optimus의 관점에서 보면 자동 오류 수정에 중점을 두고 구부러진 배터리를 집어 넣을 수도 있습니다. NVIDIA 과학자 Jim Fan은 Optimus의 손에 대해 높은 평가를 했습니다. Optimus의 손은 세계의 다섯 손가락 로봇 중 하나입니다. 가장 능숙합니다. 손은 촉각적일 뿐만 아니라

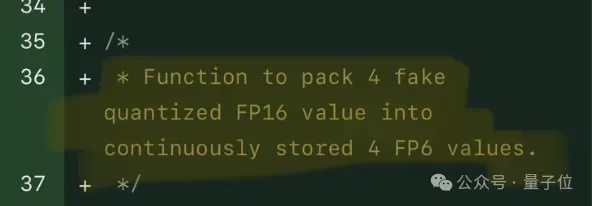

단일 카드는 듀얼 카드보다 Llama를 70B 더 빠르게 실행합니다. Microsoft는 A100에 FP6을 넣었습니다 |

Apr 29, 2024 pm 04:55 PM

단일 카드는 듀얼 카드보다 Llama를 70B 더 빠르게 실행합니다. Microsoft는 A100에 FP6을 넣었습니다 |

Apr 29, 2024 pm 04:55 PM

FP8 이하의 부동 소수점 수량화 정밀도는 더 이상 H100의 "특허"가 아닙니다! Lao Huang은 모든 사람이 INT8/INT4를 사용하기를 원했고 Microsoft DeepSpeed 팀은 NVIDIA의 공식 지원 없이 A100에서 FP6을 실행하기 시작했습니다. 테스트 결과에 따르면 A100에 대한 새로운 방법 TC-FPx의 FP6 양자화는 INT4에 가깝거나 때로는 더 빠르며 후자보다 정확도가 더 높은 것으로 나타났습니다. 또한 오픈 소스로 제공되고 DeepSpeed와 같은 딥 러닝 추론 프레임워크에 통합된 엔드투엔드 대규모 모델 지원도 있습니다. 이 결과는 대형 모델 가속화에도 즉각적인 영향을 미칩니다. 이 프레임워크에서는 단일 카드를 사용하여 Llama를 실행하면 처리량이 듀얼 카드보다 2.65배 더 높습니다. 하나