linux vcs는 파형을 시뮬레이션하고 보는 데 사용되는 컴파일된 Verilog 시뮬레이터입니다. 이는 창의 modelsim 및 Questasim은 물론 quartus 및 vivado 시뮬레이션 작업과 같은 도구와 유사합니다.

이 튜토리얼의 운영 환경: linux5.9.8 시스템, Dell G3 컴퓨터.

리눅스 vcs란 무엇인가요?

VCS 도구의 기본 사용

VCS은 Linux에서 파형을 시뮬레이션하고 보는 데 사용되는 도구로, 창의 modelsim 및 Questasim은 물론 quartus 및 vivado 시뮬레이션과 유사한 도구입니다. 작동하다.

vcs의 공통 명령어 접미어

| 명령 | 의미 |

|---|---|

-l readme.log -l readme.log

|

用于将编译产生的信息放在log文件内 |

+v2k |

是使VCS兼容verilog 2001以前的标准 |

-debug_all |

用于产生debug所需的文件 |

-f verilog_file.f |

可将.f文件里的源码全部编译 |

-R |

编译后立即运行,即编译完成后立即执行 ./simv |

-Mupdate |

源文件有修改时,只重新编译有改动的**.v**文件,节约编译时间。 |

-sverilog |

打开对Systemverilog的支持,编译Systemverilog文件时使用。 |

-timescale=1ns/1ns |

设置仿真精度 |

-o simv_file |

编译默认产生的可执行文件为simv,可以使用 -o 更改可执行文件名。如果这里修改执行仿真时候就不是使用simv而是对应的o名字了。 |

simv的常见指令

| 指令 | 含义 |

|---|---|

./simv -l run.log |

执行的日志文件保存 |

./simv -gui | 다음 용도로 사용됨 컴파일로 생성된 정보를 로그 파일에 넣으세요

-debug_all🎜 이전의 Verilog와 호환되도록 하는 표준입니다. 🎜디버깅에 필요한 파일을 생성하기 위해 사용합니다🎜🎜🎜🎜-f verilog_file.f🎜🎜.f 파일의 모든 소스 코드를 컴파일할 수 있습니다🎜🎜🎜🎜-R🎜🎜 컴파일 직후 실행, 즉 컴파일 직후 실행 🎜./simv🎜🎜🎜🎜🎜-Mupdate🎜🎜소스 파일 수정 시 수정된 **.v*만 * 파일이 다시 컴파일되므로 컴파일 시간이 절약됩니다. 🎜🎜🎜🎜-sverilog🎜🎜 🎜Systemverilog🎜 지원을 켜고 🎜Systemverilog🎜 파일을 컴파일할 때 사용하세요. 🎜🎜🎜🎜-timescale=1ns/1ns🎜🎜시뮬레이션 정확도 설정🎜🎜🎜🎜-o simv_file🎜🎜컴파일로 생성된 기본 실행 파일은 🎜simv🎜입니다. 실행 파일 이름은 🎜-o🎜를 사용하여 변경할 수 있습니다. 여기서 수정하시면 시뮬레이션 실행시 🎜simv🎜가 아닌 해당 o 이름을 사용하게 됩니다. 🎜🎜🎜🎜🎜🎜simv의 공통 명령🎜🎜🎜🎜🎜🎜Command 🎜🎜 의미🎜🎜🎜🎜🎜🎜./simv -l run.log🎜🎜실행 로그 파일을 저장합니다. 🎜 🎜 🎜🎜./simv -gui🎜🎜그래픽 인터페이스로 열기🎜🎜🎜🎜 사용 예는 full adder 공식 튜토리얼을 기반으로 합니다. 먼저 스크립트를 사용하지 않는 실행 과정을 소개합니다.

(1) 먼저 vcs를 실행하고 해당 full_adder 파일을 추가합니다. vcs加入对应的full_adder文件

vcs -sverilog -debug_all -timescale=1ns/1ps full_adder.v full_adder_tb.v -l com.log

这里先写full_adder.v 是因为tb文件需要调用它,所以把被调用的文件先写出来,这条语句会生成simv文件(如果使用了-o simv_file会生成对应的文件名字)。

(2)可以用./simv文件执行波形的界面,也可以采用下面指令以后台方式打开一个界面。

dve &或者 ./simv -l run.log -gui

(3)如果以./simv执行会直接看到波形文件,如果使用dve & 需要自行加入simv

.PHONY:vcs sim dve clean

OUTPUT = adder

VCS = vcs -sverilog +v2k -timescale=1ns/1ns \

-debug_all \

-o ${OUTPUT} \

-l compile.log \SIM = ./${OUTPUT} -l run.log

vcs: ${VCS} -f verilog_file.f

sim: ${SIM}dve:

dve -vpd vcdplus.vpd & clean: rm -rf *.log csrc simv* *.key *.vpd DVEfiles coverage *.vdb-o simv_file을 사용하면 해당 파일 이름이 생성됩니다).  (2)

(2) ./simv 파일을 사용하여 파형 인터페이스를 실행하거나 다음 명령을 사용하여 백그라운드에서 인터페이스를 열 수 있습니다. find -name ".*v" > file.list

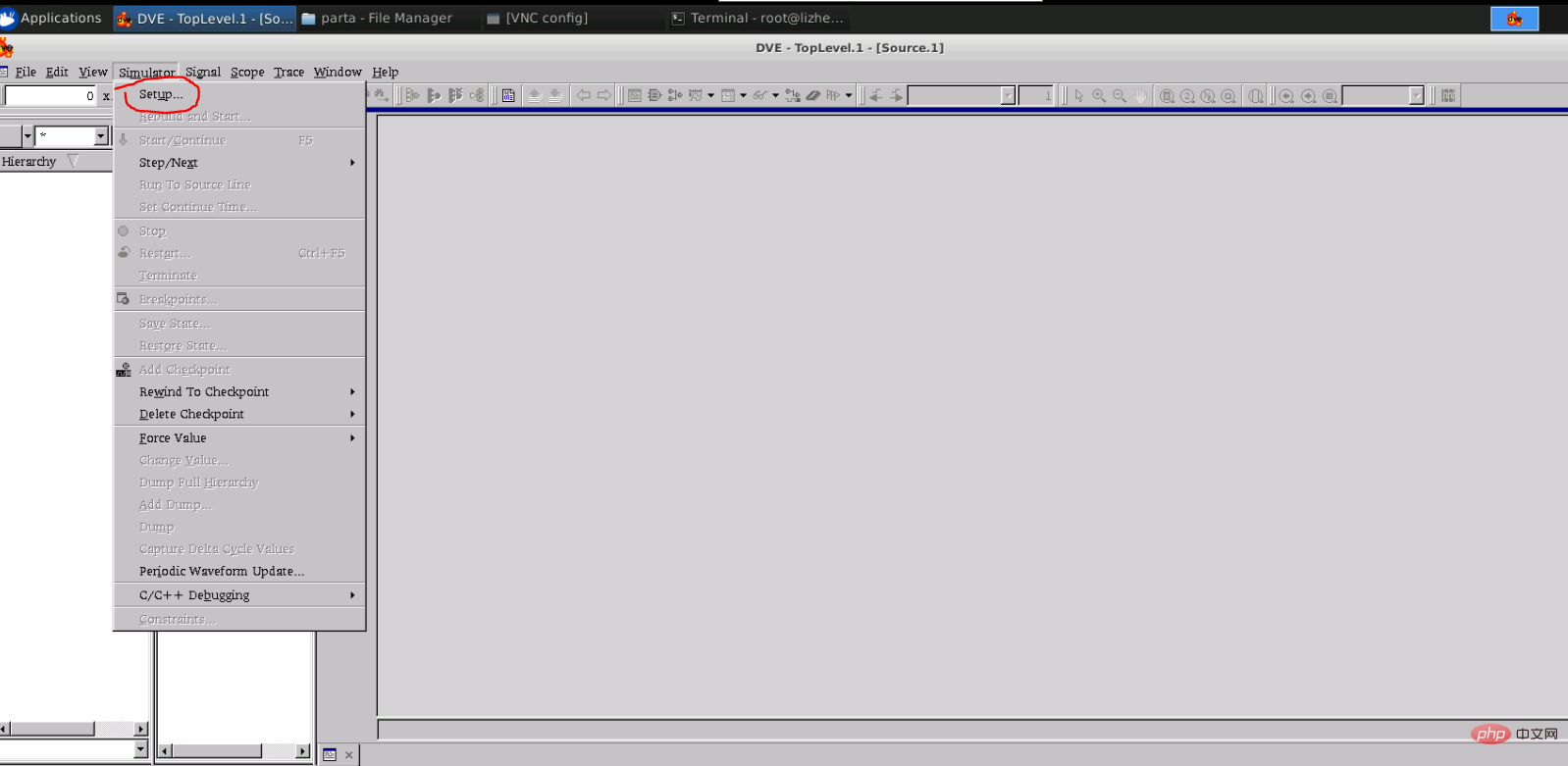

./simv로 실행하면 웨이브 파일이 바로 보입니다. dve&를 사용한다면 를 추가해야 합니다. >simv 파일을 직접 확인하고 simulator->Setup을 선택한 다음 생성된 simv ctrl+d

ctrl+d 넷째: 누가 운전했는지 추적

위 내용은 리눅스 VCS 란 무엇입니까?의 상세 내용입니다. 자세한 내용은 PHP 중국어 웹사이트의 기타 관련 기사를 참조하세요!