NVIDIA는 AI를 사용하여 GPU 연산 회로를 설계합니다. 이는 가장 발전된 EDA에 비해 면적을 25% 줄여 더 빠르고 효율적으로 만듭니다.

대규모 산술 회로 배열이 NVIDIA GPU를 구동하여 AI, 고성능 컴퓨팅 및 컴퓨터 그래픽의 전례 없는 가속을 가능하게 합니다. 따라서 이러한 산술 회로의 설계를 개선하는 것은 GPU 성능과 효율성을 향상시키는 데 매우 중요합니다. AI가 이러한 회로를 설계하는 방법을 학습한다면 어떨까요? 최근 NVIDIA 논문 "PrefixRL: Optimization of Parallel Prefix Circuits using Deep Reinforcement Learning"에서 연구원들은 AI가 이러한 회로를 처음부터 설계할 수 있을 뿐만 아니라 AI가 설계한 회로가 국가에서 설계한 회로보다 우수하다는 점을 입증했습니다. 최첨단 전자 설계 자동화(EDA) 도구는 더 작고 빠릅니다.

문서 주소: https://arxiv.org/pdf/2205.07000.pdf

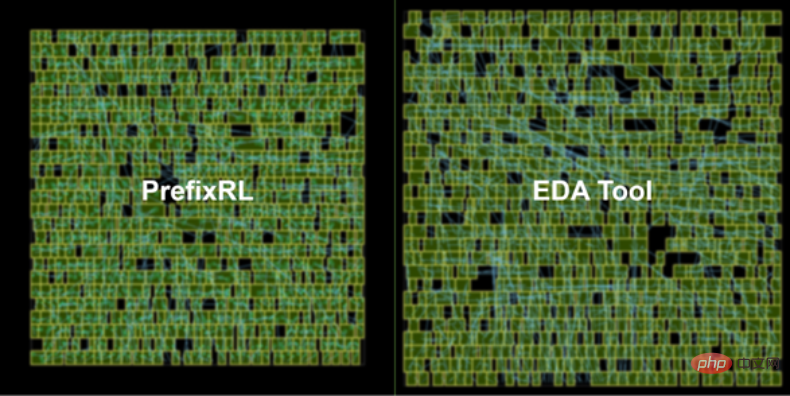

최신 NVIDIA Hopper GPU 아키텍처에는 약 13,000개의 AI 설계 회로 예제가 있습니다. 아래 그림 1: 왼쪽의 PrefixRL AI로 설계된 64b 가산기 회로는 그림 1의 오른쪽에 있는 가장 진보된 EDA 도구로 설계된 회로보다 25% 더 작습니다.

회로 설계 개요

컴퓨터 칩의 산술 회로는 논리 게이트(예: NAND, NOR 및 XOR)와 와이어의 네트워크로 구성됩니다. 이상적인 회로는 다음과 같은 특성을 가져야 합니다.

- 소형: 더 작은 면적, 더 많은 회로를 칩에 패키징할 수 있습니다.

- 빠름: 낮은 대기 시간, 향상된 칩 성능

- 더 낮은 전력 소비.

이 NVIDIA 연구에서 연구원들은 회로 영역과 대기 시간에 중점을 두었습니다. 그들은 전력 소비가 관심 있는 회로의 영역과 밀접한 관련이 있다는 것을 발견했습니다. 회로 영역과 지연은 종종 경쟁하는 속성이므로 이러한 속성을 효과적으로 상쇄하는 설계를 위해 파레토 프론티어를 찾는 것이 바람직합니다. 즉, 연구자들은 각 지연에서 회로 영역이 최소화되기를 원합니다.

따라서 PrefixRL에서 연구원들은 인기 있는 산술 회로 클래스인 병렬 접두사 회로에 중점을 둡니다. 가속기, 증분, 인코더 등 GPU의 다양한 중요 회로는 접두사 회로이며 상위 수준에서 접두사 그래프로 지정할 수 있습니다.

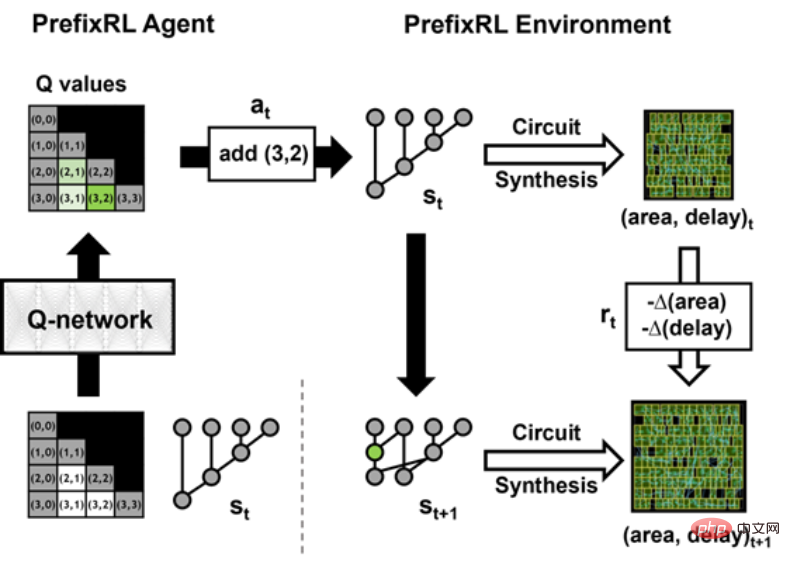

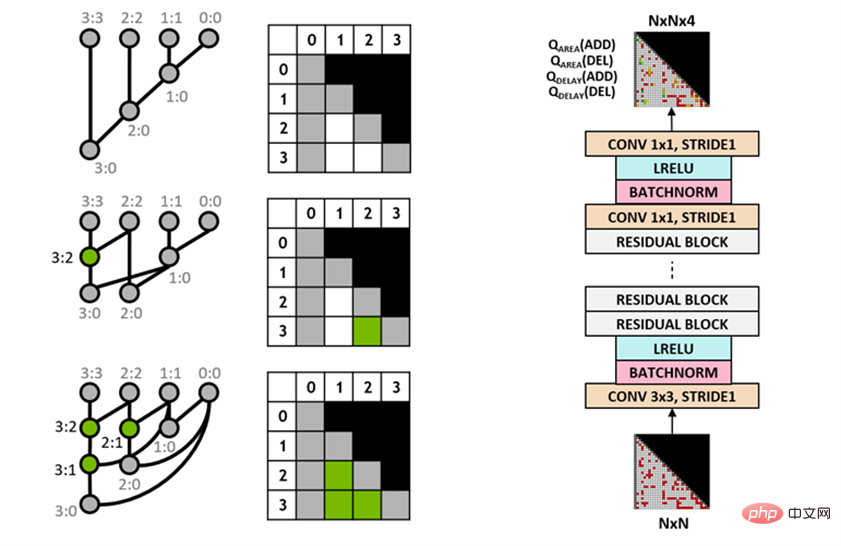

그럼 질문은 AI 에이전트가 좋은 접두사 이미지를 디자인할 수 있을까요? 모든 접두사 그래프의 상태 공간은 매우 크며 O(2^n^n)이며 무차별 대입 방법을 사용하여 탐색할 수 없습니다. 아래 그림 2는 4b 회로 인스턴스를 사용한 PrefixRL의 반복을 보여줍니다.

연구원들은 회로 생성기를 사용하여 접두사 다이어그램을 와이어와 논리 게이트가 있는 회로로 변환했습니다. 다음으로 생성된 회로는 게이트 크기, 복제, 버퍼 삽입 등 물리적 합성 최적화를 사용하는 물리적 합성 도구를 통해 최적화됩니다.

이러한 물리적 합성 최적화로 인해 최종 회로 속성(지연, 면적 및 전력)은 원래 접두사 그래프 속성(예: 레벨 및 노드 수)에서 직접 변환되지 않습니다. AI 에이전트가 접두사 그래프 설계 방법을 학습하면서도 접두사 그래프에서 생성된 최종 회로의 속성을 최적화하는 이유가 여기에 있습니다.

연구원들은 산술회로 설계를 강화 학습(RL) 작업으로 취급합니다. 여기서 에이전트는 산술회로의 영역 및 지연 속성을 최적화하도록 훈련됩니다. 접두사 회로의 경우 RL 에이전트가 접두사 그래프에서 노드를 추가하거나 제거한 후 다음 단계를 수행할 수 있는 환경을 설계했습니다.

- 접두사 그래프는 항상 올바른 접두사 합계 계산을 유지하도록 정규화됩니다. 정규화된 접두사 그래프에서 회로 생성

- 물리적 합성 도구를 사용하여 회로의 물리적 합성 최적화 수행

- 회로 영역 및 지연 특성을 측정합니다.

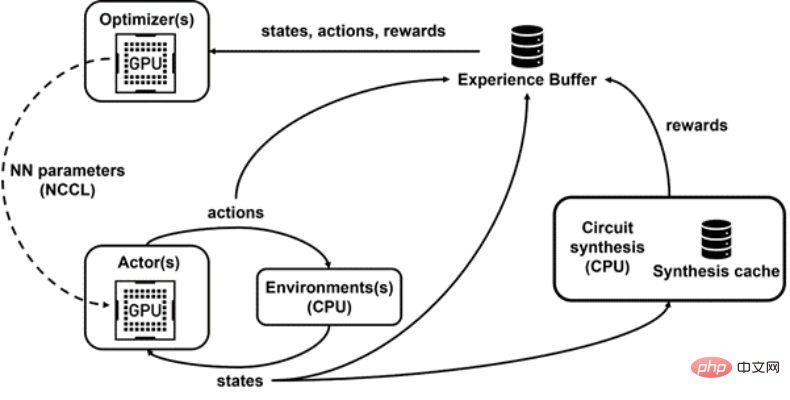

원본 사진은 인터랙티브 버전입니다. 연구원들은 Q-learning(Q-learning) 알고리즘을 사용하여 에이전트 회로 설계를 훈련합니다. 아래 그림 3에 표시된 것처럼 접두사 그래프를 그리드 표현으로 분해합니다. 여기서 그리드의 각 요소는 접두사 노드에 고유하게 매핑됩니다. 이 그리드는 Q 네트워크에 사용되는 입력과 출력을 나타냅니다. 입력 그리드의 각 요소는 노드의 존재 여부를 나타냅니다. 출력 그리드의 각 요소는 추가되거나 제거된 노드의 Q 값을 나타냅니다. 그림 3: 4b 접두사 그래프 표현(왼쪽) 및 완전 컨벌루션 Q-learning 에이전트 아키텍처(오른쪽). PrefixRL은 계산 집약적이며 물리 시뮬레이션에서 GPU당 256개의 CPU가 필요하고 64b 작업을 훈련하려면 32,000 GPU 시간 이상이 필요합니다. 이번에 NVIDIA는 이러한 종류의 산업 수준 강화 학습을 수행하기 위해 NVIDIA의 하드웨어 장점을 최대한 활용하는 내부 분산 강화 학습 플랫폼인 Raptor를 개발했습니다(아래 그림 4). 마지막으로 Raptor는 다중 스레드 서비스가 포함된 재생 버퍼와 같은 GPU 인식 데이터 구조를 제공하여 여러 작업자로부터 경험을 수신하고 데이터를 병렬로 배치하여 GPU에 미리 로드합니다. 그림 4: 연구원들은 Raptor를 사용하여 병렬 훈련과 보상 계산을 분리하여 회로 합성 지연을 극복합니다. 연구원들은 면적 목표와 지연 목표를 결합하기 위해 균형 가중치 w(범위 [0,1])를 사용했습니다. 파레토 프론티어를 얻기 위해 다양한 가중치를 가진 다양한 에이전트를 훈련하여 영역과 대기 시간 간의 균형을 맞춥니다. 그러나 물리적 합성을 수행하는 것은 느린 프로세스(64b 가산기의 경우 ~35초)이므로 RL 훈련 및 탐색 속도가 크게 느려질 수 있습니다. 아래 그림 5는 최첨단 EDA 도구의 PrefixRL과 파레토 지배 가산기 회로를 사용하여 설계된 64b 가산기 회로의 면적과 지연을 보여줍니다. 그림 5: PrefixRL로 설계한 산술 회로는 최첨단 EDA 도구로 설계한 회로보다 작고 빠릅니다. (왼쪽) 회로 아키텍처, (오른쪽) 해당 64b 가산기 회로 특성 다이어그램 이것이 심층 강화 학습 에이전트를 사용하여 산술 회로를 설계하는 첫 번째 방법인 것으로 이해됩니다. NVIDIA는 실제 회로 설계 문제에 AI를 적용하고, 작업 공간, 상태 표현, RL 에이전트 모델을 구축하고, 여러 경쟁 목표에 맞게 최적화하고, 느린 보상 계산을 극복하기 위한 청사진을 구상합니다.

완전 컨벌루션 Q-learning 에이전트

Q 학습 에이전트의 입력과 출력이 그리드 표현이기 때문에 연구원은 완전 컨벌루션 신경망 아키텍처를 사용합니다. 훈련 중에 면적과 지연에 대한 보상을 별도로 관찰할 수 있으므로 에이전트는 면적과 지연 속성에 대한 Q 값을 별도로 예측합니다.

분산 훈련을 위한 Raptor

Raptor는 작업 스케줄링, 맞춤형 네트워크 및 GPU 인식 데이터 구조와 같은 훈련 모델의 확장성과 훈련 속도를 향상시킬 수 있습니다. PrefixRL의 맥락에서 Raptor는 CPU, GPU 및 스팟 인스턴스 전반에 걸쳐 하이브리드 할당을 지원합니다. 이 강화 학습 애플리케이션의 네트워크는 다양하며 다음과 같은 이점이 있습니다.

아래 그림 4는 PrefixRL 프레임워크가 동시 훈련 및 데이터 수집을 지원하고 NCCL을 활용하여 참가자(아래 그림의 배우)에게 최신 매개변수를 효율적으로 전송하는 것을 보여줍니다.

보상 계산

RL 환경에서 물리적으로 합성된 최적화는 영역과 대기 시간을 절충하는 다양한 솔루션을 생성할 수 있습니다. 연구자들은 특정 에이전트를 훈련하는 데 사용되는 것과 동일한 균형 가중치를 사용하여 물리적 합성 도구를 구동합니다.

보상 계산 루프에서 물리적 합성 최적화를 수행하면 다음과 같은 이점이 있습니다.

에이전트가 조치를 취하려면 회로 합성이나 이전 보상 없이 현재 접두사 그래프 상태만 필요하기 때문에 연구원들은 상태 업데이트에서 보상 계산을 분리합니다. Raptor 덕분에 긴 보상 계산을 CPU 작업자 풀에 오프로드하여 물리 합성을 병렬로 수행할 수 있으며, 행위자 에이전트는 대기 없이 환경에서 실행할 수 있습니다.

CPU 작업자가 보상을 반환하면 변환이 재생 버퍼에 포함될 수 있습니다. 상태가 다시 발생할 때 중복 계산을 피하기 위해 포괄적인 보상이 캐시됩니다. 결과 및 전망

최고의 PrefixRL 가산기는 동일한 대기 시간에 EDA 도구 가산기보다 25% 더 적은 영역을 달성합니다. 물리적 합성 최적화 이후 파레토 최적 가산기 회로에 매핑된 이러한 접두사 그래프는 불규칙한 구조를 가지고 있습니다.

위 내용은 NVIDIA는 AI를 사용하여 GPU 연산 회로를 설계합니다. 이는 가장 발전된 EDA에 비해 면적을 25% 줄여 더 빠르고 효율적으로 만듭니다.의 상세 내용입니다. 자세한 내용은 PHP 중국어 웹사이트의 기타 관련 기사를 참조하세요!

핫 AI 도구

Undresser.AI Undress

사실적인 누드 사진을 만들기 위한 AI 기반 앱

AI Clothes Remover

사진에서 옷을 제거하는 온라인 AI 도구입니다.

Undress AI Tool

무료로 이미지를 벗다

Clothoff.io

AI 옷 제거제

Video Face Swap

완전히 무료인 AI 얼굴 교환 도구를 사용하여 모든 비디오의 얼굴을 쉽게 바꾸세요!

인기 기사

뜨거운 도구

메모장++7.3.1

사용하기 쉬운 무료 코드 편집기

SublimeText3 중국어 버전

중국어 버전, 사용하기 매우 쉽습니다.

스튜디오 13.0.1 보내기

강력한 PHP 통합 개발 환경

드림위버 CS6

시각적 웹 개발 도구

SublimeText3 Mac 버전

신 수준의 코드 편집 소프트웨어(SublimeText3)

뜨거운 주제

7681

7681

15

15

1393

1393

52

52

1209

1209

24

24

91

91

11

11

73

73

19

19

Web3 Trading Platform Ranking_Web3 글로벌 교환 상위 10 개 요약

Apr 21, 2025 am 10:45 AM

Web3 Trading Platform Ranking_Web3 글로벌 교환 상위 10 개 요약

Apr 21, 2025 am 10:45 AM

Binance는 Global Digital Asset Trading Ecosystem의 대 군주이며, 그 특성에는 다음이 포함됩니다. 1. 평균 일일 거래량은 1,500 억 달러를 초과하여 주류 통화의 98%를 차지하며 500 개의 거래 쌍을 지원합니다. 2. 혁신 매트릭스는 파생 상품 시장, Web3 레이아웃 및 교육 시스템을 포함합니다. 3. 기술적 이점은 밀리 초에 일치하는 엔진이며, 최고 처리량은 초당 140 만 건의 트랜잭션입니다. 4. 규정 준수 진행 상황은 15 개국 라이센스를 보유하고 있으며 유럽과 미국에 준수 엔티티를 설립합니다.

Worldcoin (WLD) 가격 예측 2025-2031 : WLD가 2031 년까지 4 달러에 도달 할 것인가?

Apr 21, 2025 pm 02:42 PM

Worldcoin (WLD) 가격 예측 2025-2031 : WLD가 2031 년까지 4 달러에 도달 할 것인가?

Apr 21, 2025 pm 02:42 PM

Worldcoin (WLD)은 Cryptocurrency 시장에서 고유 한 생체 인정 및 개인 정보 보호 메커니즘으로 눈에 띄고 많은 투자자의 관심을 끌고 있습니다. WLD는 혁신적인 기술, 특히 OpenAi 인공 지능 기술과 함께 Altcoins에서 뛰어난 성과를 거두었습니다. 그러나 향후 몇 년 안에 디지털 자산은 어떻게 행동 할 것인가? WLD의 미래 가격을 함께 예측합시다. 2025 WLD 가격 예측은 2025 년 WLD에서 상당한 성장을 달성 할 것으로 예상됩니다. 시장 분석에 따르면 평균 WLD 가격은 최대 $ 1.36로 $ 1.31에 도달 할 수 있습니다. 그러나 곰 시장에서 가격은 약 $ 0.55로 떨어질 수 있습니다. 이러한 성장 기대는 주로 WorldCoin2에 기인합니다.

통화에서 레버리지 교환 순위 순위 서클 통화 서클에서 상위 10 개의 레버리지 거래소의 최신 권장 사항

Apr 21, 2025 pm 11:24 PM

통화에서 레버리지 교환 순위 순위 서클 통화 서클에서 상위 10 개의 레버리지 거래소의 최신 권장 사항

Apr 21, 2025 pm 11:24 PM

2025 년에 레버리지 거래, 보안 및 사용자 경험에서 뛰어난 성능을 보이는 플랫폼은 다음과 같습니다. 1. OKX, 고주파 거래자에게 적합하여 최대 100 배의 레버리지를 제공합니다. 2. Binance, 전 세계의 다중 통화 거래자에게 적합하며 125 배 높은 레버리지를 제공합니다. 3. Gate.io, 전문 파생 상품 플레이어에게 적합하며 100 배의 레버리지를 제공합니다. 4. 초보자 및 소셜 트레이더에게 적합한 Bitget, 최대 100 배의 레버리지를 제공합니다. 5. 크라켄은 꾸준한 투자자에게 적합하며 5 배의 레버리지를 제공합니다. 6. Bybit, Altcoin Explorers에 적합하며 20 배의 레버리지를 제공합니다. 7. 저비용 거래자에게 적합한 Kucoin, 10 배의 레버리지를 제공합니다. 8. 비트 피 넥스, 시니어 플레이에 적합합니다

크로스 체인 거래는 무엇을 의미합니까? 크로스 체인 거래는 무엇입니까?

Apr 21, 2025 pm 11:39 PM

크로스 체인 거래는 무엇을 의미합니까? 크로스 체인 거래는 무엇입니까?

Apr 21, 2025 pm 11:39 PM

크로스 체인 거래를 지원하는 교환 : 1. Binance, 2. Uniswap, 3. Sushiswap, 4. Curve Finance, 5. Thorchain, 6. 1inch Exchange, 7. DLN 거래,이 플랫폼은 다양한 기술을 통해 다중 체인 자산 거래를 지원합니다.

가상 통화 가격의 상승 또는 하락은 왜입니까? 가상 통화 가격의 상승 또는 하락은 왜입니까?

Apr 21, 2025 am 08:57 AM

가상 통화 가격의 상승 또는 하락은 왜입니까? 가상 통화 가격의 상승 또는 하락은 왜입니까?

Apr 21, 2025 am 08:57 AM

가상 통화 가격 상승의 요인은 다음과 같습니다. 1. 시장 수요 증가, 2. 공급 감소, 3. 긍정적 인 뉴스, 4. 낙관적 시장 감정, 5. 거시 경제 환경; 감소 요인에는 다음이 포함됩니다. 1. 시장 수요 감소, 2. 공급 증가, 3. 부정적인 뉴스의 파업, 4. 비관적 시장 감정, 5. 거시 경제 환경.

Top 10 Cryptocurrency Exchange 플랫폼 세계 최대의 디지털 환전 목록

Apr 21, 2025 pm 07:15 PM

Top 10 Cryptocurrency Exchange 플랫폼 세계 최대의 디지털 환전 목록

Apr 21, 2025 pm 07:15 PM

거래소는 오늘날의 cryptocurrency 시장에서 중요한 역할을합니다. 그들은 투자자들이 거래 할 수있는 플랫폼 일뿐 만 아니라 시장 유동성 및 가격 발견의 중요한 원천이기도합니다. 세계 최대의 가상 환전 거래소는 상위 10 위이며, 이러한 거래소는 거래량이 훨씬 앞서있을뿐만 아니라 사용자 경험, 보안 및 혁신적인 서비스에서 고유 한 장점이 있습니다. 목록 위에있는 교환은 일반적으로 대규모 사용자 기반과 광범위한 시장 영향을 미치며 거래량 및 자산 유형은 종종 다른 거래소에서 도달하기가 어렵습니다.

환전 회계의 상위 10 개 플랫폼은 무엇입니까?

Apr 21, 2025 pm 12:21 PM

환전 회계의 상위 10 개 플랫폼은 무엇입니까?

Apr 21, 2025 pm 12:21 PM

최고 거래소에는 다음이 포함됩니다. 1. 세계 최대의 거래량 인 Binance는 600 개의 통화를 지원하며 스팟 취급 수수료는 0.1%입니다. 2. 균형 잡힌 플랫폼 인 OKX는 708 개의 거래 쌍을 지원하며 영구 계약 처리 수수료는 0.05%입니다. 3. Gate.io, 2700 개의 소규모 통화를 포괄하며 스팟 취급 수수료는 0.1%-0.3%입니다. 4. Coinbase, 미국 규정 준수 벤치 마크, 스팟 취급 수수료는 0.5%입니다. 5. Kraken, 최고 보안 및 정기 예약 감사.

Binance 전체 프로세스 전략에 대한 커널 에어 드롭 보상을받는 방법

Apr 21, 2025 pm 01:03 PM

Binance 전체 프로세스 전략에 대한 커널 에어 드롭 보상을받는 방법

Apr 21, 2025 pm 01:03 PM

암호 화폐의 번화 한 세계에서는 새로운 기회가 항상 나타납니다. 현재 Kerneldao (Kernel) 에어 드롭 활동은 많은 관심을 끌고 많은 투자자들의 관심을 끌고 있습니다. 그렇다면이 프로젝트의 기원은 무엇입니까? BNB 보유자는 어떤 이점을 얻을 수 있습니까? 걱정하지 마십시오. 다음은 당신을 위해 하나씩 공개 할 것입니다.