여기에 트랜지스터 생명선이 있습니다. 3D 적층 CMOS, 무어의 법칙이 앞으로 10년 동안 계속될까요?

트랜지스터는 "20세기 최고의 발명품"으로 알려져 있습니다.

그것의 출현은 집적 회로, 마이크로 프로세서 및 컴퓨터 메모리 생산의 토대를 마련했습니다.

1965년에 "무어의 법칙"이 제안되어 수십 년 동안 반도체 산업의 황금률이 되었습니다.

18~24개월마다 마이크로칩에 패키징되는 트랜지스터의 수가 두 배로 늘어나고, 칩의 성능도 두 배로 증가한다는 것을 보여줍니다.

그러나 새로운 프로세스 노드가 지속적으로 도입되면서 트랜지스터의 원자 수가 점점 줄어들고 있으며 다양한 물리적 한계로 인해 무어의 법칙이 더 발전하는 것을 제한하고 있습니다.

무어의 법칙이 끝났다고 생각하는 사람들도 있습니다.

따라서 무어의 법칙을 '살리기' 위해 엔지니어들은 트랜지스터 구조를 바꾸고, 면적과 소비전력을 지속적으로 줄여 성능을 향상시켜야 합니다.

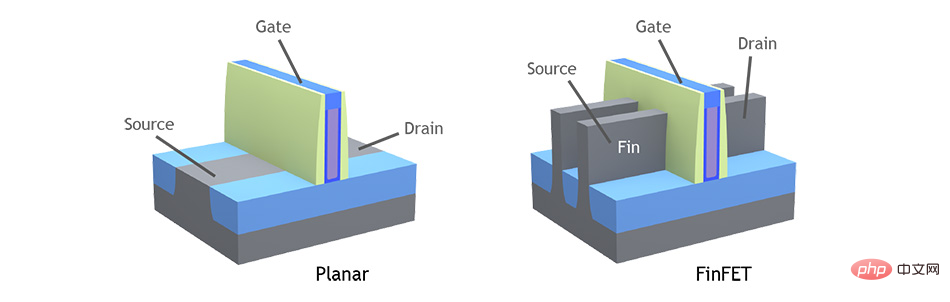

20세기 후반에는 평면 트랜지스터 설계(Planar Transistor)가 주로 유행했습니다. 2010년대에 들어서면서 점차 평면 디자인을 3D 핀 형태의 디바이스가 대체하게 되었습니다.

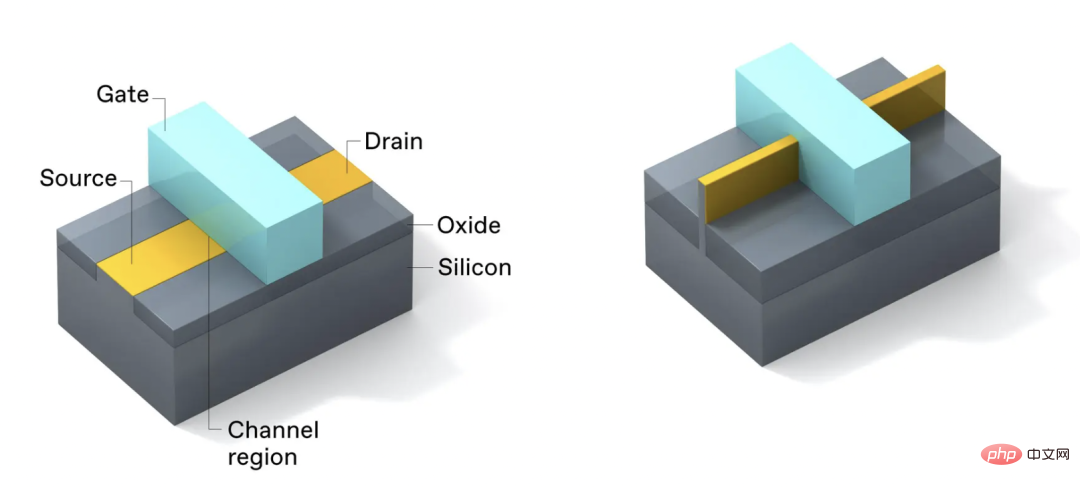

이제 완전히 새로운 트랜지스터 설계 구조인 GAA(Gate-All-Around Transistor)가 FinFET의 후속 제품으로 곧 생산에 들어갑니다.

하지만 좀 더 지켜봐야 합니다. Intel이 제안한 새로운 트랜지스터 아키텍처인 RibbonFET을 사용하더라도 크기를 줄이는 데는 한계가 있기 때문입니다.

3D 적층형 상보형 금속 산화물 반도체(CMOS) 또는 CFET(상보형 전계 효과 트랜지스터)가 무어의 법칙을 향후 10년까지 확장하는 열쇠가 될 것이라고 믿습니다.

트랜지스터의 진화

모든 금속 산화물 반도체 전계 효과 트랜지스터(MOSFET)에는 동일한 기본 구성 요소 세트가 있습니다.

게이트 스택, 채널 영역(채널 영역), 소스, 드레인

소스와 드레인은 화학적으로 도핑되어 이동형 전자가 풍부하거나(n형), 전자가 부족(p형)합니다. 채널 영역은 소스 및 드레인과 반대 방향으로 도핑됩니다.

2011년 이전 고급 마이크로프로세서의 트랜지스터 평면 버전에서는 MOSFET의 게이트 스택이 채널 영역 바로 위에 있었고 전기장을 채널 영역에 투영하는 데 사용되었습니다.

게이트에 소스에 비해 충분히 큰 전압을 가하면 채널 영역에 이동 전하 캐리어 층이 형성되어 소스와 드레인 사이에 전류가 흐를 수 있습니다.

평면 트랜지스터 설계의 크기를 줄이기 위해 "단채널 효과"가 물리학자들의 초점이 되었습니다.

공정 기술이 계속해서 향상되면서 트랜지스터의 게이트 전극 폭이 점점 작아지고 있습니다. 아시다시피, 게이트가 20nm보다 낮으면 전류는 제어할 수 없게 되고 소스 전류는 게이트를 관통하여 드레인에 직접 도달하게 됩니다.

이때 "누출"이 발생하여 칩의 에너지 소비가 급격히 증가합니다.

이 문제를 해결하기 위해 새로운 FinFET 트랜지스터 기술이 제안되었습니다. 더 나은 정적 제어를 제공하기 위해 3면의 채널 주위에 게이트를 감쌉니다.

FinFET은 이전 세대 평면 아키텍처와 동일한 성능 수준에서 전력 소비를 약 50% 줄입니다. FinFET은 또한 더 빠르게 전환하여 37% 성능 향상을 제공합니다.

인텔은 2011년 출시한 22nm 노드에 FinFET를 도입하여 3세대 코어 프로세서 생산에 사용했습니다.

이후 FinFET은 무어의 법칙을 실현하는 주체가 되었습니다.

하지만 FinFET으로 전환하면서 우리도 잃은 것이 있었습니다.

평면 디바이스에서 트랜지스터의 폭은 포토리소그래피에 의해 정의되므로 매우 유연한 매개변수입니다.

그러나 FinFET에서는 트랜지스터 폭이 개별적으로 증가하며 한 번에 하나의 핀이 추가됩니다. 이 속성을 흔히 핀 양자화라고 합니다.

FinFET의 유연성에도 불구하고 핀 양자화는 여전히 중요한 설계 제약으로 남아 있습니다. 이를 둘러싼 설계 규칙과 성능 향상을 위해 더 많은 핀을 추가하려는 욕구로 인해 로직 셀의 전체 면적이 늘어나고 단일 트랜지스터를 완전한 로직 회로로 바꾸는 상호 연결 스택이 복잡해집니다.

또한 트랜지스터의 커패시턴스를 증가시켜 스위칭 속도를 감소시킵니다. 따라서 FinFET은 업계의 주력 제품으로서 우리에게 큰 도움이 되었지만 새롭고 더욱 세련된 접근 방식이 필요합니다.

물리학자들이 곧 출시될 3D 트랜지스터인 RibbonFET을 발명하게 된 것은 바로 이러한 접근 방식입니다.

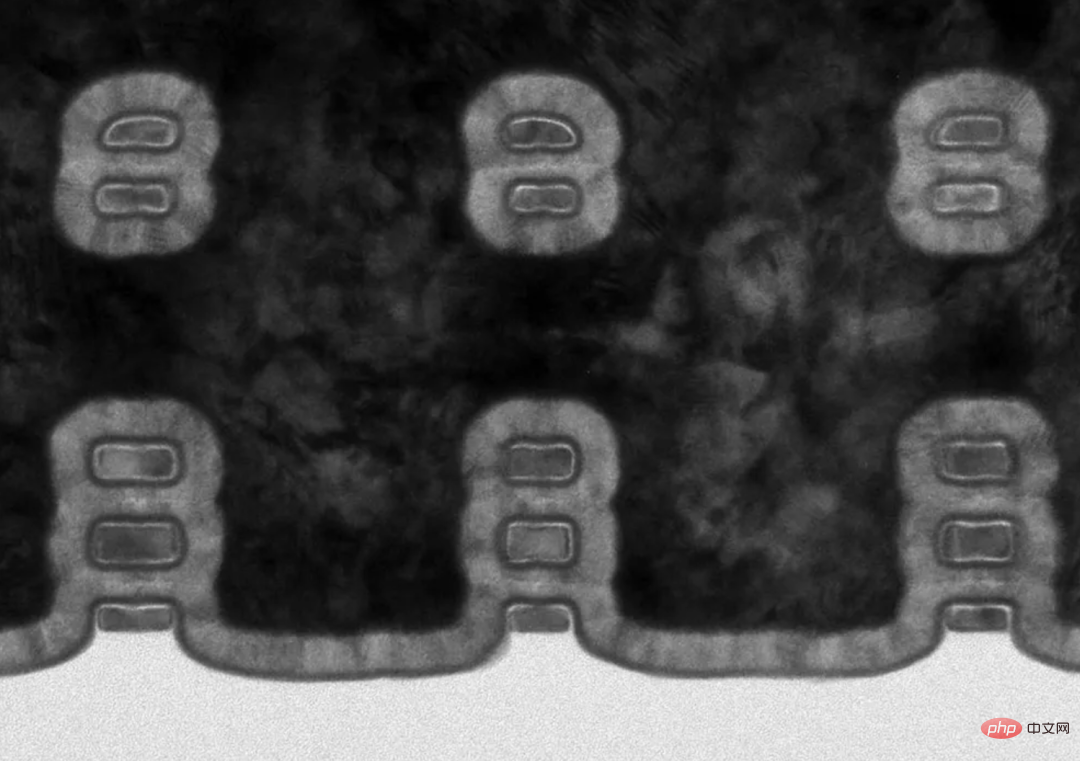

RibbonFET에서는 게이트가 트랜지스터 채널 영역을 둘러싸서 전하 캐리어 제어를 강화합니다. 새로운 구조는 또한 더 나은 성능과 보다 정교한 최적화를 가능하게 합니다.

구체적으로, 게이트는 채널을 완전히 둘러싸고 있어 채널 내의 전하 운반체를 더욱 엄격하게 제어할 수 있으며, 이는 이제 나노 크기의 실리콘 리본으로 형성됩니다.

이러한 나노리본(나노시트)을 이용하면 다시 포토리소그래피를 이용해 트랜지스터의 폭을 원하는 대로 바꾸는 것이 가능하다.

양자화 제약 조건을 제거한 후 애플리케이션에 적합한 크기의 너비를 생성할 수 있습니다. 이를 통해 전력, 성능, 비용의 균형을 맞출 수 있습니다.

더 중요한 것은 장치를 쌓아서 병렬로 작동함으로써 면적을 늘리지 않고도 장치가 더 많은 전류를 구동하고 성능을 향상시킬 수 있다는 것입니다.

따라서 인텔은 합리적인 전력으로 더 높은 성능을 달성하기 위해서는 RibbonFET이 최선의 선택이라고 믿습니다.

2024년에 Intel 20A 프로세스에 RibbonFET 구조를 도입할 예정입니다.

3D Stacked CMOS

Planar, FinFET, RibbonFET 트랜지스터의 공통점 중 하나는 모두 CMOS 기술을 사용한다는 것입니다. 앞서 언급했듯이 CMOS는 n형 트랜지스터와 p형 트랜지스터로 구성됩니다. . 이 기술은 다른 대안보다 훨씬 적은 전류를 소비하기 때문에 1980년대에 주류가 되었습니다. 전류가 적다는 것은 작동 주파수가 높고 트랜지스터 밀도가 높다는 것을 의미합니다.

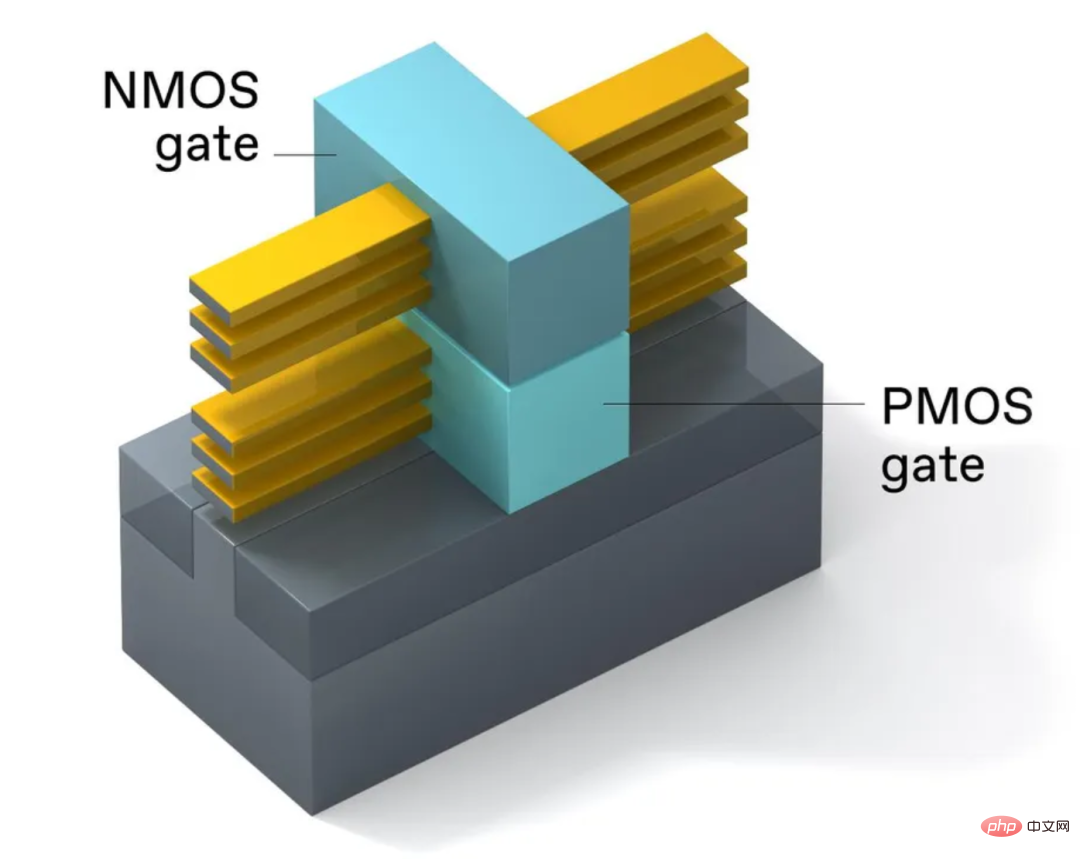

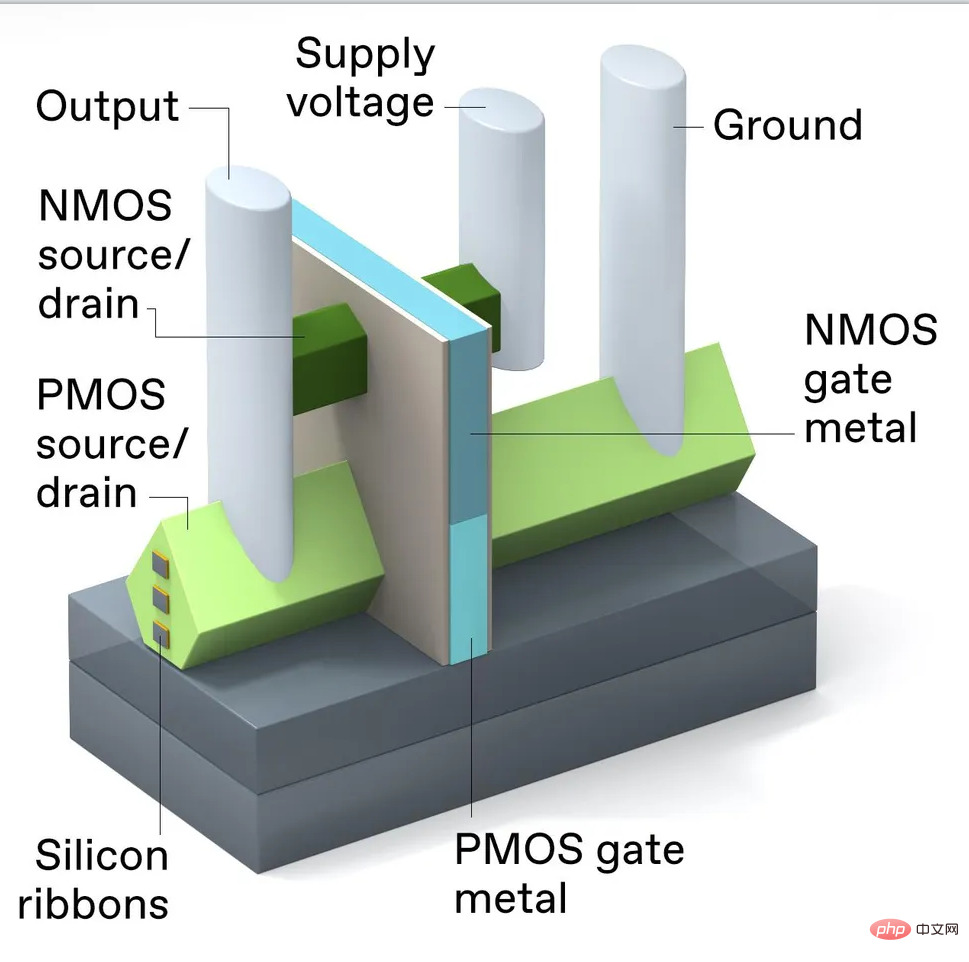

현재까지 모든 CMOS 기술은 NMOS 및 PMOS 트랜지스터의 표준 쌍을 나란히 배치했습니다. 그러나 2019년 IEEE 국제전자부품회의(IEDM) 기조연설에서는 PMOS 트랜지스터 위에 NMOS 트랜지스터를 배치하는 '3D 적층' 트랜지스터 개념이 제안됐다.

IEDM 2020에서는 이 3D 기술을 사용하여 논리 회로를 사용하여 설계된 최초의 인버터가 발표되었습니다. 3D 적층형 CMOS는 인버터 설치 공간을 효과적으로 절반으로 줄여 트랜지스터 면적 밀도를 두 배로 늘리고 무어의 법칙의 한계를 더욱 뛰어 넘습니다.

3D 적층형 CMOS 구조로 NMOS 장치 위에 PMOS 장치를 배치하고 전체 면적이 RibbonFET 면적 1개와 동일합니다. NMOS 및 PMOS 게이트는 서로 다른 금속 재료를 사용합니다.

3D 적층형 CMOS를 활용하려면 해결해야 할 프로세스 통합 문제가 많이 있으며, 그 중 일부는 CMOS 처리 및 제조의 한계와 관련이 있습니다.

어떻게 달성하나요? 자체 정렬된 3D CMOS 제작은 실리콘 웨이퍼에서 시작됩니다. 웨이퍼 위에 우리는 "초격자"라고 불리는 구조인 실리콘과 실리콘 게르마늄 층을 층층이 증착합니다. 그런 다음 포토리소그래픽 패턴을 사용하여 초격자의 일부를 잘라내어 지느러미 모양의 구조를 남깁니다. 초격자 결정은 후속 개발 프로세스를 위한 강력한 지원 구조를 제공합니다.

다음으로, 다음 작업으로부터 전자를 보호하기 위해 "가짜" 폴리실리콘이 초격자 위에 배치됩니다. 수직 적층형 이중 소스/드레인 공정으로 알려진 이 단계는 상단 나노리본(미래 NMOS 사이트)의 양쪽 끝에서 인 도핑된 실리콘을 성장시키는 동시에 하단 나노리본(미래 PMOS 사이트)에서 도핑된 실리콘을 선택적으로 성장시킵니다. 그런 다음 전원 주위에 유전체를 배치하여 방전을 통해 전원을 서로 격리시킵니다.

3D 스태킹은 제곱밀리미터당 CMOS 트랜지스터 밀도를 효과적으로 두 배로 늘리며, 실제 밀도는 관련된 로직 셀의 복잡성에 따라 달라집니다.

드디어 문 공사가 시작됩니다. 먼저 이전에 설치된 거짓 도어를 제거하여 실리콘 나노리본을 노출시킵니다. 다음으로, 실리콘 게르마늄만 에칭되어 트랜지스터의 채널 영역인 평행한 실리콘 나노리본 더미가 형성됩니다.

그런 다음 나노리본의 네 면 모두에 매우 얇은 절연층을 코팅합니다. 이 절연층은 유전율이 높습니다. 나노리본 채널은 너무 작아서 평면 트랜지스터만큼 효율적으로 화학적으로 코팅할 수 없습니다.

금속을 사용하여 하단 나노리본을 둘러싸서 p-도핑 채널을 형성하고, 상단 나노리본은 다른 나노리본과 함께 n-도핑 채널을 형성합니다. 이러한 방식으로 게이트 스택이 구성되고 두 개의 트랜지스터가 설치됩니다.

이 과정은 복잡해 보일 수 있지만 다른 기술(Sequential 3D Stacking)보다 낫습니다. 후자를 사용하는 경우 NMOS 장치와 PMOS 장치를 별도의 웨이퍼에 장착한 다음 두 장치를 하나로 모아 PMOS 층을 NMOS 웨이퍼로 전사합니다. 자체 정렬된 3D 적층 방식은 처리 단계가 적고 제조 비용을 보다 엄격하게 제어할 수 있습니다.

그리고 더 중요한 것은 이 자체 정렬 방식으로 두 개의 웨이퍼를 연결할 때 발생할 수 있는 정렬 오류도 방지할 수 있다는 것입니다. 3D 적층형 CMOS에 필요한 모든 연결을 만드는 것은 매우 어렵습니다. 아래 장치 스택에서 전원을 연결해야 합니다. 설계상 NMOS 장치[위]와 PMOS 장치[아래]에는 별도의 소스/드레인 접점이 있지만 두 장치 모두 공통 게이트를 공유합니다.

NMOS와 PMOS 사이의 수직 간격을 최적화해야 한다는 점은 주목할 가치가 있습니다. 너무 짧으면 기생 용량이 증가하고, 너무 길면 상호 연결의 저항이 증가합니다. 두 장치 사이. 극단적인 상황에서는 회로 속도가 느려지고 더 많은 전력을 소비하게 됩니다.

IEDM 2021 컨퍼런스에서 American TEL Research Center가 발표한 것과 같은 많은 설계 연구에서는 3D CMOS의 제한된 공간 내에서 필요한 모든 상호 연결을 제공할 것을 제안하며, 이를 통해 논리 장치가 구성하는 영역을 크게 늘리지 않습니다. 연구 결과에 따르면 최고의 상호 연결 옵션을 찾는 데 혁신을 가져올 수 있는 기회가 많이 있습니다.

무어 법칙의 미래

스트립 전계 효과 트랜지스터와 3D CMOS를 사용하면 적어도 2024년과 그 이후까지 무어 법칙의 수명을 연장할 수 있는 명확한 경로가 있습니다.

무어의 법칙 제안자인 고든 무어는 2005년 인터뷰에서 “이루어진 진전에 가끔 놀랐다”고 인정했습니다.

"그 과정에서 이제 끝이라고 생각한 적도 있었지만, 우리 크리에이티브 엔지니어들이 그 어려움을 극복할 수 있는 방법을 생각해 냈습니다."

트랜지스터 제조 공정으로 FinFET를 거쳐, 지속적인 최적화를 통해 RibbonFET 시대를 맞이했고, 마침내 3D Stacked CMOS 공정으로 나아가게 되면서 Gordon Moore 씨에게 남은 놀라움이 곧 찾아올 것으로 예상됩니다.

위 내용은 여기에 트랜지스터 생명선이 있습니다. 3D 적층 CMOS, 무어의 법칙이 앞으로 10년 동안 계속될까요?의 상세 내용입니다. 자세한 내용은 PHP 중국어 웹사이트의 기타 관련 기사를 참조하세요!

핫 AI 도구

Undresser.AI Undress

사실적인 누드 사진을 만들기 위한 AI 기반 앱

AI Clothes Remover

사진에서 옷을 제거하는 온라인 AI 도구입니다.

Undress AI Tool

무료로 이미지를 벗다

Clothoff.io

AI 옷 제거제

AI Hentai Generator

AI Hentai를 무료로 생성하십시오.

인기 기사

뜨거운 도구

메모장++7.3.1

사용하기 쉬운 무료 코드 편집기

SublimeText3 중국어 버전

중국어 버전, 사용하기 매우 쉽습니다.

스튜디오 13.0.1 보내기

강력한 PHP 통합 개발 환경

드림위버 CS6

시각적 웹 개발 도구

SublimeText3 Mac 버전

신 수준의 코드 편집 소프트웨어(SublimeText3)

뜨거운 주제

7569

7569

15

15

1386

1386

52

52

87

87

11

11

61

61

19

19

28

28

107

107

자율주행 분야에서 Gaussian Splatting이 인기를 끌면서 NeRF가 폐기되기 시작한 이유는 무엇입니까?

Jan 17, 2024 pm 02:57 PM

자율주행 분야에서 Gaussian Splatting이 인기를 끌면서 NeRF가 폐기되기 시작한 이유는 무엇입니까?

Jan 17, 2024 pm 02:57 PM

위에 작성됨 및 저자의 개인적인 이해 3DGS(3차원 가우스플래팅)는 최근 몇 년간 명시적 방사선장 및 컴퓨터 그래픽 분야에서 등장한 혁신적인 기술입니다. 이 혁신적인 방법은 수백만 개의 3D 가우스를 사용하는 것이 특징이며, 이는 주로 암시적 좌표 기반 모델을 사용하여 공간 좌표를 픽셀 값에 매핑하는 NeRF(Neural Radiation Field) 방법과 매우 다릅니다. 명시적인 장면 표현과 미분 가능한 렌더링 알고리즘을 갖춘 3DGS는 실시간 렌더링 기능을 보장할 뿐만 아니라 전례 없는 수준의 제어 및 장면 편집 기능을 제공합니다. 이는 3DGS를 차세대 3D 재구성 및 표현을 위한 잠재적인 게임 체인저로 자리매김합니다. 이를 위해 우리는 처음으로 3DGS 분야의 최신 개발 및 관심사에 대한 체계적인 개요를 제공합니다.

Microsoft Teams의 3D Fluent 이모티콘에 대해 알아보기

Apr 24, 2023 pm 10:28 PM

Microsoft Teams의 3D Fluent 이모티콘에 대해 알아보기

Apr 24, 2023 pm 10:28 PM

특히 Teams 사용자라면 Microsoft가 업무 중심 화상 회의 앱에 새로운 3DFluent 이모티콘을 추가했다는 사실을 기억해야 합니다. Microsoft가 작년에 Teams 및 Windows용 3D 이모티콘을 발표한 후 실제로 플랫폼용으로 업데이트된 기존 이모티콘이 1,800개 이상 나타났습니다. 이 큰 아이디어와 Teams용 3DFluent 이모티콘 업데이트 출시는 공식 블로그 게시물을 통해 처음 홍보되었습니다. 최신 Teams 업데이트로 FluentEmojis가 앱에 제공됩니다. Microsoft는 업데이트된 1,800개의 이모티콘을 매일 사용할 수 있다고 밝혔습니다.

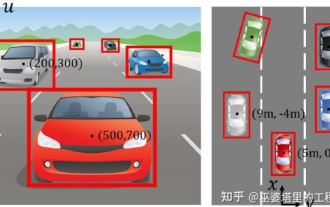

카메라 또는 LiDAR를 선택하시겠습니까? 강력한 3D 객체 감지 달성에 대한 최근 검토

Jan 26, 2024 am 11:18 AM

카메라 또는 LiDAR를 선택하시겠습니까? 강력한 3D 객체 감지 달성에 대한 최근 검토

Jan 26, 2024 am 11:18 AM

0. 전면 작성&& 자율주행 시스템은 다양한 센서(예: 카메라, 라이더, 레이더 등)를 사용하여 주변 환경을 인식하고 알고리즘과 모델을 사용하는 고급 인식, 의사결정 및 제어 기술에 의존한다는 개인적인 이해 실시간 분석과 의사결정을 위해 이를 통해 차량은 도로 표지판을 인식하고, 다른 차량을 감지 및 추적하며, 보행자 행동을 예측하는 등 복잡한 교통 환경에 안전하게 작동하고 적응할 수 있게 되므로 현재 널리 주목받고 있으며 미래 교통의 중요한 발전 분야로 간주됩니다. . 하나. 하지만 자율주행을 어렵게 만드는 것은 자동차가 주변에서 일어나는 일을 어떻게 이해할 수 있는지 알아내는 것입니다. 이를 위해서는 자율주행 시스템의 3차원 객체 감지 알고리즘이 주변 환경의 객체의 위치를 포함하여 정확하게 인지하고 묘사할 수 있어야 하며,

CLIP-BEVFormer: BEVFormer 구조를 명시적으로 감독하여 롱테일 감지 성능을 향상시킵니다.

Mar 26, 2024 pm 12:41 PM

CLIP-BEVFormer: BEVFormer 구조를 명시적으로 감독하여 롱테일 감지 성능을 향상시킵니다.

Mar 26, 2024 pm 12:41 PM

위에 작성 및 저자의 개인적인 이해: 현재 전체 자율주행 시스템에서 인식 모듈은 중요한 역할을 합니다. 자율주행 시스템의 제어 모듈은 적시에 올바른 판단과 행동 결정을 내립니다. 현재 자율주행 기능을 갖춘 자동차에는 일반적으로 서라운드 뷰 카메라 센서, 라이더 센서, 밀리미터파 레이더 센서 등 다양한 데이터 정보 센서가 장착되어 다양한 방식으로 정보를 수집하여 정확한 인식 작업을 수행합니다. 순수 비전을 기반으로 한 BEV 인식 알고리즘은 하드웨어 비용이 저렴하고 배포가 용이하며, 출력 결과를 다양한 다운스트림 작업에 쉽게 적용할 수 있어 업계에서 선호됩니다.

Windows 11의 Paint 3D: 다운로드, 설치 및 사용 가이드

Apr 26, 2023 am 11:28 AM

Windows 11의 Paint 3D: 다운로드, 설치 및 사용 가이드

Apr 26, 2023 am 11:28 AM

새로운 Windows 11이 개발 중이라는 소문이 퍼지기 시작했을 때 모든 Microsoft 사용자는 새 운영 체제가 어떤 모습일지, 어떤 결과를 가져올지 궁금해했습니다. 추측 끝에 Windows 11이 여기에 있습니다. 운영 체제에는 새로운 디자인과 기능 변경이 포함되어 있습니다. 일부 추가 기능 외에도 기능 지원 중단 및 제거가 함께 제공됩니다. Windows 11에 없는 기능 중 하나는 Paint3D입니다. 서랍, 낙서, 낙서에 적합한 클래식 페인트를 계속 제공하지만 3D 제작자에게 이상적인 추가 기능을 제공하는 Paint3D를 포기합니다. 몇 가지 추가 기능을 찾고 있다면 최고의 3D 디자인 소프트웨어로 Autodesk Maya를 추천합니다. 좋다

카드 한장으로 30초만에 가상 3D 아내를 만나보세요! Text to 3D는 Maya, Unity 및 기타 제작 도구와 원활하게 연결되어 명확한 모공 세부 정보를 갖춘 고정밀 디지털 휴먼을 생성합니다.

May 23, 2023 pm 02:34 PM

카드 한장으로 30초만에 가상 3D 아내를 만나보세요! Text to 3D는 Maya, Unity 및 기타 제작 도구와 원활하게 연결되어 명확한 모공 세부 정보를 갖춘 고정밀 디지털 휴먼을 생성합니다.

May 23, 2023 pm 02:34 PM

ChatGPT는 AI 산업에 닭의 피를 주입했고, 한때 상상할 수 없었던 모든 것이 오늘날 기본적인 관행이 되었습니다. 계속해서 발전하고 있는 Text-to-3D는 Diffusion(이미지), GPT(텍스트)에 이어 AIGC 분야의 차세대 핫스팟으로 평가되며 전례 없는 주목을 받고 있습니다. 아니요, ChatAvatar라는 제품은 공개 베타 버전으로 출시되어 빠르게 700,000회 이상의 조회수와 관심을 얻었으며 Spacesofttheweek에 소개되었습니다. △ChatAvatar는 AI가 생성한 단일 시점/다중 시점 원본 그림에서 3D 스타일화된 캐릭터를 생성하는 Imageto3D 기술도 지원합니다. 현재 베타 버전에서 생성된 3D 모델은 큰 주목을 받았습니다.

자율주행을 위한 3D 시각 인식 알고리즘의 심층 해석

Jun 02, 2023 pm 03:42 PM

자율주행을 위한 3D 시각 인식 알고리즘의 심층 해석

Jun 02, 2023 pm 03:42 PM

자율주행 응용을 위해서는 궁극적으로 3D 장면을 인식하는 것이 필요합니다. 그 이유는 간단합니다. 인간 운전자도 이미지를 바탕으로 운전할 수는 없습니다. 물체와의 거리, 장면의 깊이 정보는 2차원 인식 결과에 반영될 수 없기 때문에 이 정보는 자율주행 시스템이 주변 환경을 정확하게 판단하는 데 핵심이 된다. 일반적으로 자율주행차의 시각 센서(예: 카메라)는 차체 위쪽이나 차량 내부 백미러에 설치됩니다. 어디에 있든 카메라가 얻는 것은 투시 뷰(PerspectiveView)(세계 좌표계에서 이미지 좌표계로)에서 실제 세계를 투영하는 것입니다. 이 관점은 인간의 시각 시스템과 매우 유사합니다.

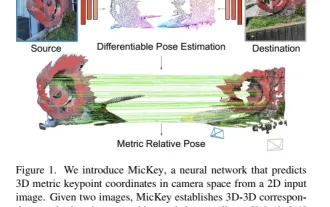

옥스포드 대학의 최신 소식! 미키: 3D SOTA로 2D 이미지 매칭! (CVPR\'24)

Apr 23, 2024 pm 01:20 PM

옥스포드 대학의 최신 소식! 미키: 3D SOTA로 2D 이미지 매칭! (CVPR\'24)

Apr 23, 2024 pm 01:20 PM

앞에 적힌 프로젝트 링크: https://nianticlabs.github.io/mickey/ 두 장의 사진이 주어지면 사진 간의 대응 관계를 설정하여 두 장의 사진 사이의 카메라 포즈를 추정할 수 있습니다. 일반적으로 이러한 대응은 2D에서 2D로 이루어지며 추정된 포즈는 규모에 따라 결정되지 않습니다. 언제 어디서나 즉각적인 증강 현실과 같은 일부 애플리케이션은 규모 측정항목의 포즈 추정이 필요하므로 규모를 복구하기 위해 외부 깊이 추정기에 의존합니다. 본 논문에서는 3차원 카메라 공간에서 메트릭 일치성을 예측할 수 있는 키포인트 매칭 프로세스인 MicKey를 제안합니다. 이미지 전반에 걸쳐 3D 좌표 매칭을 학습함으로써 측정 기준을 추론할 수 있습니다.