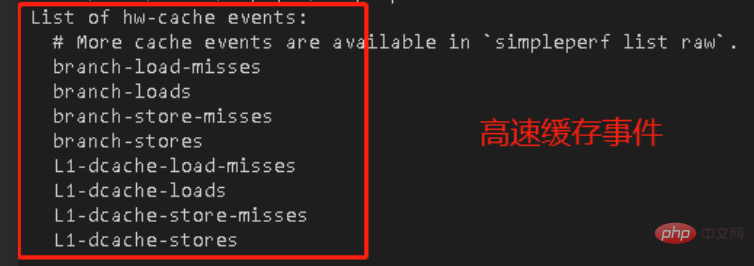

사실은 이렇습니다. 그때 리더님이 perf를 사용하는 과정에서 perf 하드웨어 성능 모니터링 작업을 주셨는데요. 다음 정보를 보았습니다.

내 임무는 이러한 캐시 이벤트를 정상적으로 계산하는 것인데, 핵심은 이것이 misses、loads의미가 전혀 무엇인지 모른다는 것입니다.

둘 다 캐시라는 것만 알고 있는데 이름이 너무 비슷하네요 차이점이 무엇인가요?

이런 이유로 캐시에 대해 배우는 것이 필요하다고 느꼈고, 캐시와 성능 등에 대한 이해는 여기서부터 시작되었습니다.

다음은 제가 캐시를 공부할 때 요약한 몇 가지 기본 개념 지식입니다. 기본 레이어나 캐시를 이해하지 못하는 사람들에게 도움이 될 것이라고 믿습니다.

기본적으로 질문이 많아서 안내해드린 적이 많아서 질문과 답변 형식으로 안내해드리겠습니다.

우선 CPU가 메모리에 직접 접근하지 않고 먼저 Cache를 거쳐야 한다는 점을 알아야 합니다. 왜일까요?

원인: CPU의 데이터는 레지스터에 저장됩니다. 레지스터에 액세스하는 속도는 매우 빠르지만 레지스터 용량은 작습니다. 메모리 용량은 크지만 속도가 느립니다. CPU와 메모리 사이의 속도와 용량 문제를 해결하기 위해 캐시가 도입되었습니다.

Cache는 CPU와 Main Memory 사이에 위치하며, CPU가 Main Memory에 접근할 때 먼저 Cache에 접근하여 해당 데이터가 있는지 확인하고, 존재한다면 Cache에서 데이터를 가져옵니다. Cache에 데이터가 없으면 CPU로 반환한 다음 주 메모리에 액세스합니다.

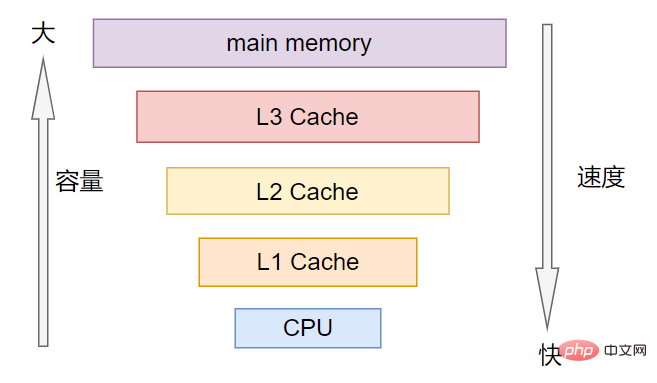

일반적으로 캐시가 하나가 아니라 여러 개, 즉 다단계 캐시가 존재하는 이유는 무엇일까요?

이유: CPU 액세스 캐시도 매우 빠릅니다. 그러나 속도와 용량 사이의 완전한 호환성을 달성할 수 없습니다. 캐시에 액세스하는 CPU의 속도가 레지스터에 액세스하는 CPU의 속도와 비슷하다면 캐시는 매우 빠르지만 용량은 매우 작다는 의미입니다. 작은 캐시 용량은 우리의 요구를 충족시키기에 충분하지 않으므로 다중 레벨 캐시가 도입되었습니다.

다중 레벨 캐시는 캐시를 L1, L2, L3 등의 여러 레벨로 나눕니다.

속도 순서는 L1>L2>L3 순입니다.

저장 용량에 따라 L3>L2>L1 순입니다.

L1은 CPU에 가장 가깝고 L3은 메인 메모리에 가장 가깝습니다.

보통 L1은 명령어 캐시(ICache) 및 데이터 캐시(<code style="font-size: 14px;padding: 2px 4px;border-radius: 4px;margin-right: 2px;margin-left: 2px; background-color: rgba(27, 31, 35, 0.05);글꼴 계열: " operator mono consolas monaco menlo monospace break-all rgb>DCache ), L1 캐시는 CPU 전용이며 각 CPU에는 L1 캐시가 있습니다. ICache)和data cache(DCache),并且L1 cache是cpu私有的,每个cpu都有一个L1 cache。

命中:CPU要访问的数据在cache中有缓存,称为“命中”,即cache hit

缺失:CPU要访问的数据在cache中没有缓存,称为“缺失”,即cache miss

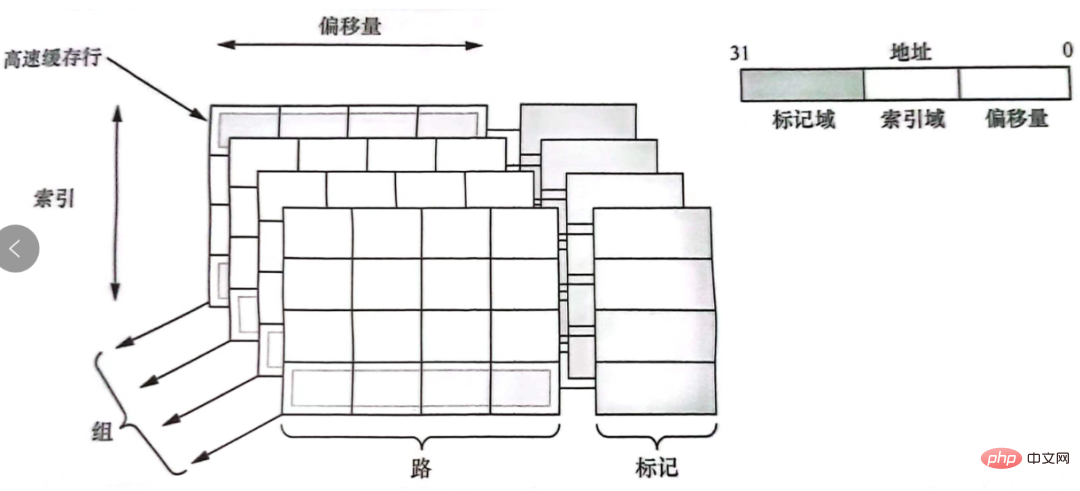

캐시 적중🎜🎜🎜missing🎜: CPU에서 액세스할 데이터가 캐시에 캐시되지 않습니다. "누락"이라고 합니다. 즉, 캐시 누락🎜캐시 라인: 높음 속도 캐시 라인은 캐시를 여러 개의 동일한 블록으로 나누고 각 블록의 크기를 캐시 라인. cache line:高速缓存行,将cache平均分成相等的很多块,每一个块大小称之为cache line。

cache line也是cache和主存之间数据传输的最小单位.

当CPU试图load一个字节数据的时候,如果cache缺失,那么cache控制器会从主存中一次性的load cache line大小的数据到cache中。例如,cache line大小是8字节。CPU即使读取一个byte,在cache缺失后,cache会从主存中load 8字节填充整个cache line。

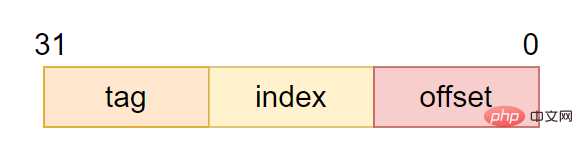

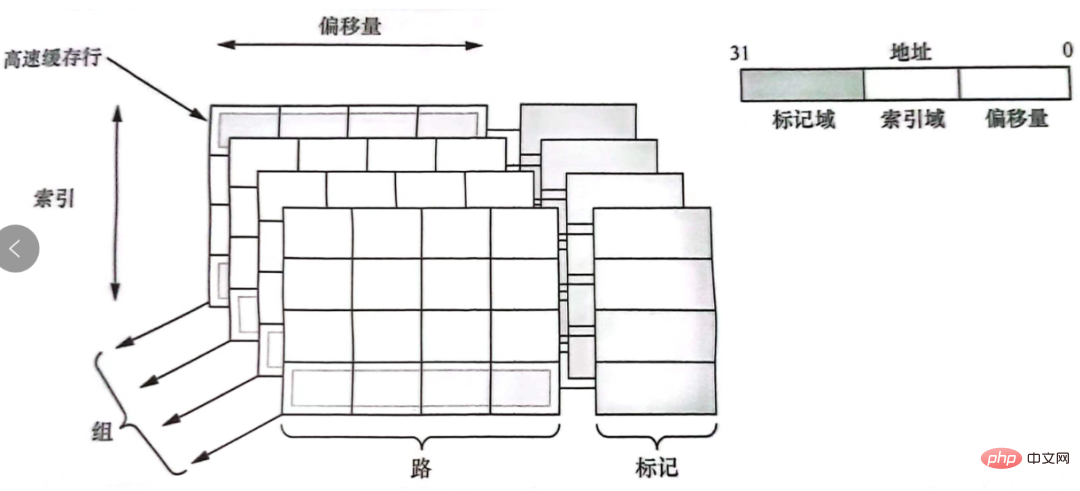

CPU访问cache时的地址编码,通常由tag、index和offset三部分组成:

tag(标记域):用于判断cache line缓存的数据的地址是否和处理器寻址地址一致。- index(索引域):用于索引和查找地址在高速缓存中的哪一行

offset캐시 라인은 캐시와 메인 메모리 사이의 데이터 전송의 가장 작은 단위이기도 합니다. CPU가 1바이트의 데이터를 로드하려고 할 때 캐시가 누락된 경우 캐시 컨트롤러는 메인 메모리에서 캐시 라인 크기의 데이터를 한 번에 캐시로 로드합니다. 예를 들어, 캐시 라인 크기는 8바이트입니다. CPU가 1바이트를 읽어도 캐시가 누락된 후 캐시는 메인 메모리에서 8바이트를 로드하여 전체 캐시 라인을 채웁니다.

tag(tag field)🎜: 캐시 라인 캐시를 결정하는 데 사용됩니다. 데이터 주소가 프로세서 주소 지정 주소와 일치하는지 여부. 🎜🎜🎜🎜- 색인 (인덱스 필드) 🎜: 주소가 있는 캐시의 행을 색인화하고 찾는 데 사용됩니다. 🎜오프셋🎜(오프셋) 🎜: 캐시 라인의 오프셋. 캐시 라인의 내용은 워드나 바이트로 주소를 지정할 수 있습니다. 🎜🎜🎜🎜캐시 라인과 태그, 인덱스, 오프셋 등의 관계는 그림과 같습니다. 🎜

우리는 CPU가 메모리에 직접 접근하지 않는다는 것을 알고 있지만, CPU가 가상 주소를 발급한 후 MMU에 의해 물리 주소로 변환되고, 물리 주소를 기반으로 메모리에서 데이터를 가져옵니다. . 그렇다면 캐시는 가상 주소에 접근하는 걸까요, 아니면 물리 주소에 접근하는 걸까요?

A: 반드시 그런 것은 아닙니다. 가상 주소, 물리적 주소 또는 가상 주소와 물리적 주소의 조합일 수 있습니다.

하드웨어 설계에서 캐시에는 여러 구성 방법이 있기 때문입니다.

VIVT가상 캐시VIVT虚拟高速缓存:虚拟地址的index,虚拟地址的tag。PIPT物理高速缓存:物理地址的index,物理地址的tag。VIPT物理标记的虚拟高速缓存:虚拟地址的index,物理地址的tag。歧义(homonyms: 가상 주소의 인덱스, 가상 주소의 태그.

PIPT code><strong style="color: black;">물리적 캐시 🎜: 물리적 주소의 인덱스, 물리적 주소의 태그. </strong>VIPT code><strong style="color: black;">물리적 태그의 가상 캐시 🎜: 가상 주소의 인덱스, 물리적 주소의 태그. </strong>

동음이의어 )🎜: 동일한 가상 주소는 다른 물리적 주소에 해당합니다🎜Alias (별칭)alias):多个虚拟地址映射到了相同的物理地址(多个虚拟地址被称为别名)。

例如上述VIVT方式就会存在别名问题,那VIVT、PIPT和VIPT那个方式更好呢?

PIPT其实是比较理想的,因为index和tag都使用了物理地址,软件层面不需要任何维护就能避免歧义和别名问题。

VIPT的tag使用了物理地址,所以不存在歧义问题,但index是虚拟地址,所以可能也存在别名问题。

而VIVT : 많은 가상 주소가 동일한 물리적 주소에 매핑됩니다(여러 개의 가상 주소를 별칭이라고 함). 예를 들어 위에서 언급한 VIVT 방법에는 별칭 문제가 있습니다. VIVT, PIPT 또는 VIPT 중 어떤 방법이 더 좋습니까?

PIPT가 실제로 더 이상적입니다. 왜냐하면 인덱스와 태그 모두 물리적 주소를 사용합니다. 모호함과 별칭 문제를 피하기 위해 소프트웨어 수준에서 유지 관리가 필요하지 않습니다.

그리고VIPT의 태그는 물리학을 사용합니다. 주소이므로 모호성 문제는 없지만, 인덱스는 가상 주소이므로 별칭 문제도 있을 수 있습니다.

VIVT 방식, 캐시 구성, 모호성 및 별칭 문제는 비교적 큰 콘텐츠입니다. 여기서는 캐시가 접근하는 주소가 가상 주소일 수도 있고, 물리적 주소일 수도 있고, 가상 주소와 물리적 주소의 조합일 수도 있다는 것만 알면 됩니다. 그리고 다양한 구성 방법에는 모호성과 별칭 문제가 있습니다.

🎜🎜🎜7. 캐시 할당 전략은? 🎜🎜 🎜🎜🎜🎜 캐시 미스가 발생한 경우 캐시를 할당하는 방법을 나타냅니다. 🎜🎜읽기 할당: CPU읽기 데이터, 발생캐시가 없습니다. 이 In 모든 경우에 캐시 라인데이터 캐시 주 메모리에서 읽습니다. CPU读数据时,发生cache缺失,这种情况下都会分配一个cache line缓存从主存读取的数据。默认情况下,cache都支持读分配。

写分配:当CPU写数据发生cache缺失时,才会考虑写分配策略。当我们不支持写分配的情况下,写指令只会更新主存数据,然后就结束了。当支持写分配的时候,我们首先从主存中加载数据到cache line中(相当于先做个读分配动作),然后会更新cache line기본적으로 캐시 모든 읽기 지원 배포 .

캐시 라인(먼저 읽기 할당을 수행하는 것과 동일), 캐시 라인의 데이터.

8. 캐시 업데이트 전략은?

은 캐시에 도달할 때 쓰기 작업이 데이터를 업데이트하는 방법을 나타냅니다.

🎜Write passthrough🎜: CPU가 저장 명령을 실행하고 캐시 적중이 발생하면 캐시의 데이터를 업데이트하고 메인 메모리의 데이터를 업데이트합니다. 🎜캐시와 메인 메모리의 데이터는 항상 일관됩니다🎜. 🎜답장 : CPU执行store指令并在cache命中时,我们只更新cache中的数据。并且每个cache line中会有一个bit位记录数据是否被修改过,称之为dirty bit。我们会将dirty bit置位。主存中的数据只会在cache line被替换或者显示的clean 작동 시 업데이트됩니다. 따라서 주 메모리의 데이터는 수정되지 않은 데이터일 수 있지만 수정된 데이터는 캐시 에 있습니다. 캐시와 메인 메모리의 데이터가 일치하지 않을 수 있습니다. ㅋㅋㅋ

위 내용은 입사하고 나서 Cache가 뭔지 이해하게 됐어요의 상세 내용입니다. 자세한 내용은 PHP 중국어 웹사이트의 기타 관련 기사를 참조하세요!