Berapakah kelajuan maksimum pcie3.0x4

Kelajuan baca atau tulis maksimum teori bagi PCIe3.0x4 ialah 4GB/s Tanpa mengira overhed protokol, IO 4GB/4K 4K boleh dihantar sesaat, yang bermaksud IOPS maksimum teori 1000K. Oleh itu, tidak kira apa media yang digunakan dalam lapisan asas SSD, sama ada flash atau 3D xpoint, kelajuan antara muka hanya begitu rendah, dan IOPS maksimum tidak boleh melebihi nilai ini.

Persekitaran pengendalian tutorial ini: sistem Windows 7, komputer Dell G3.

Pengenalan antara muka PCIe

PCIe telah berkembang sehingga kini, dan kelajuannya lebih pantas daripada generasi sebelumnya.

Dalam baris Lebar Pautan, kita lihat X1, X2, X4..., apakah maksudnya? Ini merujuk kepada bilangan lorong (Lane) sambungan PCIe. Sama seperti lebuh raya, terdapat satu lorong, 2 lorong dan 4 lorong Walau bagaimanapun, lebuh raya dengan 8 lorong atau lebih adalah tidak biasa, tetapi PCIe boleh mempunyai sehingga 32 lorong.

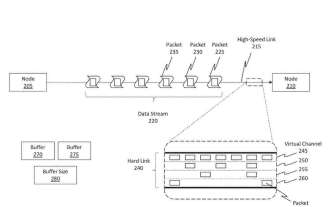

Sambungan PCIe antara dua peranti dipanggil Pautan, seperti yang ditunjukkan dalam rajah di bawah:

Daripada A Ke B, terdapat sambungan dua hala Kereta itu boleh memandu dari A ke B, dan pada masa yang sama, kereta juga boleh memandu dari B ke A, masing-masing pergi ke arahnya sendiri. Terdapat saluran penghantaran dan penerimaan khusus antara dua peranti PCIe, dan data boleh dihantar dalam kedua-dua arah pada masa yang sama memanggil mod kerja mod dwi-simplex, yang boleh difahami sebagai mod dupleks penuh.

Apakah mod kerja SATA?

Seperti PCIe, SATA juga mempunyai saluran penghantaran dan penerimaan bebas, tetapi ia berbeza daripada mod kerja PCIe: hanya satu saluran boleh menghantar data pada masa yang sama Dalam erti kata lain, jika anda menghantar data pada satu saluran, anda tidak boleh menerima data pada saluran lain, dan sebaliknya. Mod kerja ini mestilah mod separuh dupleks. PCIe adalah seperti telefon bimbit kita, kedua-dua pihak boleh bercakap pada masa yang sama, manakala SATA seperti walkie-talkie Apabila seseorang bercakap, orang lain hanya boleh mendengar tetapi tidak bercakap.

Kembali ke jadual jalur lebar PCIe sebelumnya. Jalur lebar di atas, seperti PCIe3.0x1, mempunyai lebar jalur 2GB/s, yang merujuk kepada jalur lebar dua hala, iaitu baca dan tulis. lebar jalur. Jika ia hanya merujuk kepada membaca atau menulis, nilainya hendaklah dikurangkan separuh, iaitu kelajuan membaca atau kelajuan menulis 1GB/s.

Mari kita lihat cara lebar jalur dalam jadual dikira.

PCIe ialah bas bersiri. Kadar penghantaran bit dalam talian bagi PCIe1.0 ialah 2.5Gb/s Lapisan fizikal menggunakan pengekodan 8/10, iaitu data fizikal sebenar talian ialah 10 bit perlu dihantar, jadi:

PCIe1.0 x 1的带宽=(2.5Gb/s x 2(双向通道))/ 10bit = 0.5GB/s

Ini ialah lebar jalur bagi satu Lorong Jika terdapat beberapa Lorong, maka keseluruhan lebar jalur ialah 0.5GB/s didarab dengan bilangan Lorong .

Kadar penghantaran bit dalam talian PCIe2.0 telah meningkat dua kali ganda berdasarkan PCIe1.0 kepada 5Gb/s Lapisan fizikal juga menggunakan pengekodan 8/10, jadi:

PCIe2.0 x 1的带宽=(5Gb/s x 2(双向通道))/ 10bit = 1GB/s

Begitu juga, lebar jalur ialah 1GB/s didarab dengan bilangan Lorong.

Kadar penghantaran bit dalam talian PCIe3.0 tidak meningkat dua kali ganda berdasarkan PCIe2.0 Ia bukan 10Gb/s, tetapi 8Gb/s, tetapi lapisan fizikal menggunakan pengekodan 128/130 untuk penghantaran data. jadi:

PCIe3.0 x 1的带宽=(8Gb/s x 2(双向通道))/ 8bit = 2GB/s

Begitu juga, lebar jalur ialah 2GB/s didarab dengan bilangan Lorong.

Disebabkan penggunaan pengekodan 128/130, data 128-bit hanya menambah 2 bit overhed tambahan, dan nisbah penghantaran data berkesan meningkat Walaupun kadar penghantaran bit dalam talian tidak meningkat dua kali ganda, data yang berkesan lebar jalur masih Ia digandakan berdasarkan PCIe2.0.

Perlu dinyatakan di sini bahawa lebar jalur data yang dikira di atas telah mengambil kira pengekodan 8/10 atau 128/130 Oleh itu, apabila mengira lebar jalur, tidak perlu mempertimbangkan pengekodan dalam talian.

Berbeza dengan saluran tunggal SATA, sambungan PCIe boleh mengembangkan lebar jalur dengan menambah bilangan saluran, yang penuh dengan fleksibiliti. Semakin tinggi bilangan saluran, semakin cepat kelajuannya. Walau bagaimanapun, semakin tinggi bilangan saluran, semakin tinggi kos, mengambil lebih banyak ruang dan menggunakan lebih banyak kuasa. Oleh itu, berapa banyak saluran untuk digunakan harus menjadi pertimbangan menyeluruh antara prestasi dan faktor lain. Memandangkan prestasi sahaja, lebar jalur maksimum PCIe boleh mencapai 64GB/s, dan lebar jalur yang sepadan dengan PCIe 3.0 x 32 adalah angka yang menakutkan. Walau bagaimanapun, SSD antara muka PCIe sedia ada biasanya menggunakan sehingga 4 saluran, seperti PCIe3.0x4, dengan lebar jalur dua arah 8GB/s dan lebar jalur baca atau tulis 4GB/s.

Kelajuan pemindahan beberapa GB/s, yang bagus untuk membaca dan menulis filem kecil.

Di sini, mari kita hitung maksimum teori IOPS 4K PCIe3.0x4. Kelajuan baca atau tulis maksimum secara teori bagi PCIe3.0x4 ialah 4GB/s Tanpa mengira overhed protokol, ia boleh menghantar 4GB/4K 4K IO sesaat, yang bermaksud IOPS maksimum teori ialah 1000K. Oleh itu, untuk SSD, tidak kira apa media yang anda gunakan di bahagian bawah, sama ada flash atau 3D xpoint, kelajuan antara muka hanya begitu rendah, dan IOPS maksimum tidak boleh melebihi nilai ini.

PCIe dibangunkan daripada PCIe "e" bagi PCIe ialah singkatan daripada express, yang bermaksud cepat. Bagaimanakah PCIe boleh menjadi lebih pantas daripada PCI (atau PCI-X)? PCIe pada asasnya berbeza daripada PCI dari segi penghantaran fizikal: PCI menggunakan port selari untuk menghantar data, manakala PCIe menggunakan penghantaran port bersiri. Bas selari PCI saya boleh menghantar 32 bit atau 64 bit dalam satu kitaran jam Mengapa ia tidak boleh dibandingkan dengan bas bersiri anda yang menghantar 1 bit data dalam satu kitaran jam?

Apabila frekuensi jam sebenar agak rendah, port selari memang lebih pantas daripada port bersiri kerana ia boleh menghantar beberapa bit pada masa yang sama. Dengan perkembangan teknologi, kadar penghantaran data diperlukan untuk menjadi lebih cepat dan lebih cepat, dan frekuensi jam juga diperlukan untuk menjadi lebih cepat dan lebih cepat, bagaimanapun, frekuensi jam bas selari tidak boleh secepat yang anda mahu.

Pada penghujung penghantaran, data dihantar keluar pada tepi jam tertentu (tepi naik pertama jam di sebelah kiri), dan pada hujung penerimaan, data dihantar pada tepi jam seterusnya (tepi naik pertama jam di sebelah kanan) terima. Oleh itu, untuk mengumpul data dengan betul di hujung penerima, kitaran jam mestilah lebih besar daripada masa penghantaran data (masa penerbangan dari hujung penghantaran ke hujung penerima). Terhad oleh masa penghantaran data (yang juga meningkat apabila panjang talian data bertambah), kekerapan jam tidak boleh dibuat terlalu tinggi. Di samping itu, apabila isyarat jam dihantar dalam talian, terdapat juga fasa mengimbangi (clock skew), yang menjejaskan pengumpulan data di hujung penerima juga, dalam penghantaran selari, hujung penerima mesti menunggu sedikit data yang paling perlahan untuk tiba sebelum ia boleh mengunci keseluruhan Data (signal skew).

PCIe tidak menghadapi masalah ini apabila menggunakan bas bersiri untuk penghantaran data. Ia tidak mempunyai isyarat jam luaran. Maklumat jamnya dibenamkan dalam aliran data melalui pengekodan 8/10 atau pengekodan 128/130. Oleh itu, ia tidak terhad oleh penghantaran data masa dalam talian Anda Tidak kira berapa lama wayar itu, atau berapa cepat kekerapan penghantaran data anda tanpa isyarat jam luaran, secara semula jadi tiada apa yang dipanggil masalah kecondongan jam kerana ia adalah penghantaran bersiri; satu bit dihantar, jadi tiada masalah pencongan isyarat. Walau bagaimanapun, jika berbilang lorong digunakan untuk menghantar data (ada keselarian dalam siri, haha), masalahnya kembali, kerana hujung penerima juga perlu menunggu data di lorong paling perlahan tiba sebelum ia boleh memproses keseluruhan data.

Pengetahuan asas bas PCIe

Berbeza daripada bas PCI, bas PCIe menggunakan kaedah sambungan hujung ke hujung hujung hanya boleh menyambung ke satu peranti Kedua-dua peranti adalah hujung penghantaran data dan hujung penerimaan data. Selain pautan bas, bas PCIe juga mempunyai berbilang lapisan Pengirim akan melalui lapisan ini semasa menghantar data, dan penerima juga akan menggunakan lapisan ini apabila menerima data. Struktur hierarki yang digunakan oleh bas PCIe adalah serupa dengan susunan protokol rangkaian.

Pautan PCIe menggunakan "kaedah penghantaran data hujung ke hujung". .

Seperti yang ditunjukkan dalam rajah di atas, dalam laluan data (Lane) pautan fizikal bas PCIe, terdapat dua set isyarat pembezaan, sejumlah 4 garis isyarat. Komponen TX di hujung pemancar dan komponen RX di hujung penerima disambungkan menggunakan satu set isyarat pembezaan Pautan ini juga dipanggil pautan pemancar di hujung pemancar dan juga merupakan pautan penerima di hujung penerima; komponen di hujung pemancar dan komponen TX di hujung penerima menggunakan satu lagi set isyarat pembezaan Sekumpulan sambungan isyarat pembezaan, pautan ini juga dipanggil pautan terima di hujung penghantar dan juga merupakan pautan hantar di hujung penerima. Pautan PCIe boleh terdiri daripada berbilang Lorong.

Spesifikasi elektrik untuk isyarat pembezaan berkelajuan tinggi memerlukan kapasitor disambung secara bersiri dengan hujung pemancar untuk gandingan AC. Kapasitor ini juga dipanggil kapasitor gandingan AC. Pautan PCIe menggunakan isyarat pembezaan untuk penghantaran data Isyarat pembezaan terdiri daripada dua isyarat, D+ dan D- hujung penerima isyarat membandingkan perbezaan antara dua isyarat untuk menentukan sama ada hujung penghantaran menghantar logik "1" atau logik ". 0" ".

Berbanding dengan isyarat satu hujung, isyarat pembezaan lebih tahan terhadap gangguan, kerana isyarat pembezaan memerlukan "sama panjang", "sama lebar", "berhampiran" semasa pendawaian dan berada pada lapisan yang sama. Oleh itu, bunyi gangguan luaran akan dimuatkan pada dua isyarat D+ dan D- dengan nilai yang sama dan "secara serentak". Oleh itu, isyarat pembezaan boleh menggunakan frekuensi bas yang lebih tinggi.

Selain itu, penggunaan isyarat pembezaan secara berkesan dapat menekan gangguan elektromagnet EMI (Electro Magnetic Interference). Kerana isyarat pembezaan D+ dan D- adalah sangat rapat dan mempunyai amplitud isyarat yang sama dan kekutuban bertentangan. Amplitud medan elektromagnet yang digabungkan antara kedua-dua wayar ini dan wayar tanah adalah sama dan akan membatalkan satu sama lain, jadi isyarat pembezaan menyebabkan kurang gangguan elektromagnet kepada dunia luar. Sudah tentu, kelemahan isyarat pembezaan juga jelas. Pertama, isyarat pembezaan menggunakan dua isyarat untuk menghantar satu bit data, kedua, pendawaian isyarat pembezaan adalah agak ketat.

Pautan PCIe boleh terdiri daripada berbilang Lorong Pada masa ini, pautan PCIe boleh menyokong 1, 2, 4, 8, 12, 16 dan 32 Lorong, iaitu ×1, ×2, ×4, ×8 , ×. Pautan PCIe lebar 12, ×16 dan ×32. Kekerapan bas yang digunakan pada setiap Lorong adalah berkaitan dengan versi bas PCIe yang digunakan.

Spesifikasi bas PCIe pertama ialah V1.0, diikuti oleh V1.0a, V1.1, V2.0 dan V2.1. Spesifikasi terkini bas PCIe kini ialah V2.1, manakala V3.0 sedang dalam pembangunan dan dijangka dikeluarkan pada tahun 2010. Spesifikasi bas PCIe yang berbeza mentakrifkan frekuensi bas yang berbeza dan kaedah pengekodan pautan, seperti yang ditunjukkan dalam Jadual 41.

Hubungan antara spesifikasi bas PCIe dan kekerapan bas dan pengekodan

| PCIe总线规范 | 总线频率[1] | 单Lane的峰值带宽 | 编码方式 |

|---|---|---|---|

| 1.x | 1.25GHz | 2.5GT/s | 8/10b编码 |

| 2.x | 2.5GHz | 5GT/s | 8/10b编码 |

| 3.0 | 4GHz | 8GT/s | 128/130b编码 |

Seperti yang ditunjukkan dalam jadual di atas, spesifikasi bas PCIe yang berbeza menggunakan frekuensi bas yang berbeza pengekodan yang digunakan juga berbeza. Spesifikasi bas PCIe V1.x dan V2.0 menggunakan pengekodan 8/10b dalam lapisan fizikal, iaitu, 10 bit pada pautan PCIe mengandungi 8 bit data yang sah manakala spesifikasi V3.0 menggunakan pengekodan 128/130b, iaitu 130 bit pada pautan PCIe mengandungi 128 bit data yang sah.

Seperti yang ditunjukkan dalam jadual di atas, walaupun kekerapan bas yang digunakan oleh spesifikasi V3.0 hanya 4GHz, lebar jalur berkesannya adalah dua kali ganda berbanding V2.x. Berikut akan mengambil spesifikasi V2.x sebagai contoh untuk menggambarkan lebar jalur puncak yang boleh disediakan oleh pautan PCIe dengan lebar yang berbeza, seperti yang ditunjukkan dalam Jadual 42.

Jalur lebar puncak bas PCIe

| PCIe总线的数据位宽 | ×1 | ×2 | ×4 | ×8 | ×12 | ×16 | ×32 |

|---|---|---|---|---|---|---|---|

| 峰值带宽(GT/s) | 5 | 10 | 20 | 40 | 60 | 80 | 160 |

Seperti yang ditunjukkan dalam jadual di atas, pautan ×32 PCIe boleh memberikan lebar jalur pautan 160GT/s, iaitu jauh lebih tinggi Lebar jalur puncak yang disediakan oleh bas PCI/PCI-X. Spesifikasi PCIe V3.0 yang akan datang menggunakan frekuensi bas 4GHz, yang akan meningkatkan lagi lebar jalur puncak pautan PCIe.

Dalam bas PCIe, gunakan GT (Gigatransfer) untuk mengira lebar jalur puncak pautan PCIe. GT ialah lebar jalur puncak yang dihantar pada pautan PCIe, dan formula pengiraannya ialah kekerapan bas × lebar bit data × 2.

Dalam bas PCIe, terdapat banyak faktor yang mempengaruhi lebar jalur berkesan, jadi jalur lebar berkesannya sukar dikira. Walaupun begitu, jalur lebar berkesan yang disediakan oleh bas PCIe masih jauh lebih tinggi daripada bas PCI. Bas PCIe juga mempunyai kelemahannya, yang paling menonjol ialah kependaman penghantaran.

Pautan PCIe menggunakan mod bersiri untuk penghantaran data Walau bagaimanapun, di dalam cip, bas data masih selari, jadi antara muka pautan PCIe perlu melakukan penukaran bersiri-ke-selari ini akan menghasilkan Kelewatan yang lebih besar. Selain itu, paket data pada bas PCIe perlu melalui lapisan transaksi, lapisan pautan data dan lapisan fizikal Paket data ini juga akan menyebabkan kelewatan apabila melalui lapisan ini.

Antara peranti berasaskan bas PCIe, pautan ×1 PCIe adalah yang paling biasa, manakala pautan ×12 PCIe jarang berlaku dan peranti PCIe ×4 dan ×8 juga jarang berlaku. Intel biasanya menyepadukan berbilang pautan PCIe ×1 dalam ICH untuk menyambungkan persisian berkelajuan rendah, dan menyepadukan pautan ×16 PCIe dalam MCH untuk menyambungkan pengawal kad grafik. Pemproses PowerPC biasanya boleh menyokong pautan ×8, ×4, ×2, dan ×1 PCIe.

Penghantaran data antara pautan fizikal bas PCIe menggunakan mekanisme penghantaran segerak berasaskan jam, tetapi tiada garis jam pada pautan fizikal Hujung penerima bas PCIe mengandungi modul pemulihan jam CDR (Clock Pemulihan Data). CDR akan mengekstrak jam terima daripada mesej yang diterima untuk melakukan pemindahan data segerak.

Perlu diperhatikan bahawa dalam peranti PCIe, selain mengekstrak jam dari paket, pasangan isyarat REFCLK+ dan REFCLK- juga digunakan sebagai jam rujukan tempatan

Lebih banyak pengetahuan berkaitan , Sila lawati bahagian Soalan Lazim!

Atas ialah kandungan terperinci Berapakah kelajuan maksimum pcie3.0x4. Untuk maklumat lanjut, sila ikut artikel berkaitan lain di laman web China PHP!

Alat AI Hot

Undresser.AI Undress

Apl berkuasa AI untuk mencipta foto bogel yang realistik

AI Clothes Remover

Alat AI dalam talian untuk mengeluarkan pakaian daripada foto.

Undress AI Tool

Gambar buka pakaian secara percuma

Clothoff.io

Penyingkiran pakaian AI

AI Hentai Generator

Menjana ai hentai secara percuma.

Artikel Panas

Alat panas

Notepad++7.3.1

Editor kod yang mudah digunakan dan percuma

SublimeText3 versi Cina

Versi Cina, sangat mudah digunakan

Hantar Studio 13.0.1

Persekitaran pembangunan bersepadu PHP yang berkuasa

Dreamweaver CS6

Alat pembangunan web visual

SublimeText3 versi Mac

Perisian penyuntingan kod peringkat Tuhan (SublimeText3)

Topik panas

1381

1381

52

52

Sila matikan kuasa dan sambungkan kabel kuasa PCIe

Feb 19, 2024 am 11:09 AM

Sila matikan kuasa dan sambungkan kabel kuasa PCIe

Feb 19, 2024 am 11:09 AM

Jika anda melihat mesej ralat Sila matikan dan sambungkan kabel kuasa PCIe pada PC Windows 11/10 anda, sila baca siaran ini untuk mengetahui cara menyelesaikan isu tersebut. Ralat ini boleh dicetuskan apabila peranti PCIe (biasanya kad grafik) gagal menerima kuasa yang mencukupi. Punca yang mungkin termasuk kabel kuasa PCIe yang rosak, masalah sambungan atau kuasa yang tidak mencukupi. Masalah ini juga boleh berlaku jika kord kuasa tidak disambungkan dengan betul. Sila matikan kuasa dan sambungkan kabel kuasa PCIE (S) kad grafik ini. Pengguna PC kali pertama atau orang yang kurang pengalaman dalam memasang sistem komputer sering menghadapi masalah ini. Mesej ralat ini juga mungkin berlaku jika kabel PCIe menjadi longgar disebabkan oleh getaran atau masa. Artikel ini menerangkan langkah yang perlu anda ambil untuk menyelesaikan isu ini

Adakah antara muka pcie4.0 dan pcie3.0 sama?

Mar 13, 2023 pm 04:39 PM

Adakah antara muka pcie4.0 dan pcie3.0 sama?

Mar 13, 2023 pm 04:39 PM

Antara muka pcie4.0 dan pcie3.0 adalah dua versi berbeza bagi standard PCIe. Perbezaan antara keduanya: 1. PCIe 4.0 menyediakan kelajuan penghantaran data yang lebih pantas, sehingga 16GT/s, iaitu dua kali ganda daripada PCIe 3.0 2. PCIe 4.0 menyokong lebih lebar jalur, sehingga 69.6GB/s sahaja menyokong sehingga 32GB/s; 3. PCIe4.0 menyokong lebih banyak saluran dan boleh menyokong lebih banyak peranti 4. PCIe4.0 menyokong penggunaan kuasa yang lebih rendah.

Ditangguh selama 1 tahun, penggunaan spesifikasi PCIe 6.0/7.0 menghadapi halangan

Jun 15, 2024 pm 04:45 PM

Ditangguh selama 1 tahun, penggunaan spesifikasi PCIe 6.0/7.0 menghadapi halangan

Jun 15, 2024 pm 04:45 PM

Menurut berita dari laman web ini pada 15 Jun, Kumpulan Kepentingan Khas Interconnect Komponen Periferal (PCI-SIG) mengadakan Persidangan Pembangun 2024 minggu ini dan mengumumkan kemajuan terkini PCIe6.0 dan PCIe7.0, menunjukkan bahawa walaupun kedua-dua standard di atas Beberapa kemajuan telah dicapai, tetapi penggunaan penggunaan lebih perlahan daripada yang dijangkakan. PCI-SIG pada masa ini telah menangguhkan pelancaran "Program Pematuhan" (Program Pematuhan) Ujian ketekalan awal PCIe6.0 pada asalnya dijadualkan bermula pada bulan Mac tahun ini, tetapi telah ditangguhkan kepada "suku kedua", yang bermaksud. ia akan diuji sebelum akhir bulan ini. Pelan halatuju keluaran standard PCIe untuk 2023 (atas) dan 2024 (bawah) Agensi menyatakan bahawa ujian pematuhan mendalam PCIe6.0 akan dijalankan pada 2020

Berapakah kelajuan maksimum pcie3.0x4

Mar 15, 2023 pm 05:09 PM

Berapakah kelajuan maksimum pcie3.0x4

Mar 15, 2023 pm 05:09 PM

Kelajuan baca atau tulis maksimum secara teori bagi PCIe3.0x4 ialah 4GB/s Tanpa mengira overhed protokol, ia boleh menghantar 4GB/4K 4K IO sesaat, yang bermaksud IOPS maksimum teori ialah 1000K. Oleh itu, tidak kira apa media yang digunakan dalam lapisan asas SSD, sama ada flash atau 3D xpoint, kelajuan antara muka hanya terhad, dan IOPS maksimum tidak boleh melebihi nilai ini.

Draf pertama rasmi spesifikasi PCIe 7.0 (versi 0.5) telah diumumkan dan masih dijangka dikeluarkan sepenuhnya tahun depan

Apr 04, 2024 am 08:37 AM

Draf pertama rasmi spesifikasi PCIe 7.0 (versi 0.5) telah diumumkan dan masih dijangka dikeluarkan sepenuhnya tahun depan

Apr 04, 2024 am 08:37 AM

Menurut berita dari laman web ini pada 3 April, PCI-SIG, organisasi pembangunan spesifikasi PCIe, baru-baru ini mengumumkan versi 0.5 spesifikasi PCIe7.0, iaitu, draf pertama rasminya telah dikeluarkan kepada ahli PCI-SIG. Berbanding dengan spesifikasi PCIe6.0 yang dikeluarkan pada awal 2022, spesifikasi PCIe7.0 menggandakan kadar sekali lagi sambil terus menggunakan kaedah modulasi isyarat PAM4, mencapai kadar data asal 128GT/s dan mencapai 512GB/s dua hala dalam konfigurasi x16 . Pembangunan seni bina PCIe7.0 menumpukan pada meningkatkan parameter saluran, liputan dan kecekapan tenaga, bertujuan untuk menyediakan aplikasi intensif data seperti 800G Ethernet, beban kerja AI/ML, pusat data berskala ultra-besar, pengkomputeran berprestasi tinggi, kuantum pengkomputeran, dan awan

Gamescom 2024 | Asus dan MSI mendedahkan mekanisme keluaran pantas yang inovatif untuk GPU dan M.2 SSD

Aug 25, 2024 am 06:30 AM

Gamescom 2024 | Asus dan MSI mendedahkan mekanisme keluaran pantas yang inovatif untuk GPU dan M.2 SSD

Aug 25, 2024 am 06:30 AM

Di Gamescom 2024, Asus dan MSI benar-benar menjadi tumpuan dengan beberapa mekanisme keluaran pantas yang hebat untuk GPU dan M.2 SSD. Ciri baharu ini bertujuan untuk menjadikan kehidupan lebih mudah bagi orang yang membina PC, terutamanya apabila berurusan dengan komponen yang besar itu. Asus rolle

Apa yang perlu dilakukan jika PCIe 6 menjadi panas? Intel menyerahkan pemacu baharu, memudahkan dengan mengawal kelajuan bas

Jun 04, 2024 am 10:28 AM

Apa yang perlu dilakukan jika PCIe 6 menjadi panas? Intel menyerahkan pemacu baharu, memudahkan dengan mengawal kelajuan bas

Jun 04, 2024 am 10:28 AM

Menurut berita dari laman web ini pada 11 Mei, perubahan versi PCIe telah membawa lebar jalur yang lebih tinggi, kelajuan penghantaran yang lebih pantas, dan juga membawa lebih banyak haba. Intel baru-baru ini mengeluarkan pemacu Linux yang menggunakan sumber terbuka "Pengawal Lebar Jalur PCIe" untuk mengekang haba dan mengawal kelajuan pautan secara automatik apabila haba mencapai ambang tertentu. Nota dari laman web ini: Perubahan versi PCIe bukan sahaja meningkatkan kelajuan penghantaran, tetapi juga memerlukan integriti isyarat yang lebih baik dan kehilangan isyarat yang lebih rendah, jadi mereka sering memerlukan frekuensi jam yang lebih tinggi, kuasa yang lebih besar dan pengoptimuman pengekodan, yang kesemuanya akan menghasilkan kalori tambahan. Jurutera Intel Ilpo Järvinen menulis dalam nota tampalan terkini: "Siri tampung ini hanya menambah sokongan untuk mengawal kelajuan pautan PCIe. Mengawal PCIe

Meningkatkan penghantaran pautan data PCIe dalaman HoloLens: Microsoft berkongsi paten AR/VR

Jan 03, 2024 pm 02:05 PM

Meningkatkan penghantaran pautan data PCIe dalaman HoloLens: Microsoft berkongsi paten AR/VR

Jan 03, 2024 pm 02:05 PM

(Nweon 27 Disember 2023) Sambungan berwayar sering dipanggil "pautan keras", yang menyambungkan satu nod ke nod lain secara fizikal. Satu sambungan berwayar ialah PCIe. PCIe ialah antara muka yang digunakan untuk menyambungkan nod berkelajuan tinggi, dan sementara terminal dan protokol sambungan berkelajuan tinggi seperti PCIe menawarkan kelebihan yang besar, jenis terminal ini memerlukan kuasa tinggi untuk beroperasi. Untuk seni bina pengkomputeran berkuasa bateri seperti set kepala, ini akan memberi beban yang besar kepada sistem. Dalam aplikasi paten bertajuk "Errorrecoveryandpowermanagementbetweennodesofaninterconnectionnetwork", Microsoft menerangkan cara memulihkan data daripada bar ralat