Peranti teknologi

Peranti teknologi

AI

AI

Inilah talian hayat transistor: CMOS bertindan 3D, adakah Undang-undang Moore akan diteruskan selama 10 tahun lagi?

Inilah talian hayat transistor: CMOS bertindan 3D, adakah Undang-undang Moore akan diteruskan selama 10 tahun lagi?

Inilah talian hayat transistor: CMOS bertindan 3D, adakah Undang-undang Moore akan diteruskan selama 10 tahun lagi?

Transistor dikenali sebagai "ciptaan terhebat abad ke-20."

Kemunculannya meletakkan asas untuk penghasilan litar bersepadu, mikropemproses dan ingatan komputer.

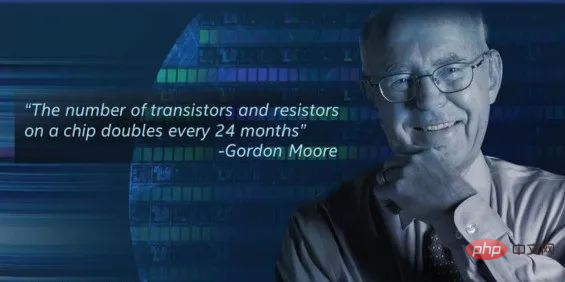

Pada tahun 1965, "Moore's Law" telah dicadangkan dan menjadi peraturan emas industri semikonduktor selama beberapa dekad.

Ia menunjukkan bahawa setiap 18~24 bulan, bilangan transistor yang dibungkus pada mikrocip akan berganda, dan prestasi cip akan meningkat dua kali ganda.

Walau bagaimanapun, dengan pengenalan berterusan nod proses baharu, bilangan atom dalam transistor semakin berkurangan. , dan pelbagai had melampau Fizikal menyekat perkembangan selanjutnya Undang-undang Moore.

Sesetengah orang berpendapat bahawa Undang-undang Moore sudah berakhir.

Oleh itu, untuk "menyelamatkan" Undang-undang Moore, jurutera perlu menukar struktur transistor, terus mengurangkan kawasan dan penggunaan kuasa, dan meningkatkan prestasinya.

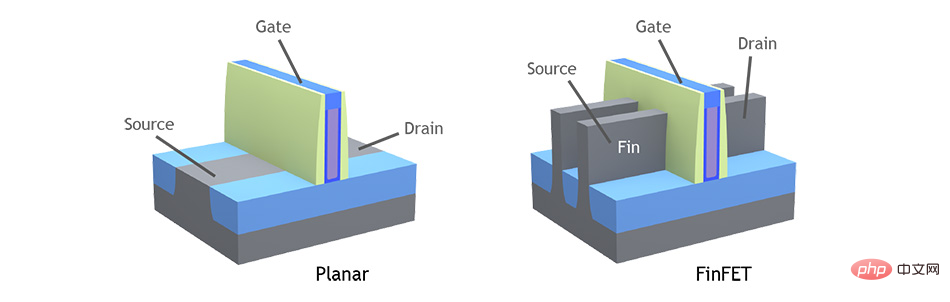

Pada separuh kedua abad ke-20, reka bentuk transistor planar (Transistor Planar) amat popular. Memasuki tahun 2010-an, peranti berbentuk sirip 3D secara beransur-ansur menggantikan reka bentuk rata.

Kini, struktur reka bentuk transistor yang benar-benar baharu, transistor get-all-around (GAA), ialah pengganti kepada FinFET dan akan memasuki pengeluaran.

Walau bagaimanapun, kita mesti melihat lebih jauh. Kerana walaupun dengan seni bina transistor baharu ini RibbonFET yang dicadangkan oleh Intel, keupayaan kami untuk mengurangkan saiz mempunyai had.

Percaya bahawa semikonduktor oksida logam pelengkap (CMOS) atau CFET (transistor kesan medan pelengkap) bertindan 3D akan menjadi sepuluh tahun akan datang untuk melanjutkan Hukum Moore Kunci kepada tahun.

Evolusi Transistor

Setiap Transistor Kesan Medan Semikonduktor Oksida Logam (MOSFET) mempunyai set komponen asas yang sama:

Timbunan pintu, kawasan saluran, sumber, longkang

Punca dan longkang didop secara kimia supaya bahawa mereka sama ada kaya dengan elektron mudah alih (jenis-n) atau kekurangannya (jenis-p). Rantau saluran mempunyai doping yang bertentangan dengan sumber dan longkang.

Dalam versi planar transistor dalam mikropemproses lanjutan sebelum 2011, susunan gerbang MOSFET berada tepat di atas kawasan saluran Unjurkan medan elektrik ke dalam saluran wilayah.

Menggunakan voltan yang cukup besar ke pintu gerbang (berbanding dengan sumber) akan membentuk lapisan pembawa cas mudah alih di kawasan saluran, supaya Biarkan arus mengalir antara punca dan longkang.

Untuk mengurangkan saiz reka bentuk transistor planar, "kesan saluran pendek" telah menjadi tumpuan ahli fizik .

Oleh kerana teknologi proses terus bertambah baik, lebar elektrod get dalam transistor semakin kecil dan kecil. Anda tahu, apabila pintu pagar lebih rendah daripada 20nm, arus akan menjadi tidak terkawal, dan arus sumber akan menembusi pintu dan terus sampai ke longkang.

Pada masa ini, "kebocoran" akan berlaku, yang akan menyebabkan penggunaan tenaga cip meningkat dengan mendadak.

Untuk menyelesaikan masalah ini, teknologi transistor FinFET baharu telah dicadangkan. Ia membalut pintu pagar di sekeliling saluran pada tiga sisi untuk memberikan kawalan statik yang lebih baik.

FinFET mengurangkan penggunaan kuasa kira-kira 50% pada tahap prestasi yang sama seperti seni bina satah generasi sebelumnya. FinFET juga bertukar lebih pantas, memberikan peningkatan prestasi sebanyak 37%.

Pada tahun 2011, Intel memperkenalkan FinFET pada nod 22nmnya dan menggunakannya dalam pengeluaran pemproses Teras generasi ketiga.

Sejak itu, FinFET telah menjadi kuda kerja Undang-undang Moore.

Walau bagaimanapun, kami juga kehilangan sesuatu apabila kami berpindah ke FinFET.

Dalam peranti planar, lebar transistor ditakrifkan oleh fotolitografi, jadi ia merupakan parameter yang sangat fleksibel.

Tetapi dalam FinFET, lebar transistor datang dalam kenaikan diskret, satu sirip ditambah pada satu masa. Sifat ini sering dipanggil kuantisasi sirip.

Walaupun FinFET mempunyai fleksibiliti, pengkuantitian sirip kekal sebagai kekangan reka bentuk yang penting. Peraturan reka bentuk yang mengelilinginya, dan keinginan untuk menambah lebih banyak sirip untuk meningkatkan prestasi, meningkatkan keseluruhan kawasan sel logik dan merumitkan timbunan antara sambungan yang menjadikan satu transistor menjadi litar logik yang lengkap.

Ia juga meningkatkan kapasiti transistor, dengan itu mengurangkan kelajuan pensuisannya. Oleh itu, sementara FinFET telah berkhidmat kepada kami dengan baik sebagai pekerja industri, pendekatan baharu yang lebih halus diperlukan.

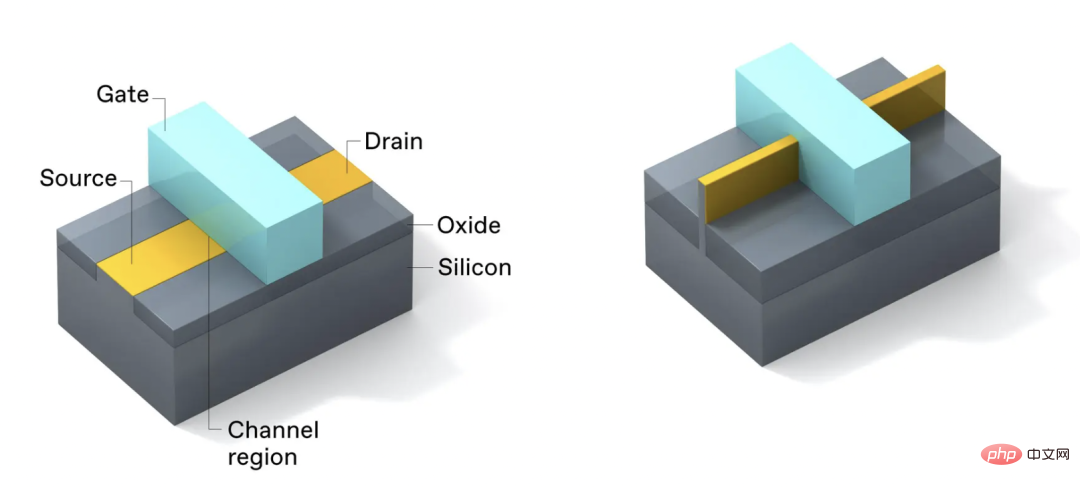

Pendekatan inilah yang menyebabkan ahli fizik mencipta transistor 3D yang akan datang, RibbonFET.

Dalam RibbonFET, pintu pagar mengelilingi kawasan saluran transistor untuk meningkatkan kawalan pembawa cas. Struktur baharu juga membolehkan prestasi yang lebih baik dan pengoptimuman yang lebih halus.

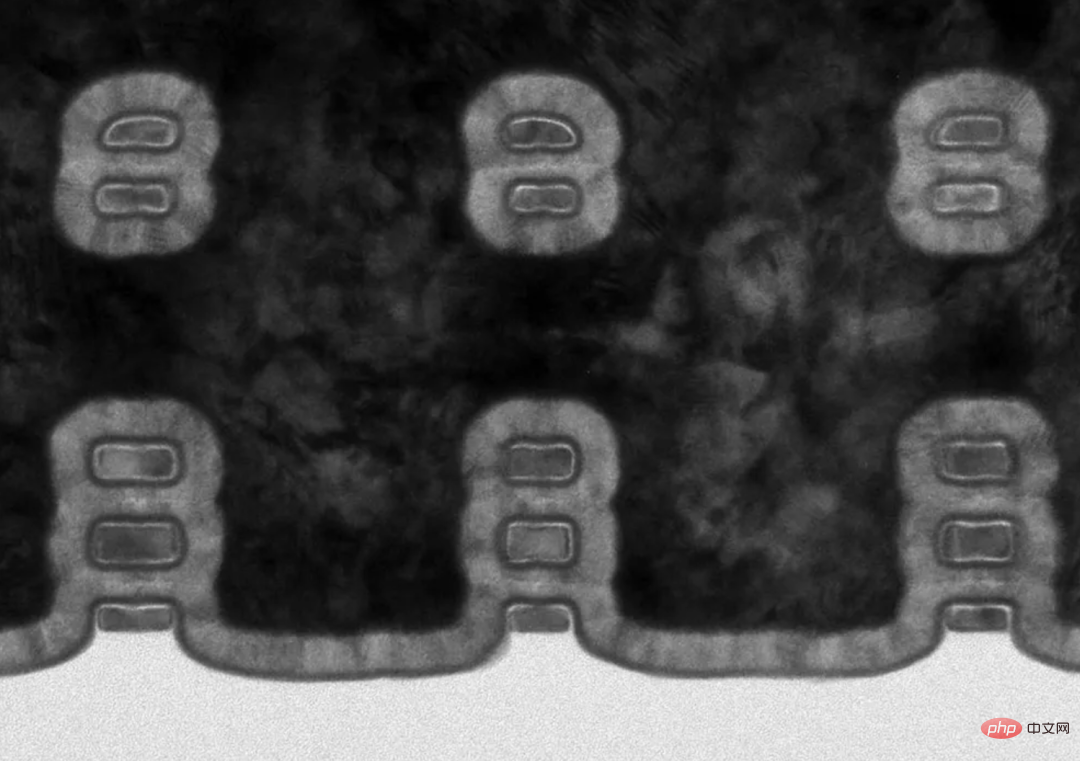

Secara khusus, pintu pagar mengelilingi saluran sepenuhnya, memberikan kawalan yang lebih ketat ke atas pembawa cas dalam saluran, yang kini diperbuat daripada bentuk reben Silikon skala nano.

Menggunakan reben nano (nanosheet) ini, sekali lagi mungkin untuk menggunakan fotolitografi untuk menukar lebar transistor seperti yang dikehendaki.

Setelah kekangan kuantisasi dialih keluar, adalah mungkin untuk menjana lebar bersaiz yang sesuai untuk aplikasi. Ini membolehkan kami mengimbangi kuasa, prestasi dan kos.

Lebih penting lagi, dengan menyusun dan beroperasi secara selari, peranti boleh memacu lebih arus, meningkatkan prestasi tanpa menambah kawasan.

Oleh itu, Intel percaya bahawa RibbonFET adalah pilihan terbaik untuk mencapai prestasi yang lebih tinggi pada kuasa yang munasabah.

Mereka akan memperkenalkan struktur RibbonFET pada proses Intel 20A pada tahun 2024.

CMOS tindanan 3D

Satu perkara yang mempunyai persamaan transistor planar, FinFET dan RibbonFET ialah semuanya Menggunakan teknologi CMOS, seperti yang dinyatakan sebelum ini, CMOS terdiri daripada transistor jenis-n dan jenis-p. Teknologi ini menjadi arus perdana pada tahun 1980-an kerana ia menarik arus yang jauh lebih sedikit daripada alternatif lain. Kurang arus bermakna frekuensi operasi yang lebih tinggi dan ketumpatan transistor yang lebih tinggi.

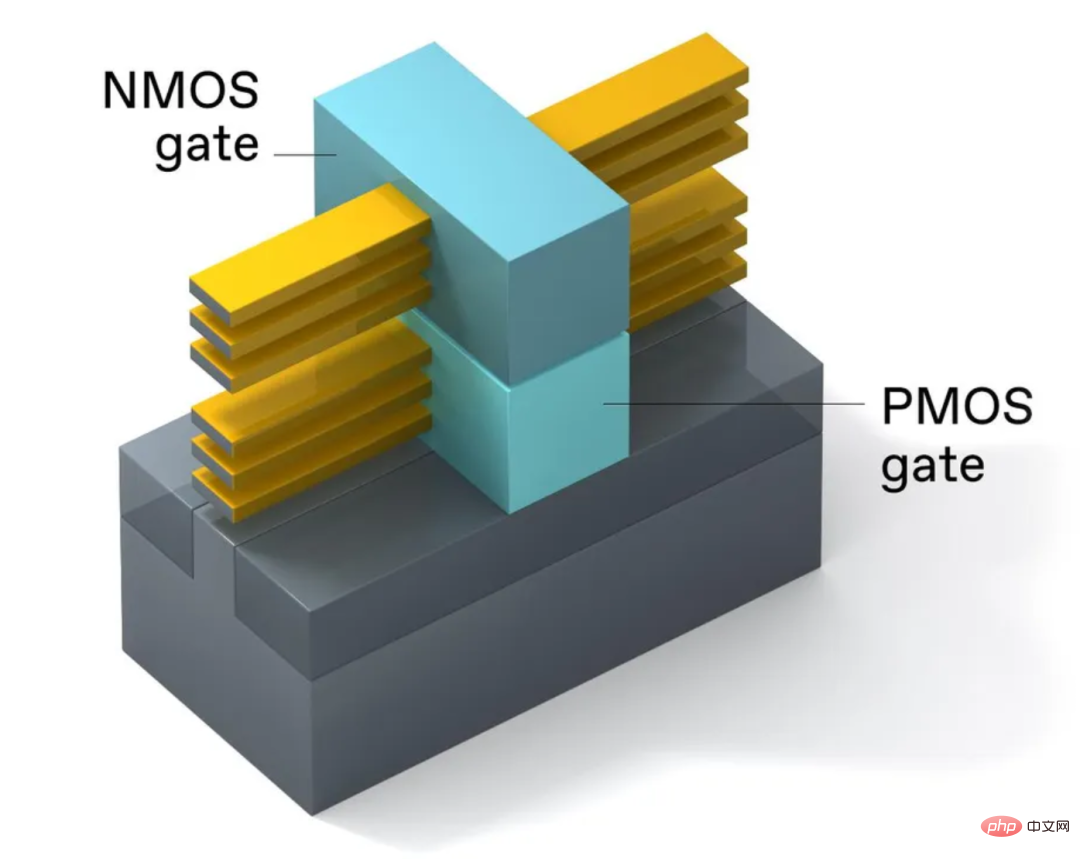

Sehingga kini, semua teknologi CMOS telah meletakkan pasangan standard transistor NMOS dan PMOS bersebelahan. Walau bagaimanapun, dalam ucaptama Persidangan Komponen Elektronik Antarabangsa IEEE (IEDM) 2019, konsep transistor "tindan 3D" telah dicadangkan, meletakkan transistor NMOS di atas transistor PMOS.

Pada IEDM 2020, penyongsang pertama reka bentuk litar logik menggunakan teknologi 3D ini telah dipersembahkan peranti. CMOS bertindan 3D dengan berkesan mengurangkan jejak penyongsang sebanyak separuh, menggandakan ketumpatan kawasan transistor dan seterusnya menolak had Hukum Moore.

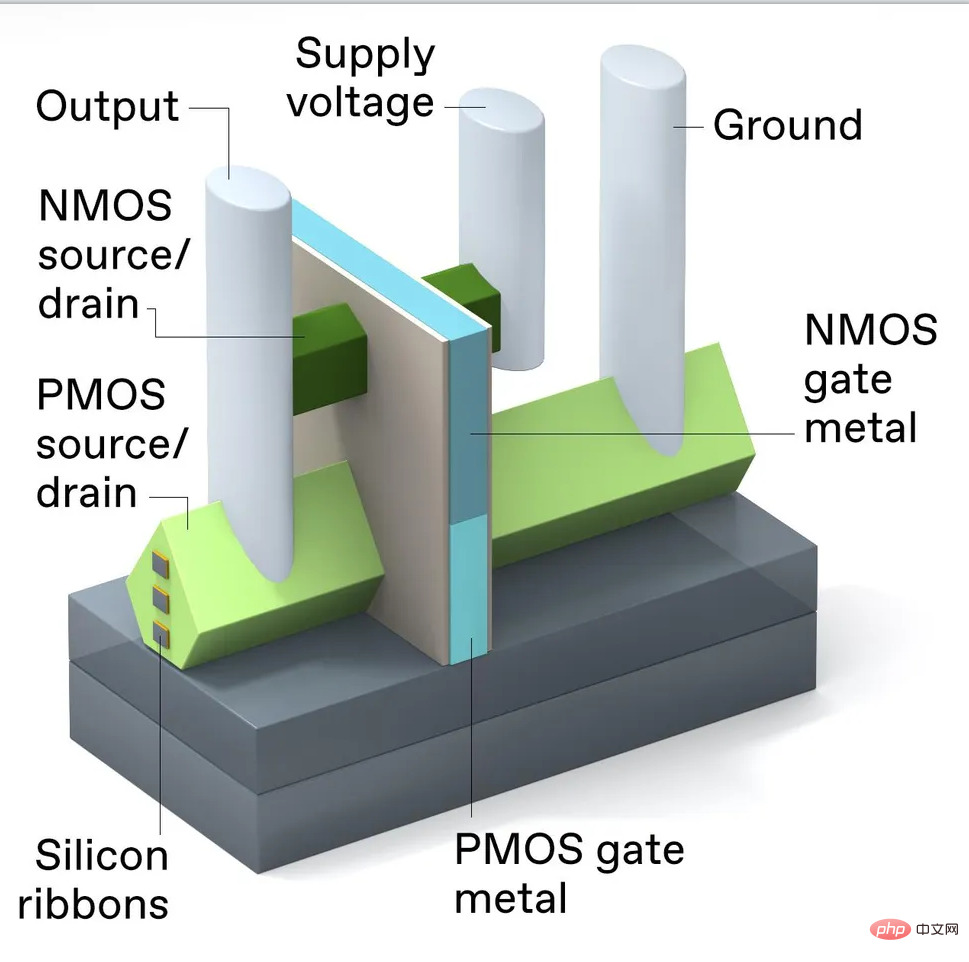

Struktur CMOS bertindan 3D, meletakkan peranti PMOS di atas peranti NMOS, dengan jumlah keluasan yang sama dengan satu kawasan RibbonFET. Pintu NMOS dan PMOS menggunakan bahan logam yang berbeza

Untuk menggunakan CMOS bertindan 3D, banyak cabaran penyepaduan proses perlu diselesaikan, sebahagian daripadanya melibatkan pemprosesan dan pembuatan CMOS. had.

Bagaimana untuk mencapainya? Pembuatan CMOS 3D jajaran sendiri bermula dengan wafer silikon. Pada wafer, kami mendeposit lapisan demi lapisan silikon dan silikon germanium, struktur yang dipanggil "superlattice." Corak fotolitografi kemudiannya digunakan untuk memotong sebahagian daripada superlattice, meninggalkan struktur seperti sirip. Kristal superlattice menyediakan struktur sokongan yang kuat untuk proses pembangunan seterusnya.

Seterusnya, polisilikon "palsu" diletakkan pada kekisi super untuk melindungi bekas daripada operasi seterusnya. Langkah ini, yang dikenali sebagai proses dwi sumber/saliran bertindan secara menegak, menumbuhkan silikon dop fosforus pada kedua-dua hujung reben atas (tapak NMOS masa hadapan) manakala silikon terdop secara selektif pada nanoribbon bawah (tapak PMOS silikon germanium masa hadapan). Selepas itu, dielektrik diletakkan di sekeliling sumber kuasa untuk mengasingkannya antara satu sama lain melalui nyahcas elektrik.

Penyusun 3D dengan berkesan menggandakan ketumpatan transistor CMOS setiap milimeter persegi, ketumpatan sebenar bergantung pada kerumitan sel logik yang terlibat.

Akhirnya datanglah pembinaan pintu. Mula-mula keluarkan pintu palsu yang dipasang sebelum ini untuk mendedahkan reben nano silikon. Seterusnya, hanya germanium silikon yang terukir, melepaskan longgokan nanoribbon silikon selari, yang merupakan kawasan saluran transistor.

Kemudian lapisan penebat yang sangat nipis disalut pada keempat-empat sisi reben nano ini mempunyai pemalar dielektrik yang tinggi. Saluran nanoribbon adalah sangat kecil sehingga ia tidak boleh disalut secara kimia dengan cekap seperti transistor planar.

Gunakan logam untuk mengelilingi reben nano bawah untuk membentuk saluran berdop-p, dan reben nano atas untuk membentuk saluran berdop-n dengan reben nano yang lain. Dengan cara ini, susunan get dibina dan kedua-dua transistor dipasang.

Proses ini mungkin kelihatan rumit, tetapi ia lebih baik daripada teknik lain (susun 3D berurutan). Jika yang terakhir digunakan, peranti NMOS dan peranti PMOS dipasang pada wafer berasingan, dan kemudian kedua-duanya disatukan dan lapisan PMOS dipindahkan ke wafer NMOS. Kaedah tindanan 3D jajaran sendiri mempunyai langkah pemprosesan yang lebih sedikit dan boleh mengawal kos pembuatan dengan lebih ketat.

Dan yang lebih penting, kaedah penjajaran diri ini juga mengelakkan ralat penjajaran yang mungkin berlaku semasa menyambungkan dua wafer. Membuat semua sambungan yang diperlukan ke CMOS bertindan 3D adalah sangat mencabar. Sambungan kuasa akan diperlukan daripada timbunan peranti di bawah. Mengikut reka bentuk, peranti NMOS [atas] dan peranti PMOS [bawah] mempunyai sesentuh sumber/parit yang berasingan, tetapi kedua-dua peranti berkongsi pintu yang sama.

Perlu diperhatikan bahawa jarak menegak antara NMOS dan PMOS perlu dioptimumkan: jika ia terlalu pendek, ia akan meningkatkan kapasiti parasit, jika ia terlalu panjang, ia akan Meningkatkan rintangan sambung antara dua peranti. Sama ada situasi yang melampau akan menyebabkan litar menjadi perlahan dan menggunakan lebih banyak kuasa.

Banyak kajian reka bentuk, seperti yang dibentangkan oleh Pusat Penyelidikan TEL Amerika pada persidangan IEDM 2021, bercadang untuk menyediakan semua sambungan yang diperlukan dalam ruang terhad CMOS 3D, dan berbuat demikian tidak begitu ketara. Tingkatkan kawasan sel logik yang mereka bentuk. Penyelidikan menunjukkan bahawa terdapat banyak peluang untuk inovasi dalam mencari pilihan sambung terbaik.

Masa depan Undang-undang Moore

Dengan transistor kesan medan jalur dan CMOS 3D, kami mempunyai laluan yang jelas untuk meneruskan kehidupan Undang-undang Moore Laluan itu boleh dilanjutkan sekurang-kurangnya sehingga 2024 dan seterusnya.

Dalam temu bual 2005, Gordon Moore, pencadang Undang-undang Moore, mengakui bahawa "Saya terkejut dari semasa ke semasa dengan kemajuan yang telah dibuat. "

Dia berkata, “Ada masa di sepanjang jalan yang saya fikir kami telah sampai ke penghujungnya, tetapi jurutera kreatif kami datang dengan idea untuk mengatasi kesukaran. "

Apabila proses pembuatan transistor melalui FinFET, dan dengan pengoptimuman berterusan muncul era RibbonFET, dan akhirnya bergerak ke arah proses CMOS bertindan 3D, kita Ia adalah menjangkakan bahawa Encik Gordon Moore akan terkejut tidak lama lagi.

Atas ialah kandungan terperinci Inilah talian hayat transistor: CMOS bertindan 3D, adakah Undang-undang Moore akan diteruskan selama 10 tahun lagi?. Untuk maklumat lanjut, sila ikut artikel berkaitan lain di laman web China PHP!

Alat AI Hot

Undresser.AI Undress

Apl berkuasa AI untuk mencipta foto bogel yang realistik

AI Clothes Remover

Alat AI dalam talian untuk mengeluarkan pakaian daripada foto.

Undress AI Tool

Gambar buka pakaian secara percuma

Clothoff.io

Penyingkiran pakaian AI

AI Hentai Generator

Menjana ai hentai secara percuma.

Artikel Panas

Alat panas

Notepad++7.3.1

Editor kod yang mudah digunakan dan percuma

SublimeText3 versi Cina

Versi Cina, sangat mudah digunakan

Hantar Studio 13.0.1

Persekitaran pembangunan bersepadu PHP yang berkuasa

Dreamweaver CS6

Alat pembangunan web visual

SublimeText3 versi Mac

Perisian penyuntingan kod peringkat Tuhan (SublimeText3)

Topik panas

1386

1386

52

52

Mengapakah Gaussian Splatting begitu popular dalam pemanduan autonomi sehingga NeRF mula ditinggalkan?

Jan 17, 2024 pm 02:57 PM

Mengapakah Gaussian Splatting begitu popular dalam pemanduan autonomi sehingga NeRF mula ditinggalkan?

Jan 17, 2024 pm 02:57 PM

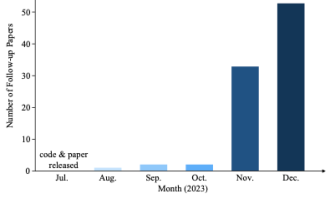

Ditulis di atas & pemahaman peribadi pengarang Gaussiansplatting tiga dimensi (3DGS) ialah teknologi transformatif yang telah muncul dalam bidang medan sinaran eksplisit dan grafik komputer dalam beberapa tahun kebelakangan ini. Kaedah inovatif ini dicirikan oleh penggunaan berjuta-juta Gaussians 3D, yang sangat berbeza daripada kaedah medan sinaran saraf (NeRF), yang terutamanya menggunakan model berasaskan koordinat tersirat untuk memetakan koordinat spatial kepada nilai piksel. Dengan perwakilan adegan yang eksplisit dan algoritma pemaparan yang boleh dibezakan, 3DGS bukan sahaja menjamin keupayaan pemaparan masa nyata, tetapi juga memperkenalkan tahap kawalan dan pengeditan adegan yang tidak pernah berlaku sebelum ini. Ini meletakkan 3DGS sebagai penukar permainan yang berpotensi untuk pembinaan semula dan perwakilan 3D generasi akan datang. Untuk tujuan ini, kami menyediakan gambaran keseluruhan sistematik tentang perkembangan dan kebimbangan terkini dalam bidang 3DGS buat kali pertama.

Ketahui tentang emoji Fasih 3D dalam Microsoft Teams

Apr 24, 2023 pm 10:28 PM

Ketahui tentang emoji Fasih 3D dalam Microsoft Teams

Apr 24, 2023 pm 10:28 PM

Anda mesti ingat, terutamanya jika anda adalah pengguna Teams, bahawa Microsoft telah menambah kumpulan baharu emoji 3DFluent pada apl persidangan video tertumpu kerjanya. Selepas Microsoft mengumumkan emoji 3D untuk Pasukan dan Windows tahun lepas, proses itu sebenarnya telah melihat lebih daripada 1,800 emoji sedia ada dikemas kini untuk platform. Idea besar ini dan pelancaran kemas kini emoji 3DFluent untuk Pasukan pertama kali dipromosikan melalui catatan blog rasmi. Kemas kini Pasukan Terkini membawa FluentEmojis ke aplikasi Microsoft mengatakan 1,800 emoji yang dikemas kini akan tersedia kepada kami setiap hari

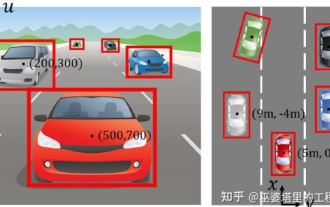

Pilih kamera atau lidar? Kajian terbaru tentang mencapai pengesanan objek 3D yang mantap

Jan 26, 2024 am 11:18 AM

Pilih kamera atau lidar? Kajian terbaru tentang mencapai pengesanan objek 3D yang mantap

Jan 26, 2024 am 11:18 AM

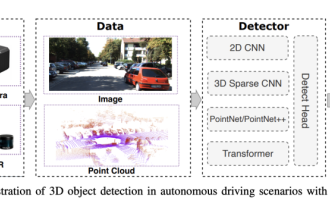

0. Ditulis di hadapan&& Pemahaman peribadi bahawa sistem pemanduan autonomi bergantung pada persepsi lanjutan, membuat keputusan dan teknologi kawalan, dengan menggunakan pelbagai penderia (seperti kamera, lidar, radar, dll.) untuk melihat persekitaran sekeliling dan menggunakan algoritma dan model untuk analisis masa nyata dan membuat keputusan. Ini membolehkan kenderaan mengenali papan tanda jalan, mengesan dan menjejaki kenderaan lain, meramalkan tingkah laku pejalan kaki, dsb., dengan itu selamat beroperasi dan menyesuaikan diri dengan persekitaran trafik yang kompleks. Teknologi ini kini menarik perhatian meluas dan dianggap sebagai kawasan pembangunan penting dalam pengangkutan masa depan satu. Tetapi apa yang menyukarkan pemanduan autonomi ialah memikirkan cara membuat kereta itu memahami perkara yang berlaku di sekelilingnya. Ini memerlukan algoritma pengesanan objek tiga dimensi dalam sistem pemanduan autonomi boleh melihat dan menerangkan dengan tepat objek dalam persekitaran sekeliling, termasuk lokasinya,

CLIP-BEVFormer: Selia secara eksplisit struktur BEVFormer untuk meningkatkan prestasi pengesanan ekor panjang

Mar 26, 2024 pm 12:41 PM

CLIP-BEVFormer: Selia secara eksplisit struktur BEVFormer untuk meningkatkan prestasi pengesanan ekor panjang

Mar 26, 2024 pm 12:41 PM

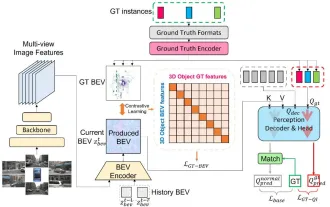

Ditulis di atas & pemahaman peribadi penulis: Pada masa ini, dalam keseluruhan sistem pemanduan autonomi, modul persepsi memainkan peranan penting Hanya selepas kenderaan pemanduan autonomi yang memandu di jalan raya memperoleh keputusan persepsi yang tepat melalui modul persepsi boleh Peraturan hiliran dan. modul kawalan dalam sistem pemanduan autonomi membuat pertimbangan dan keputusan tingkah laku yang tepat pada masanya dan betul. Pada masa ini, kereta dengan fungsi pemanduan autonomi biasanya dilengkapi dengan pelbagai penderia maklumat data termasuk penderia kamera pandangan sekeliling, penderia lidar dan penderia radar gelombang milimeter untuk mengumpul maklumat dalam modaliti yang berbeza untuk mencapai tugas persepsi yang tepat. Algoritma persepsi BEV berdasarkan penglihatan tulen digemari oleh industri kerana kos perkakasannya yang rendah dan penggunaan mudah, dan hasil keluarannya boleh digunakan dengan mudah untuk pelbagai tugas hiliran.

Cat 3D dalam Windows 11: Muat Turun, Pemasangan dan Panduan Penggunaan

Apr 26, 2023 am 11:28 AM

Cat 3D dalam Windows 11: Muat Turun, Pemasangan dan Panduan Penggunaan

Apr 26, 2023 am 11:28 AM

Apabila gosip mula tersebar bahawa Windows 11 baharu sedang dibangunkan, setiap pengguna Microsoft ingin tahu bagaimana rupa sistem pengendalian baharu itu dan apa yang akan dibawanya. Selepas spekulasi, Windows 11 ada di sini. Sistem pengendalian datang dengan reka bentuk baharu dan perubahan fungsi. Selain beberapa tambahan, ia disertakan dengan penamatan dan pengalihan keluar ciri. Salah satu ciri yang tidak wujud dalam Windows 11 ialah Paint3D. Walaupun ia masih menawarkan Paint klasik, yang bagus untuk laci, doodle dan doodle, ia meninggalkan Paint3D, yang menawarkan ciri tambahan yang sesuai untuk pencipta 3D. Jika anda mencari beberapa ciri tambahan, kami mengesyorkan Autodesk Maya sebagai perisian reka bentuk 3D terbaik. suka

Dapatkan isteri 3D maya dalam masa 30 saat dengan satu kad! Teks kepada 3D menjana manusia digital berketepatan tinggi dengan butiran liang yang jelas, menyambung dengan lancar dengan Maya, Unity dan alat pengeluaran lain

May 23, 2023 pm 02:34 PM

Dapatkan isteri 3D maya dalam masa 30 saat dengan satu kad! Teks kepada 3D menjana manusia digital berketepatan tinggi dengan butiran liang yang jelas, menyambung dengan lancar dengan Maya, Unity dan alat pengeluaran lain

May 23, 2023 pm 02:34 PM

ChatGPT telah menyuntik satu dos darah ayam ke dalam industri AI, dan segala-galanya yang dahulunya tidak dapat dibayangkan telah menjadi amalan asas hari ini. Text-to-3D, yang terus maju, dianggap sebagai tempat liputan seterusnya dalam medan AIGC selepas Difusi (imej) dan GPT (teks), dan telah mendapat perhatian yang tidak pernah berlaku sebelum ini. Tidak, produk yang dipanggil ChatAvatar telah dimasukkan ke dalam beta awam sederhana, dengan cepat memperoleh lebih 700,000 tontonan dan perhatian, dan telah dipaparkan di Spacesoftheweek. △ChatAvatar juga akan menyokong teknologi Imageto3D yang menjana aksara bergaya 3D daripada lukisan asal perspektif tunggal/berbilang perspektif Model 3D yang dihasilkan oleh versi beta semasa telah mendapat perhatian meluas.

Tafsiran mendalam algoritma persepsi visual 3D untuk pemanduan autonomi

Jun 02, 2023 pm 03:42 PM

Tafsiran mendalam algoritma persepsi visual 3D untuk pemanduan autonomi

Jun 02, 2023 pm 03:42 PM

Untuk aplikasi pemanduan autonomi, adalah perlu untuk melihat pemandangan 3D. Alasannya mudah sahaja. Kenderaan tidak boleh memandu berdasarkan hasil persepsi yang diperolehi daripada sesuatu imej. Oleh kerana jarak objek dan maklumat kedalaman tempat kejadian tidak dapat dicerminkan dalam hasil persepsi 2D, maklumat ini adalah kunci untuk sistem pemanduan autonomi untuk membuat pertimbangan yang betul ke atas persekitaran sekeliling. Secara umumnya, penderia visual (seperti kamera) kenderaan autonomi dipasang di atas badan kenderaan atau pada cermin pandang belakang di dalam kenderaan. Tidak kira di mana ia berada, apa yang kamera dapat adalah unjuran dunia sebenar dalam pandangan perspektif (PerspectiveView) (sistem koordinat dunia kepada sistem koordinat imej). Pandangan ini hampir sama dengan sistem penglihatan manusia,

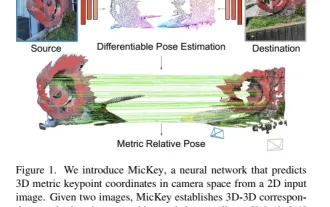

Yang terbaru dari Universiti Oxford! Mickey: Padanan imej 2D dalam SOTA 3D! (CVPR\'24)

Apr 23, 2024 pm 01:20 PM

Yang terbaru dari Universiti Oxford! Mickey: Padanan imej 2D dalam SOTA 3D! (CVPR\'24)

Apr 23, 2024 pm 01:20 PM

Pautan projek ditulis di hadapan: https://nianticlabs.github.io/mickey/ Memandangkan dua gambar, pose kamera di antara mereka boleh dianggarkan dengan mewujudkan kesesuaian antara gambar. Biasanya, surat-menyurat ini adalah 2D hingga 2D, dan anggaran pose kami adalah skala-tak tentu. Sesetengah aplikasi, seperti realiti tambahan segera pada bila-bila masa, di mana-mana sahaja, memerlukan anggaran pose metrik skala, jadi mereka bergantung pada penganggar kedalaman luaran untuk memulihkan skala. Makalah ini mencadangkan MicKey, proses pemadanan titik utama yang mampu meramalkan korespondensi metrik dalam ruang kamera 3D. Dengan mempelajari padanan koordinat 3D merentas imej, kami dapat membuat kesimpulan relatif metrik