Peranti teknologi

Peranti teknologi

AI

AI

Paten Microsoft AR/VR mencadangkan penggunaan pemacu resonan berbilang masa untuk menjana bekalan kuasa bipolar

Paten Microsoft AR/VR mencadangkan penggunaan pemacu resonan berbilang masa untuk menjana bekalan kuasa bipolar

Paten Microsoft AR/VR mencadangkan penggunaan pemacu resonan berbilang masa untuk menjana bekalan kuasa bipolar

(Nweon 5 Julai 2023) Penyelesaian pengesanan muka set kepala XR boleh digunakan untuk mengesan pergerakan kecil kulit pengguna. Dalam satu contoh penyelesaian, set kepala mungkin dilengkapi dengan litar untuk berbilang antena penderiaan yang terletak di lokasi yang berbeza. Isyarat antena boleh dimasukkan ke dalam litar resonans LC dan didorong ke resonans oleh pemacu LC. Output litar resonans LC boleh dimasukkan ke dalam penguat deria untuk memberikan isyarat yang sesuai kepada penukar analog-ke-digital ADC, yang boleh menukar isyarat deria ke dalam domain digital untuk pemprosesan selanjutnya.

Tetapi pelaksanaan konvensional litar pemacu resonans LC mungkin memerlukan tahap kuasa yang agak tinggi berbanding bateri biasa dalam peranti mudah alih. Kerana amplitud isyarat penderiaan litar resonans LC hendaklah sebesar mungkin untuk memaksimumkan julat dinamik keseluruhan dan resolusi yang mungkin semasa proses penukaran analog-ke-digital.

Selain itu, oleh kerana induktor adalah komponen besar dalam litar, jumlah bilangan komponen yang digunakan dalam keseluruhan sistem harus dikurangkan untuk mencapai faktor bentuk yang padat.

Untuk mengoptimumkan lagi, Microsoft mencadangkan dalam aplikasi paten yang dipanggil "Skim pemacu resonan pemultipleksan masa untuk menjana bekalan kekutuban dwi" bahawa skim pemacu resonan pemultipleksan masa boleh digunakan untuk menjana bekalan kuasa bipolar.

Litar pemacu resonan LC tidak perlu berjalan sepanjang masa, ia hanya perlu berjalan dalam mod kerja tertentu. Sebagai contoh, dalam skim pengesanan muka RF, apabila sensor memperoleh isyarat penderiaan, litar pemacu resonan LC boleh diaktifkan dalam satu tempoh masa, dan kemudian dalam tempoh masa yang lain, induktor boleh digunakan semula untuk bekalan kuasa bipolar , dengan itu menggunakan skim pemultipleksan masa bagi induktor. Skim pemultipleksan masa membantu untuk berkongsi modul litar yang sama dengan resonator separuh jambatan.

Litar pemacu resonan LC tradisional untuk penyelesaian penderia memerlukan voltan bekalan yang lebih tinggi kerana amplitud isyarat deria hendaklah sebesar mungkin untuk mencapai resolusi yang lebih tinggi. Oleh itu, Microsoft percaya bahawa skim pemacu resonan berbilang masa untuk menjana bekalan kuasa bipolar mungkin merupakan salah satu cara terbaik untuk melaksanakan sensor.

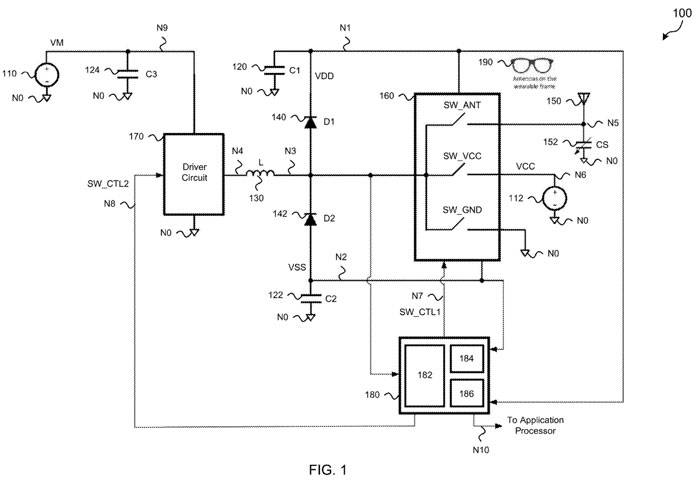

Sistem 100 pertama yang ditunjukkan dalam Rajah 1 menggunakan skema pemacu resonan berbilang masa untuk menjana kuasa bipolar dalam litar resonan LC dan boleh digunakan dalam aplikasi pengesanan muka RF. Seperti yang ditunjukkan dalam rajah, sistem 100 termasuk bateri 110, sumber DC 112, litar kapasitor pertama 120, litar kapasitor kedua 122, litar kapasitor ketiga 124, litar induktor 130, litar diod pertama 140, dan diod kedua Litar 142, antena 150, kapasitor deria 152, pemultipleks MUX 160, litar pemacu 170 dan litar pengawal 180. Antena 150 mungkin diletakkan di pelbagai lokasi pada peranti MR boleh pakai, seperti bingkai boleh pakai 190.

Bateri 110 digandingkan antara nod N9 dan nod NO untuk memberikan voltan bateri yang sepadan untuk VM nod N9. Sumber DC 112 digandingkan antara nod N6 dan nod NO dan memberikan voltan VCC pada nod N6. Litar kapasitif pertama 120 digandingkan antara nod N1 dan nod NO, ditetapkan C1. Litar kapasitor kedua 122 digandingkan antara nod N2 dan nod NO, yang ditetapkan kepada C2. Litar kapasitif ketiga 124 digandingkan antara nod N9 dan nod NO, ditetapkan C3.

Litar aruhan 130 digandingkan antara nod N3 dan nod N4, dinamakan l. Litar diod pertama 140 digandingkan antara nod N3 dan nod N1 dan ditetapkan D1. Litar diod kedua 142 digandingkan antara nod N2 dan nod N3, ditetapkan D2. Antena 150 digandingkan dengan nod N5 dan mempunyai kemuatan ciri yang sepadan dengan kapasitor pengesan 152 .

Kapasitor induktif 152 digandingkan antara nod N5 dan nod NO, CS yang ditetapkan. MUX 160 termasuk port input pada nod N3, port output pertama pada nod N5, port output kedua pada nod N6, port output ketiga pada nod NO, port kuasa pertama pada nod N1, port kuasa pertama pada nod N2 Second port kuasa dan port kawalan pada nod N7.

Litar pemanduan 170 termasuk port output nod N4, port kuasa pertama nod N9, port kuasa kedua nod NO dan port kawalan nod N8. Litar pengawal 180 termasuk port input pertama pada nod N1, port input kedua pada nod N2, port input ketiga pada nod N3, port output pertama pada nod N7, port output kedua pada nod N8, dan port output ketiga pada nod N10.

MUX 160 berfungsi bersama-sama dengan litar pemacu 170 untuk memultiplekskan masa pengecasan dan nyahcas litar induktor 130 secara berkesan pada nod N3 kepada antena 150 pada nod N7, bekalan kuasa DC 112 pada nod N6, atau tanah litar pada nod NO .

Kapasitor pengesanan 152 diwakili sebagai kapasitor dengan nilai kemuatan berubah CS, yang digandingkan antara nod N5 dan nod NO. Walaupun ditunjukkan sebagai komponen kapasitif fizikal, kemuatan pengesanan 152 sepadan dengan kemuatan ciri antena 150 . Memandangkan antena terletak secara fizikal pada bingkai boleh pakai 900, nilai kemuatan sebenar antena akan berbeza-beza berdasarkan kedekatan dengan kulit pengguna.

Litar aruhan 130 digandingkan secara berkesan secara bersiri antara output litar pemacu 170 dan antena 150. Daripada nod N4 melalui litar induktor 130 kepada kapasitor deria 152, litar penapis LC boleh dikenal pasti.

Litar pengawal 180 boleh dilaksanakan sebagai unit mikropengawal MCU. MCU boleh dikonfigurasikan melalui perisian atau arahan perisian tegar dan mengawal operasi litar 100 mengikut skema pemultipleksan pembahagian masa. Penyelesaiannya merangkumi tiga mod asas: pengecasan arah positif (mod pertama), pengecasan arah negatif (mod kedua), dan mengendalikan antena sebagai penderia untuk pengesanan gerakan muka (mod ketiga).

Dalam mod pertama, litar pengawal 180 mengaktifkan konfigurasi pertama litar pemanduan 170 melalui isyarat kawalan kedua SW_CTL2. Isyarat kawalan kedua menggabungkan nod N4 ke nod N9 supaya nod N4 sepadan dengan voltan bateri VM secara berkesan.

Juga dalam mod pertama ini, litar pengawal 180 berdenyut isyarat kawalan pertama SW_CTL1 untuk memodulasi konfigurasi suis pertama MUX 160 yang secara selektif menggandingkan nod N3 ke nod melalui litar suis ketiga dalam MUX 160 NO. Semasa tempoh nadi tinggi, litar gandingan nod N3 ke nod NO dibumikan, menyebabkan litar induktor 130 dari nod N4 ke nod N3 mengecas ke arah positif.

Semasa tempoh nadi rendah, nod N3 dipisahkan daripada nod NO, dan arus storan daripada litar induktor 130 mengalir melalui litar diod pertama 140, memindahkan cas ke litar kapasitor pertama 120 (C1). Lama kelamaan, denyutan berulang akan menyebabkan cas terkumpul pada litar kapasitor pertama 120 (C1) yang mencukupi untuk menghasilkan voltan bekalan positif VDD pada nod N1.

Semasa mod kedua, litar pengawal 180 mengaktifkan konfigurasi pemanduan kedua litar pemanduan 170 melalui isyarat kawalan kedua SW_CTL2. Isyarat kawalan menggabungkan nod N4 kepada nod NO supaya nod N4 sepadan dengan tanah litar secara berkesan.

Selain itu, dalam mod kedua, litar pengawal 180 nadi memodulasi konfigurasi suis kedua untuk MUX 160 melalui isyarat kawalan pertama SW_CTL1, dan suis secara selektif menukar nod N3 melalui litar suis kedua dalam MUX 160 Coupled to nod N6. Semasa tempoh nadi tinggi, nod N3 digandingkan kepada sumber DC 112 pada nod N6, menyebabkan litar induktor 130 mengecas ke arah negatif dari nod N3 ke nod N4.

Semasa tempoh nadi rendah, nod N3 dipisahkan daripada nod N6, dan arus storan daripada litar induktor 130 mengalir melalui litar diod kedua 140, memberikan cas kepada litar kapasitor kedua 122 (C2). Lama kelamaan, denyutan berulang akan menyebabkan pengumpulan cas pada litar kapasitor kedua 122 (C2) yang mencukupi untuk menghasilkan voltan bekalan negatif VSS pada nod N2.

Dalam mod ketiga, litar pengawal 180 memilih konfigurasi suis ketiga untuk MUX 160 melalui isyarat kawalan pertama SW_CTL1. Suis menggandingkan nod N3 kepada nod N5 melalui suis litar suis pertama dalam MUX 160 .

Juga dalam mod ketiga, litar pengawal 180 secara selektif mengaktifkan litar pemanduan 170 melalui isyarat kawalan kedua SW_CTL2. Isyarat kawalan kedua berdenyut modulasi nod N4 digandingkan antara nod N9 dan nod NO. Dalam mod ketiga ini, litar induktif 130 digandingkan dengan antena 150 dan kapasitor pengesan cirinya 152 (CS), membentuk litar resonans LC.

Dengan memodulasi nadi pada gandingan nod N4 antara nod N9 dan nod NO, litar resonans LC teruja untuk menghasilkan isyarat ayunan yang boleh diperhatikan pada nod N3, yang boleh digunakan untuk pengesanan muka. Voltan bekalan dwi (VDD, VSS) yang dijana sebelum ini dalam mod pertama dan kedua digunakan untuk mengendalikan pelbagai litar, manakala litar resonan LC teruja dalam mod ketiga. Berdasarkan ciri resonans Q tinggi penapis LC, tindak balas sementara akan sepadan dengan isyarat AC pada nod N3.

Litar pengawal 180 boleh dikonfigurasikan untuk menangkap isyarat deria daripada nod N3, yang kemudiannya boleh disediakan sebagai isyarat digital kepada nod N10 kepada sistem lain untuk pemprosesan selanjutnya. Disebabkan oleh ciri-ciri tinggi penapis LC, isyarat deria mungkin mempunyai voltan puncak ke puncak yang ketara. Oleh itu, litar tambahan mungkin diperlukan untuk mengecilkan saiz isyarat sebelum dinilai oleh litar pengawal 180.

Rajah 1 menggambarkan konfigurasi induktor dwiguna yang digunakan untuk menjana bekalan voltan DC dan sebagai penukar DC-AC untuk pengesanan gerakan muka RF, yang sesuai untuk sistem mudah alih yang menggunakan kuasa bateri.

Microsoft menyatakan bahawa sistem yang dicadangkan termasuk penapis LC (atau resonator) dengan faktor kualiti yang tinggi, di mana penapis LC menggunakan litar aruhan bersiri digabungkan dengan kapasitor penderiaan yang dibentuk oleh antena penderiaan dan kulit muka pengguna. Penapis LC dikonfigurasikan untuk menguatkan voltan AC sumber kuasa AC pada frekuensi resonans sistem pengesan muka frekuensi radio.

Aspek penting skema yang diterangkan ialah sistem pengesanan muka mendapat manfaat daripada kerumitan litar yang dikurangkan.

Kekerapan resonan penapis LC berubah apabila kemuatan penderiaan antena berubah, yang berubah mengikut pergerakan muka berbanding kedudukan antena. Untuk frekuensi input tetap yang diberikan, keuntungan dan fasa isyarat keluaran penapis LC akan berubah sebagai fungsi perubahan kapasitans yang dikesan. Oleh kerana perolehan puncak dan Q tinggi pada frekuensi resonan penapis LC, isyarat keluaran yang sangat besar boleh dicapai dengan isyarat input yang agak kecil.

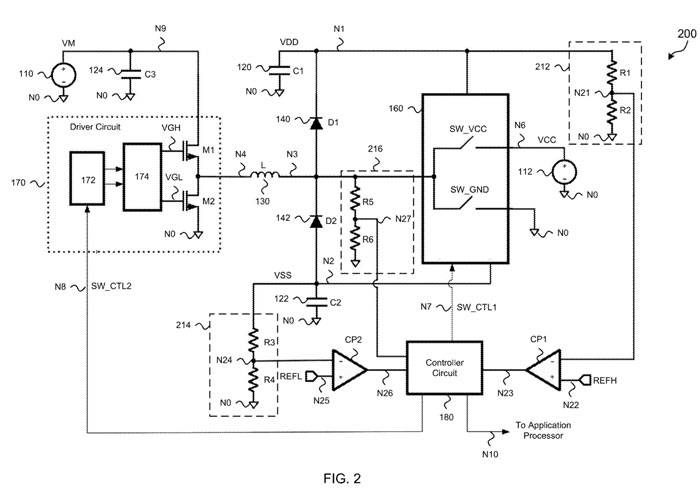

Sistem kedua 200 yang ditunjukkan dalam Rajah 2 menggunakan skema pemacu resonan berbilang masa untuk menjana kuasa bipolar dalam litar resonan LC dan boleh digunakan dalam aplikasi pengesanan muka RF. Seperti yang ditunjukkan dalam rajah, sistem 200 termasuk bateri 110, sumber DC 112, litar kapasitor pertama 120, litar kapasitor kedua 122, litar kapasitor ketiga 124, litar induktor 130, litar diod pertama 140, dan diod kedua Litar 142, pemultipleks MUX 160, litar pemacu 170 dan litar pengawal 180.

Berbanding dengan Rajah 1, sistem Rajah 2 termasuk dua pembanding CP1 dan CP2, dan tiga pembahagi voltan atau litar penskalaan (212, 214 dan 216). Litar pembahagi voltan pertama 212 termasuk dua perintang R1, R2 digabungkan secara bersiri antara nod N1 dan nod NO, dan output litar pembahagi voltan pertama sepadan dengan nod N21.

Komparator CP1 pertama termasuk input penyongsangan (−) digandingkan ke nod N21, input bukan penyongsangan (+) digandingkan ke nod N22 dan output digandingkan ke nod N23. Litar pembahagi voltan kedua 214 termasuk dua perintang R3, R4 digabungkan secara bersiri antara nod N2 dan nod NO, keluaran litar pembahagi voltan kedua sepadan dengan nod N24.

Pembanding kedua CP2 termasuk input penyongsangan (−) digandingkan ke nod N24, input bukan penyongsangan (+) digandingkan ke nod N25 dan output digandingkan ke nod N26. Litar pembahagi voltan ketiga 216 termasuk dua perintang R5, R6 digabungkan secara bersiri antara nod N3 dan nod NO, keluaran litar pembahagi voltan kedua sepadan dengan nod N27.

Litar pembahagi voltan di atas dikonfigurasikan untuk mengurangkan voltan daripada salah satu nod input yang sepadan ke tahap yang sesuai untuk pemprosesan selanjutnya. Sebagai contoh, litar pembahagi voltan pertama yang terdiri daripada perintang R1 dan R2 mengesan voltan pada nod N1 dan menghasilkan versi berskala voltan yang dikesan pada nod N21.

Begitu juga, litar pembahagi voltan kedua yang terdiri daripada perintang R3 dan R4 mengesan voltan pada nod N2 dan menghasilkan versi berskala voltan deria pada nod N24 manakala litar pembahagi voltan ketiga terdiri daripada perintang R5 dan R6 Voltan nod N3; dikesan dan versi berskala voltan deria nod N27 dijana.

Komparator CP1 dan CP2 dikonfigurasikan untuk mengesan apabila voltan yang sepadan pada inputnya mencapai voltan sasaran. Sebagai contoh, CP1 pembanding pertama dikonfigurasikan untuk membandingkan voltan penderiaan nod N21 dengan voltan rujukan pertama REFH, dan menjana isyarat pada nod N23.

Begitu juga, konfigurasikan pembanding kedua CP2 untuk membandingkan voltan penderiaan nod N24 dengan voltan rujukan kedua REFL, dan menjana isyarat pada nod N26.

Litar pengawal 180 menggunakan isyarat daripada nod N23 dan N26 sebagai input untuk mengawal masa pengecasan dan kitaran tugas litar induktor 130.

Keluaran litar pembahagi voltan ketiga 216 ditunjukkan digandingkan dengan input litar pengawal 180 pada nod N27. Input ini sepadan dengan versi berskala voltan deria pada nod N3. Dalam operasi, voltan pada nod N3 boleh mewakili tindak balas litar resonan LC, seperti litar resonan LC yang terdiri daripada induktor 130 dan kapasitor penderia 152 seperti yang ditunjukkan dalam Rajah 1. Tindak balas litar resonans LC yang diukur pada nod N27 boleh ditukar kepada nilai digital oleh ADC 184 dalam litar pengawal 180 .

Pelaksanaan terperinci litar pemacu 170 juga ditunjukkan dalam Rajah 2, yang merangkumi blok logik 172, blok pemacu get 174, transistor kesan medan M1 dan transistor kesan medan M2. Blok logik 172 termasuk port input yang digandingkan dengan nod N8 dan sepasang output yang digabungkan dengan blok pemacu get 174 . Blok pemacu pagar 177 termasuk keluaran pertama (VGH) yang digandingkan dengan pagar FET M1 dan keluaran kedua (VGL) digandingkan dengan pintu pagar FET M2.

FET M1 termasuk kedua-dua longkang yang digandingkan dengan nod N9 dan sumber yang digabungkan dengan nod N4. FET M2 termasuk kedua-dua longkang yang digandingkan dengan nod N4 dan sumber yang digabungkan dengan nod NO. Secara operasi, isyarat pada nod N8 mungkin mewakili isyarat kawalan tunggal atau isyarat kawalan berbilang yang mengawal pemasaan dan kitaran tugas pengecasan induktor melalui litar pemacu 170 .

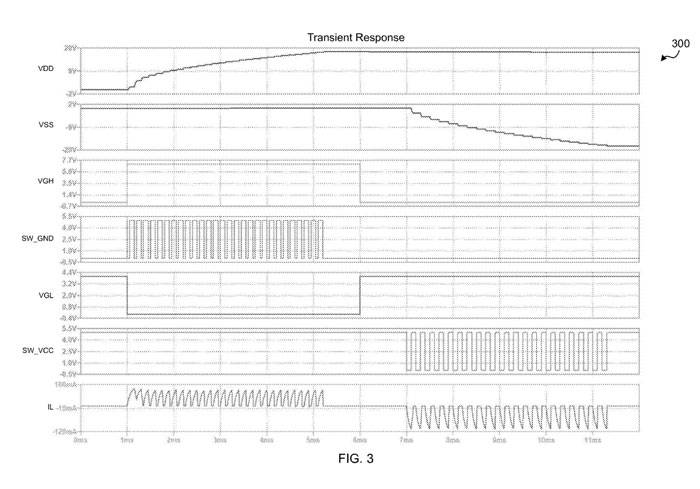

Rajah 3 menunjukkan tindak balas sementara untuk contoh skema pemacu resonan berbilang masa, seperti sistem contoh yang digunakan untuk FIGS. 3 termasuk bentuk gelombang voltan bekalan kuasa dwi (VDD, VSS), isyarat kawalan pintu tinggi dan rendah (VGH, VGL) litar pemanduan 170 , isyarat kawalan suis pertama dan kedua litar pemultipleksan 160 , dan aliran dalam litar induktor 130 Bentuk gelombang arus arus.

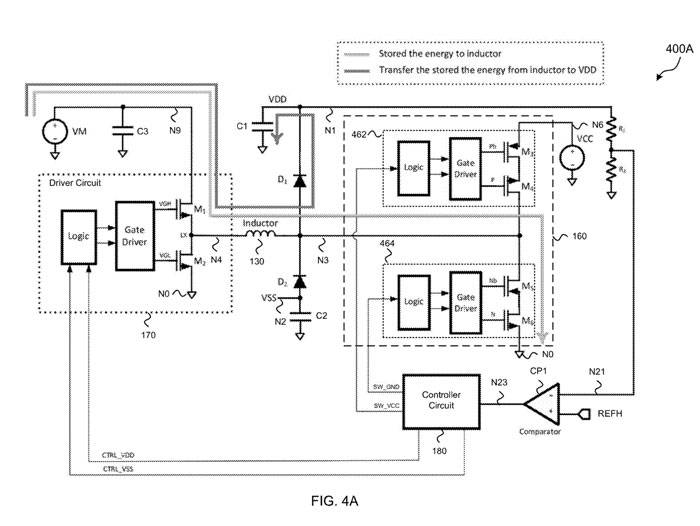

Rajah 4A menunjukkan bahagian pertama operasi contoh ketiga skema pemacu resonan berganda masa untuk menjana kuasa bipolar dalam litar resonan LC.

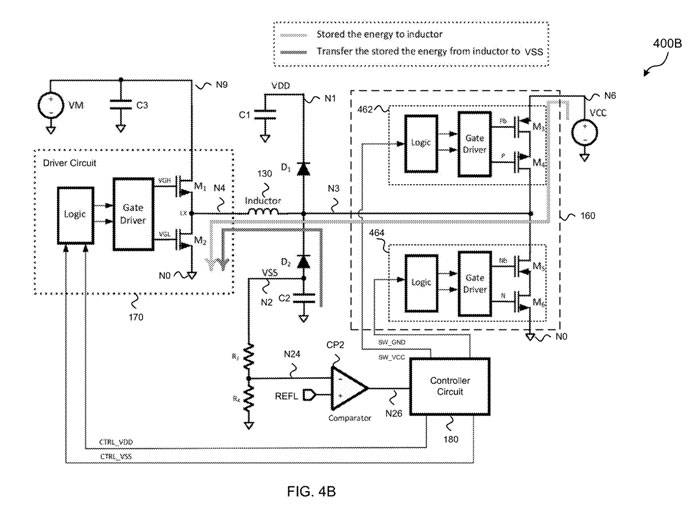

Rajah 4B menunjukkan bahagian kedua operasi skema pemacu resonan berbilang masa contoh ketiga untuk menjana kuasa bipolar dalam litar resonan LC.

Rajah 2, 4A dan 4B mewakili transistor kesan medan pertama dan transistor kesan medan kedua termasuk transistor kesan medan jenis-n. Bekalan bipolar (VDD, VSS) boleh dijana melalui pengendalian litar pemacu 170 sebagai resonator separuh jambatan, dengan dua suis disambungkan kepada sumber voltan DC dan dibumikan melalui pengendalian pemultipleks.

Pada mulanya, kapasitor C1 atau C2 mungkin tidak menyimpan cas, jadi voltan bekalan VDD dan VSS pada nod N1 dan N2 mungkin tidak seperti yang diperlukan. Pembanding CP1 membandingkan voltan nod N1 dengan voltan rujukan positif REFH melalui keluaran pembahagi voltan pertama (R1, R2) nod N21 dan menjana keluaran pembanding pada nod N23.

Komparator CP2 (melalui output pembahagi voltan kedua (R3, R4) pada nod N24 membandingkan voltan pada nod N2 dengan voltan rujukan negatif REFL dan menghasilkan output pembanding pada nod N26.

Litar pengawal 180 menilai voltan nod N23 dan N26 untuk menentukan sama ada voltan tidak pada nilai yang dijangkakan, dan menjana satu atau lebih isyarat kawalan untuk memulakan proses pengecasan bekalan kuasa.

Seperti yang ditunjukkan dalam Rajah 4A, apabila VDD bekalan kuasa pada nod N1 terlalu rendah, FET M2 sisi tinggi bagi resonator separuh jambatan diaktifkan (jika VGH tinggi), manakala FET M2 bahagian rendah dinyahaktifkan, dengan itu menjana bekalan kuasa yang positif. Isyarat kawalan kemudiannya digunakan untuk mengawal litar suis 464 kepada litar nod gandingan tanah N3 litar induktor 130 kepada nod NO.

Apabila litar suis 464 berada dalam keadaan tertutup, arus mengalir dari bateri VM melalui litar pemacu ke litar induktor 130 pada nod N4 Nod N3 digandingkan ke tanah litar di nod NO melalui litar suis 464 Litar induktor 130 menyimpan arus dengan berkesan ke arah hadapan.

Apabila litar suis 464 berada dalam keadaan litar terbuka, tenaga yang disimpan dalam arus litar induktor 130 mengalir ke nod N1 melalui litar diod D1, di mana kapasitor C1 menyimpan cas dan meningkatkan voltan bekalan kuasa VDD dengan sewajarnya. Sepanjang berbilang kitaran modulasi ini, nilai VDD bekalan positif akan meningkat sehingga paras voltan positif yang dikehendaki dicapai dan pembanding CP1 akan tersandung untuk memberitahu litar pengawal 180 bahawa paras yang dikehendaki telah dicapai. Setelah VDD bekalan positif mencapai nilai yang dikehendaki, FET M1 pensuisan sisi tinggi litar pemacu 170 dinyahaktifkan oleh litar pengawal 180 .

Seperti yang ditunjukkan dalam Rajah 4B, apabila kuasa VSS pada nod N2 terlalu tinggi, FET M2 bahagian rendah resonator separuh jambatan diaktifkan, manakala FET M1 bahagian tinggi dinyahaktifkan, mengakibatkan bekalan kuasa negatif. Isyarat kawalan kemudiannya digunakan untuk memodulasi litar pensuisan 462 kepada sumber DC nod N3 kepada nod N6 litar induktor 130 atau VCC.

Apabila litar suis 462 berada dalam keadaan tertutup, arus mengalir dari sumber DC VCC pada nod N6 melalui litar induktor 130 pada nod N3, di mana nod N4 digandingkan ke pembumian litar pada nod NO melalui litar pemacu 170, dan litar induktor 130 secara berkesan membalikkan penyimpanan semasa.

Apabila litar suis 462 berada dalam keadaan litar terbuka, arus storan dalam litar induktor 130 mengalir dari nod tanah NO, mencapai nod N3 melalui kapasitor C2 dan litar diod D1. Dalam nod N3, tenaga induktor dipindahkan ke kapasitor C2, dengan itu mengurangkan voltan bekalan VSS.

Melalui berbilang kitaran modulasi ini, nilai VSS bekalan negatif akan berkurangan sehingga tahap bekalan voltan negatif yang dikehendaki dicapai dan pembanding CP2 akan tersandung untuk memberitahu litar pengawal 180 bahawa tahap yang dikehendaki telah dicapai. Setelah VSS bekalan negatif berada pada nilai yang dikehendaki, FET M2 pensuisan sisi rendah litar pemacu 170 dinyahaktifkan oleh litar pengawal 180 .

Paten berkaitan: Paten Microsoft |. Skim pemacu resonan berbilang masa untuk menjana bekalan dwi kekutuban

Aplikasi paten Microsoft bertajuk "Skim pemacu resonan berganda masa untuk menjana bekalan kekutuban dwi" pada asalnya diserahkan pada Disember 2021 dan baru-baru ini diterbitkan oleh Pejabat Paten dan Tanda Dagangan AS.

Atas ialah kandungan terperinci Paten Microsoft AR/VR mencadangkan penggunaan pemacu resonan berbilang masa untuk menjana bekalan kuasa bipolar. Untuk maklumat lanjut, sila ikut artikel berkaitan lain di laman web China PHP!

Alat AI Hot

Undresser.AI Undress

Apl berkuasa AI untuk mencipta foto bogel yang realistik

AI Clothes Remover

Alat AI dalam talian untuk mengeluarkan pakaian daripada foto.

Undress AI Tool

Gambar buka pakaian secara percuma

Clothoff.io

Penyingkiran pakaian AI

AI Hentai Generator

Menjana ai hentai secara percuma.

Artikel Panas

Alat panas

Notepad++7.3.1

Editor kod yang mudah digunakan dan percuma

SublimeText3 versi Cina

Versi Cina, sangat mudah digunakan

Hantar Studio 13.0.1

Persekitaran pembangunan bersepadu PHP yang berkuasa

Dreamweaver CS6

Alat pembangunan web visual

SublimeText3 versi Mac

Perisian penyuntingan kod peringkat Tuhan (SublimeText3)

Topik panas

1376

1376

52

52

Saya cuba pengekodan getaran dengan kursor AI dan ia menakjubkan!

Mar 20, 2025 pm 03:34 PM

Saya cuba pengekodan getaran dengan kursor AI dan ia menakjubkan!

Mar 20, 2025 pm 03:34 PM

Pengekodan Vibe membentuk semula dunia pembangunan perisian dengan membiarkan kami membuat aplikasi menggunakan bahasa semulajadi dan bukannya kod yang tidak berkesudahan. Diilhamkan oleh penglihatan seperti Andrej Karpathy, pendekatan inovatif ini membolehkan Dev

Top 5 Genai dilancarkan pada Februari 2025: GPT-4.5, Grok-3 & More!

Mar 22, 2025 am 10:58 AM

Top 5 Genai dilancarkan pada Februari 2025: GPT-4.5, Grok-3 & More!

Mar 22, 2025 am 10:58 AM

Februari 2025 telah menjadi satu lagi bulan yang berubah-ubah untuk AI generatif, membawa kita beberapa peningkatan model yang paling dinanti-nantikan dan ciri-ciri baru yang hebat. Dari Xai's Grok 3 dan Anthropic's Claude 3.7 Sonnet, ke Openai's G

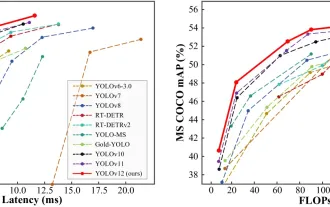

Bagaimana cara menggunakan Yolo V12 untuk pengesanan objek?

Mar 22, 2025 am 11:07 AM

Bagaimana cara menggunakan Yolo V12 untuk pengesanan objek?

Mar 22, 2025 am 11:07 AM

Yolo (anda hanya melihat sekali) telah menjadi kerangka pengesanan objek masa nyata yang terkemuka, dengan setiap lelaran bertambah baik pada versi sebelumnya. Versi terbaru Yolo V12 memperkenalkan kemajuan yang meningkatkan ketepatan

Adakah chatgpt 4 o tersedia?

Mar 28, 2025 pm 05:29 PM

Adakah chatgpt 4 o tersedia?

Mar 28, 2025 pm 05:29 PM

CHATGPT 4 kini tersedia dan digunakan secara meluas, menunjukkan penambahbaikan yang ketara dalam memahami konteks dan menjana tindak balas yang koheren berbanding dengan pendahulunya seperti ChATGPT 3.5. Perkembangan masa depan mungkin merangkumi lebih banyak Inter yang diperibadikan

Google ' s Gencast: Peramalan Cuaca dengan Demo Mini Gencast

Mar 16, 2025 pm 01:46 PM

Google ' s Gencast: Peramalan Cuaca dengan Demo Mini Gencast

Mar 16, 2025 pm 01:46 PM

Google Deepmind's Gencast: AI Revolusioner untuk Peramalan Cuaca Peramalan cuaca telah menjalani transformasi dramatik, bergerak dari pemerhatian asas kepada ramalan berkuasa AI yang canggih. Google Deepmind's Gencast, tanah air

AI mana yang lebih baik daripada chatgpt?

Mar 18, 2025 pm 06:05 PM

AI mana yang lebih baik daripada chatgpt?

Mar 18, 2025 pm 06:05 PM

Artikel ini membincangkan model AI yang melampaui chatgpt, seperti Lamda, Llama, dan Grok, menonjolkan kelebihan mereka dalam ketepatan, pemahaman, dan kesan industri. (159 aksara)

O1 vs GPT-4O: Adakah model baru OpenAI ' lebih baik daripada GPT-4O?

Mar 16, 2025 am 11:47 AM

O1 vs GPT-4O: Adakah model baru OpenAI ' lebih baik daripada GPT-4O?

Mar 16, 2025 am 11:47 AM

Openai's O1: Hadiah 12 Hari Bermula dengan model mereka yang paling berkuasa Ketibaan Disember membawa kelembapan global, kepingan salji di beberapa bahagian dunia, tetapi Openai baru sahaja bermula. Sam Altman dan pasukannya melancarkan mantan hadiah 12 hari

Penjana Seni AI Terbaik (Percuma & amp; Dibayar) untuk projek kreatif

Apr 02, 2025 pm 06:10 PM

Penjana Seni AI Terbaik (Percuma & amp; Dibayar) untuk projek kreatif

Apr 02, 2025 pm 06:10 PM

Artikel ini mengkaji semula penjana seni AI atas, membincangkan ciri -ciri mereka, kesesuaian untuk projek kreatif, dan nilai. Ia menyerlahkan Midjourney sebagai nilai terbaik untuk profesional dan mengesyorkan Dall-E 2 untuk seni berkualiti tinggi dan disesuaikan.