Tutorial Perkakasan

Tutorial Perkakasan

Berita Perkakasan

Berita Perkakasan

Enjin pelaksanaan AMD Zen 5 terdedah: menggunakan FPU 512-bit sebenar

Enjin pelaksanaan AMD Zen 5 terdedah: menggunakan FPU 512-bit sebenar

Enjin pelaksanaan AMD Zen 5 terdedah: menggunakan FPU 512-bit sebenar

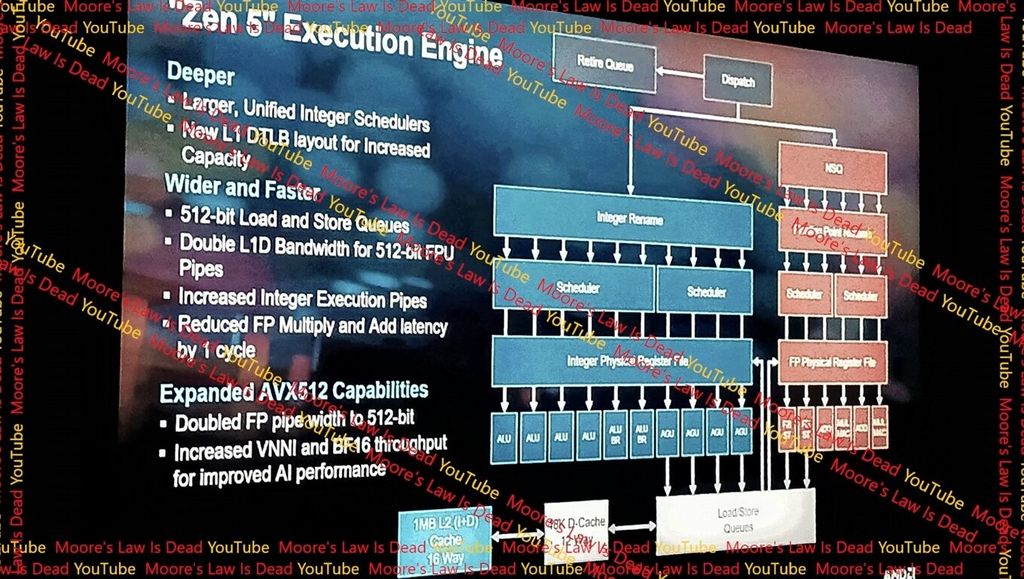

Berita dari laman web ini pada 5 April. Dalam video terbaru, sumber Moore's Law is Dead berkongsi maklumat mengenai enjin pelaksanaan pemproses AMD Zen 5 (Enjin Pelaksanaan), mengatakan bahawa ia akan menggunakan unit Operasi titik terapung 512-bit yang benar (FPU). ).

Menurut slaid yang dikongsi oleh sumber, enjin pelaksanaan Zen 5 diterangkan secara terperinci, menggunakan FPU 512-bit sebenar.

Pemproses AMD Zen 4 menggunakan FPU 256-bit dwi-saluran apabila melaksanakan beban kerja arahan AVX-512, manakala Zen 5 menggunakan FPU 512-bit sebenar untuk memproses arahan AVX atau VNNI 512-bit Akan ada prestasi yang lebih tinggi.

Tapak ini juga mengetahui daripada laporan bahawa AMD telah menaik taraf komponen berkaitan untuk FPU 512-bit, meningkatkan kapasiti L1 DTLB, mengembangkan baris gilir penyimpanan beban, menggandakan lebar jalur cache data L1 dan meningkatkan saiz sebanyak 50 %. Saiz L1D telah meningkat daripada 32 KB dalam "Zen 4" kepada 48 KB sekarang.

Latensi FPU MADD dikurangkan sebanyak 1 kitaran. Sebagai tambahan kepada FPU, AMD telah meningkatkan bilangan paip pelaksanaan Integer daripada 8 (Zen 4) kepada 10, dan saiz cache L2 eksklusif bagi setiap teras masih 1 MB.

Atas ialah kandungan terperinci Enjin pelaksanaan AMD Zen 5 terdedah: menggunakan FPU 512-bit sebenar. Untuk maklumat lanjut, sila ikut artikel berkaitan lain di laman web China PHP!

Alat AI Hot

Undresser.AI Undress

Apl berkuasa AI untuk mencipta foto bogel yang realistik

AI Clothes Remover

Alat AI dalam talian untuk mengeluarkan pakaian daripada foto.

Undress AI Tool

Gambar buka pakaian secara percuma

Clothoff.io

Penyingkiran pakaian AI

Video Face Swap

Tukar muka dalam mana-mana video dengan mudah menggunakan alat tukar muka AI percuma kami!

Artikel Panas

Alat panas

Notepad++7.3.1

Editor kod yang mudah digunakan dan percuma

SublimeText3 versi Cina

Versi Cina, sangat mudah digunakan

Hantar Studio 13.0.1

Persekitaran pembangunan bersepadu PHP yang berkuasa

Dreamweaver CS6

Alat pembangunan web visual

SublimeText3 versi Mac

Perisian penyuntingan kod peringkat Tuhan (SublimeText3)

Topik panas

1655

1655

14

14

1414

1414

52

52

1307

1307

25

25

1253

1253

29

29

1227

1227

24

24

ASUS memperkenalkan Adol Book 14 Air dengan AMD Ryzen 9 8945H dan dispenser kemenyan yang ingin tahu

Aug 01, 2024 am 11:12 AM

ASUS memperkenalkan Adol Book 14 Air dengan AMD Ryzen 9 8945H dan dispenser kemenyan yang ingin tahu

Aug 01, 2024 am 11:12 AM

ASUS sudah menawarkan pelbagai komputer riba 14-inci, termasuk Zenbook 14 OLED (sekira $1,079.99 di Amazon). Kini, ia telah memutuskan untuk memperkenalkan Adol Book 14 Air, yang kelihatan seperti komputer riba 14-inci biasa pada bahagian mukanya. Walau bagaimanapun, meta yang tidak mencolok

AMD Radeon RX 7800M dalam OneXGPU 2 mengatasi prestasi GPU Komputer Riba Nvidia RTX 4070

Sep 09, 2024 am 06:35 AM

AMD Radeon RX 7800M dalam OneXGPU 2 mengatasi prestasi GPU Komputer Riba Nvidia RTX 4070

Sep 09, 2024 am 06:35 AM

OneXGPU 2 ialah eGPU pertama yang menampilkan Radeon RX 7800M, GPU yang masih belum diumumkan oleh AMD. Seperti yang didedahkan oleh One-Netbook, pengeluar penyelesaian kad grafik luaran, GPU AMD baharu adalah berdasarkan seni bina RDNA 3 dan mempunyai Navi

Perisian Ryzen AI mendapat sokongan untuk pemproses Strix Halo dan Kraken Point AMD Ryzen baharu

Aug 01, 2024 am 06:39 AM

Perisian Ryzen AI mendapat sokongan untuk pemproses Strix Halo dan Kraken Point AMD Ryzen baharu

Aug 01, 2024 am 06:39 AM

Komputer riba AMD Strix Point baru sahaja memasuki pasaran, dan pemproses Strix Halo generasi seterusnya dijangka akan dikeluarkan pada tahun hadapan. Walau bagaimanapun, syarikat itu telah menambah sokongan untuk APU Strix Halo dan Krackan Point kepada perisian Ryzen AInya.

Cip AMD Z2 Extreme untuk konsol pegang tangan dijangka pelancaran awal 2025

Sep 07, 2024 am 06:38 AM

Cip AMD Z2 Extreme untuk konsol pegang tangan dijangka pelancaran awal 2025

Sep 07, 2024 am 06:38 AM

Walaupun AMD membuat khusus Ryzen Z1 Extreme (dan varian bukan Extreme) untuk konsol pegang tangan, cip itu hanya pernah ditemui dalam dua pegang tangan arus perdana, Asus ROG Ally (kurr. $569 di Amazon) dan Lenovo Legion Go (tiga). jika anda mengira R

AMD mengumumkan kerentanan keterukan tinggi 'Sinkclose', menjejaskan berjuta-juta pemproses Ryzen dan EPYC

Aug 10, 2024 pm 10:31 PM

AMD mengumumkan kerentanan keterukan tinggi 'Sinkclose', menjejaskan berjuta-juta pemproses Ryzen dan EPYC

Aug 10, 2024 pm 10:31 PM

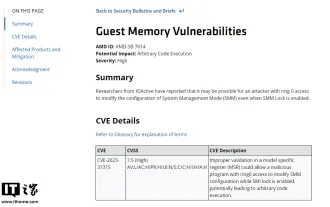

Menurut berita dari laman web ini pada 10 Ogos, AMD secara rasmi mengesahkan bahawa beberapa pemproses EPYC dan Ryzen mempunyai kelemahan baharu yang dipanggil "Sinkclose" dengan kod "CVE-2023-31315", yang mungkin melibatkan berjuta-juta pengguna AMD di seluruh dunia. Jadi, apakah itu Sinkclose? Menurut laporan oleh WIRED, kerentanan itu membenarkan penceroboh menjalankan kod hasad dalam "Mod Pengurusan Sistem (SMM)." Didakwa, penceroboh boleh menggunakan jenis perisian hasad yang dipanggil bootkit untuk mengawal sistem pihak lain, dan perisian hasad ini tidak dapat dikesan oleh perisian anti-virus. Nota dari tapak ini: Mod Pengurusan Sistem (SMM) ialah mod kerja CPU khas yang direka untuk mencapai pengurusan kuasa lanjutan dan fungsi bebas sistem pengendalian.

Mini PC Minisforum pertama dengan Ryzen AI 9 HX 370 dikhabarkan akan dilancarkan dengan tanda harga yang tinggi

Sep 29, 2024 am 06:05 AM

Mini PC Minisforum pertama dengan Ryzen AI 9 HX 370 dikhabarkan akan dilancarkan dengan tanda harga yang tinggi

Sep 29, 2024 am 06:05 AM

Aoostar adalah antara yang pertama mengumumkan PC mini Strix Point, dan kemudiannya, Beelink melancarkan SER9dengan tanda harga permulaan yang melambung tinggi sebanyak $999. Minisforum menyertai parti dengan menggoda EliteMini AI370, dan seperti namanya, ia akan menjadi syarikat

Beelink SER9: PC mini AMD Zen 5 padat diumumkan dengan iGPU Radeon 890M tetapi pilihan eGPU terhad

Sep 12, 2024 pm 12:16 PM

Beelink SER9: PC mini AMD Zen 5 padat diumumkan dengan iGPU Radeon 890M tetapi pilihan eGPU terhad

Sep 12, 2024 pm 12:16 PM

Beelink terus memperkenalkan PC mini baharu dan aksesori yang disertakan pada kadar simpulan. Untuk mengimbas kembali, lebih kurang sebulan telah berlalu sejak ia mengeluarkan dok EQi12, EQR6 dan EX eGPU. Kini, syarikat itu telah menumpukan perhatiannya kepada Strix baharu AMD

Tawaran | Lenovo ThinkPad P14s Gen 5 dengan 120Hz OLED, 64GB RAM dan AMD Ryzen 7 Pro mendapat potongan 60% sekarang

Sep 07, 2024 am 06:31 AM

Tawaran | Lenovo ThinkPad P14s Gen 5 dengan 120Hz OLED, 64GB RAM dan AMD Ryzen 7 Pro mendapat potongan 60% sekarang

Sep 07, 2024 am 06:31 AM

Ramai pelajar akan kembali ke sekolah hari ini, dan mungkin ada yang perasan bahawa komputer riba lama mereka tidak lagi berfungsi. Sesetengah pelajar kolej mungkin berada di pasaran untuk buku nota perniagaan mewah dengan skrin OLED yang cantik, dalam hal ini t