TechInsights:3D、4F2 等新結構 DRAM 記憶體預計 0C 節點量產

本站7 月26 日消息,根據韓媒The Elec 報道,來自分析機構TechInsights 的Choi Jeong-dong 博士表示,採用3D、4F2、VCT(垂直通道電晶體)等創新結構的DRAM 記憶體有望於0C nm 節點實現量產。

0C nm 即第 3 代 10nm 以下級節點。目前三大 DRAM 原廠最先進的製程是 1b (1β) nm,即第 6 代 20~10 奈米級節點。

Choi 認為,在下代 1c nm 後,DRAM 記憶體產業也將經歷 1d nm 節點才會將名義流程縮小至 10nm 以下。

四到五年前有部分業內人士認為,採用新結構的 DRAM 內存在 1d~0a nm 世代就能面世。

但目前看來 3D DRAM、4F2 DRAM 等技術仍不成熟,即使情況順利,量產至少也要等到 0b nm。以 3D DRAM 為例,仍在測試 8、12 層堆疊的記憶體樣品,離 60、90 層堆疊的目標還有很長的路要求。

Choi 表示,直到1b nm 製程,可減少漏電流的HKMG (本站註:高介電常數(材料)/金屬閘極)製程還漏電流的HKMG (本站注:高介電常數(材料)/金屬閘極)製程還僅在GDDR、DDR5、LPDDR 的部分產品中應用;

而到1c nm 節點,HKMG 製程將被三星電子和SK 海力士廣泛應用於所有類型的產品。

至於現有DRAM 產品,1b nm 從三季度開始從1a nm 手中拿下出貨量最高製程的頭銜;

而在1b nm DRAM 中,三星電子的產品尺寸最小、SK 海力士的略大、美光的最大,但差距並不顯著。

以上是TechInsights:3D、4F2 等新結構 DRAM 記憶體預計 0C 節點量產的詳細內容。更多資訊請關注PHP中文網其他相關文章!

熱AI工具

Undresser.AI Undress

人工智慧驅動的應用程序,用於創建逼真的裸體照片

AI Clothes Remover

用於從照片中去除衣服的線上人工智慧工具。

Undress AI Tool

免費脫衣圖片

Clothoff.io

AI脫衣器

Video Face Swap

使用我們完全免費的人工智慧換臉工具,輕鬆在任何影片中換臉!

熱門文章

熱工具

記事本++7.3.1

好用且免費的程式碼編輯器

SublimeText3漢化版

中文版,非常好用

禪工作室 13.0.1

強大的PHP整合開發環境

Dreamweaver CS6

視覺化網頁開發工具

SublimeText3 Mac版

神級程式碼編輯軟體(SublimeText3)

消息指出 SK 海力士五層堆疊 3D DRAM 記憶體良率已達 56.1%

Jun 24, 2024 pm 01:52 PM

消息指出 SK 海力士五層堆疊 3D DRAM 記憶體良率已達 56.1%

Jun 24, 2024 pm 01:52 PM

本站 6 月 24 日消息,韓媒 BusinessKorea 報道,業內人士透露 SK 海力士在 6 月 16 至 20 日在美國夏威夷舉行的 VLSI 2024 峰會上發表了有關 3D DRAM 技術的最新研究論文。在這篇論文中,SK 海力士報告其五層堆疊的 3D DRAM 內存良率已達 56.1%,實驗中的 3D DRAM 展現出與目前 2D DRAM 相似的特性。據介紹,與傳統的 DRAM 水平排列記憶體單元不同,3D DRAM 垂直堆疊單元,可在相同空間內實現更高的密度。不過,SK海力士

大內存優化,電腦升級16g/32g內存速度沒什麼變化怎麼辦?

Jun 18, 2024 pm 06:51 PM

大內存優化,電腦升級16g/32g內存速度沒什麼變化怎麼辦?

Jun 18, 2024 pm 06:51 PM

對於機械硬碟、或SATA固態硬碟,軟體運轉速度的提升會有感覺,如果是NVME硬碟,可能感覺不到。一,註冊表導入桌面新建一個文字文檔,複製貼上如下內容,另存為1.reg,然後右鍵合併,並重新啟動電腦。 WindowsRegistryEditorVersion5.00[HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Control\SessionManager\MemoryManagement]"DisablePagingExecutive"=d

小米14Pro如何查看記憶體佔用?

Mar 18, 2024 pm 02:19 PM

小米14Pro如何查看記憶體佔用?

Mar 18, 2024 pm 02:19 PM

最近,小米發布了一款功能強大的高階智慧型手機小米14Pro,它不僅外觀設計時尚,而且擁有內在和外在的黑科技。這款手機擁有頂級的性能和出色的多工處理能力,讓用戶能夠享受快速且流暢的手機使用體驗。但效能也是會收到記憶體的影響的,很多用戶想要知道小米14Pro如何查看記憶體佔用,趕快來看看吧。小米14Pro如何查看記憶體佔用?小米14Pro查看記憶體佔用方法介紹開啟小米14Pro手機【設定】中的【應用程式管理】按鈕。查看已安裝的所有應用程式列表,瀏覽列表並找到你想查看的應用,點擊它進入應用程式詳細頁面。在應用程式詳細頁面中

電腦8g和16g記憶體差別大嗎? (電腦記憶體選8g還是16g)

Mar 13, 2024 pm 06:10 PM

電腦8g和16g記憶體差別大嗎? (電腦記憶體選8g還是16g)

Mar 13, 2024 pm 06:10 PM

新手用戶在購買電腦時,會好奇電腦記憶體8g和16g有什麼差別?應該選擇8g還是16g呢?針對這個問題,今天小編就來跟大家詳細說明一下。 電腦記憶體8g和16g的差別大嗎? 1、在一般家庭或是普通工作使用,8G運行記憶體可以滿足,因此在使用過程中8g和16g區別不大。 2、遊戲愛好者使用時候,目前大型遊戲基本上是6g起步,8g是最低標準。目前在螢幕是2k的情況下,更高解析度並不會帶來更高的幀數表現,因此對8g和16g也無較大差異。 3、對於音訊、視訊剪輯使用者來說,8g和16g會出現明顯區

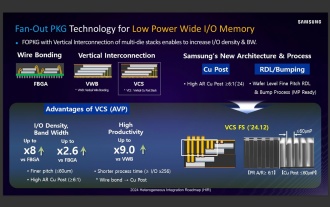

消息稱三星電子、SK 海力士堆疊式行動記憶體 2026 年後商業化

Sep 03, 2024 pm 02:15 PM

消息稱三星電子、SK 海力士堆疊式行動記憶體 2026 年後商業化

Sep 03, 2024 pm 02:15 PM

本站9月3日消息,韓媒etnews當地時間昨報道稱,三星電子和SK海力士的「類HBM式」堆疊結構行動記憶體產品將在2026年後實現商業化。消息人士表示這兩大韓國記憶體巨頭將堆疊式行動記憶體視為未來重要收入來源,並計劃將「類HBM記憶體」擴展到智慧型手機、平板電腦和筆記型電腦中,為端側AI提供動力。綜合本站先前報導,三星電子的此類產品叫做LPWideI/O內存,SK海力士則將這方面技術稱為VFO。兩家企業使用了大致相同的技術路線,即將扇出封裝和垂直通道結合在一起。三星電子的LPWideI/O內存位寬達512

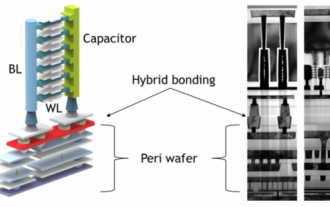

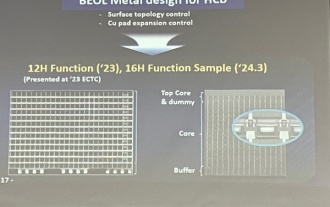

三星宣布完成 16 層混合鍵結堆疊製程技術驗證,預計在 HBM4 記憶體大面積應用

Apr 07, 2024 pm 09:19 PM

三星宣布完成 16 層混合鍵結堆疊製程技術驗證,預計在 HBM4 記憶體大面積應用

Apr 07, 2024 pm 09:19 PM

報告稱,三星電子的高層DaeWooKim表示,在2024年韓國微電子和封裝學會年會上,三星電子將完成採用16層混合鍵結HBM記憶體技術的驗證。據悉,這項技術已通過技術驗證。報告也稱,此次技術驗證將為未來若干年內的記憶體市場發展奠定基礎。 DaeWooKim表示,三星電子成功製造了基於混合鍵合技術的16層堆疊HBM3內存,該內存樣品工作正常,未來16層堆疊混合鍵合技術將用於HBM4內存量產。 ▲圖源TheElec,下同相較現有鍵合工藝,混合鍵結無需在DRAM記憶體層間添加凸塊,而是將上下兩層直接銅對銅連接,

已安裝的記憶體未顯示在Windows 11上

Mar 10, 2024 am 09:31 AM

已安裝的記憶體未顯示在Windows 11上

Mar 10, 2024 am 09:31 AM

如果您已經安裝了新的RAM,但它沒有顯示在您的Windows電腦上,本文將幫助您解決此問題。通常,我們會透過升級RAM來提高系統的效能。然而,系統效能也取決於其他硬件,如CPU、SSD等。升級RAM也可以提升您的遊戲體驗。有些使用者註意到安裝的內存在Windows11/10中沒有顯示。如果您遇到這種情況,您可以使用此處提供的建議。已安裝的記憶體未顯示在Windows11上如果您的Windows11/10PC上沒有顯示已安裝的RAM,以下建議將對您有所幫助。安裝的記憶體是否與您的電腦主機板相容?在BIO

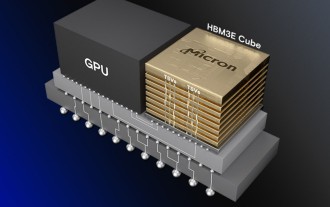

美光:HBM 記憶體消耗 3 倍晶圓量,明年產能基本預定完畢

Mar 22, 2024 pm 08:16 PM

美光:HBM 記憶體消耗 3 倍晶圓量,明年產能基本預定完畢

Mar 22, 2024 pm 08:16 PM

本站3月21日消息,美光在發布季度財報後舉行了電話會議。在該會議上美光CEO桑傑・梅赫羅特拉(SanjayMehrotra)表示,相對於傳統內存,HBM對晶圓量的消耗明顯更高。美光錶示,在同一節點生產同等容量的情況下,目前最先進的HBM3E內存對晶圓量的消耗是標準DDR5的三倍,並且預計隨著性能的提升和封裝複雜度的加劇,在未來的HBM4上這一比值將進一步提升。參考本站以往報道,這一高比值有相當一部分原因在HBM的低良率上。 HBM記憶體採用多層DRAM記憶體TSV連線堆疊而成,一層出現問題就意味著整個