組成cpu的元件包括哪些

組成cpu的元件包括「運算器」和「控制器」。 cpu(中央處理器)主要包括兩個部分:1、運算器,是指計算機中進行各種算術和邏輯運算操作的部件, 其中算術邏輯單元是中央處理核心的部分;2、控制器,是指依照預定順序改變主電路或控制電路的接線和改變電路中電阻值來控制電動馬達的啟動、調速、煞車與反向的主令裝置。

本教學操作環境:windows7系統、Dell G3電腦。

組成cpu的元件包括「運算器」和「控制器」。

中央處理器(central processing unit,簡稱CPU)作為電腦系統的運算與控制核心,是資訊處理、程式運作的最終執行單元。 CPU自產生以來,在邏輯結構、運作效率以及功能外延上取得了巨大發展。

中央處理器(CPU),是電子計算機的主要設備之一,電腦中的核心配件。其功能主要是解釋電腦指令以及處理電腦軟體中的資料。 CPU是電腦中負責讀取指令,對指令譯碼並執行指令的核心元件。 中央處理器主要包括兩個部分,即控制器、運算元,其對提高電腦的整體功能起著重要作用,能夠實現寄存控制、邏輯運算、訊號收發等多項功能的擴散,為提升電腦的效能奠定良好基礎。

運算器

運算子是指電腦中進行各種算術和邏輯運算運算的元件, 其中算術邏輯單元是中央處理核心的部分。

(1)算術邏輯單元(ALU)。算術邏輯單元是指能實現多組 算術運算與邏輯運算的組合邏輯電路,其是中央處理中的重要組成部分。算術邏輯單元的運算主要是進行二位元算術運算,如加法、減法、乘法。在運算過程中,算術邏輯單元主要以電腦指令集中執行算術與邏輯操作,通常來說,ALU能夠發揮直接讀入讀出的作用,具體體現在處理器控制器、記憶體及輸入輸出設備等方面,輸入輸出是建立在總線的基礎上實施。輸入指令包含一 個指令字,其中包括操作碼、格式碼等。

(2)中間暫存器(IR)。其長度為 128 位,其透過操作數來決定實際長度。 IR 在「進棧並取數」指令中發揮重要作用,在執行指令過程中,將ACC的內容傳送於IR,之後將操作數取到ACC,後將IR內容進棧。

(3)運算累加器(ACC)。目前的暫存器一般都是單累加器,其長度為128位元。對於ACC來說,可以將它看成可變長的累加器。在敘述指令過程中,ACC長度的表示一般都是將ACS的值作為依據,而ACS長度與 ACC 長度有著直接聯繫,ACS長度的加倍或減半也可以看作ACC長度加倍或減半。

(4)描述字暫存器(DR)。其主要應用於存放與修改描述字。 DR的長度為64位,為了簡化資料結構處理,使用描述字發揮重要作用。 [2]

(5)B暫存器。其在指令的修改中發揮重要作用,B 暫存器長度為32位,在修改位址過程中能保存位址修改量,主記憶體只能用描述字進行修改。指向陣列中的第一個元素就是描述字, 因此,存取陣列中的其它元素應需要用修改量。對於數字組成來說,其是由大小一樣的數據或者大小相同的元素組成的,且連續存儲,常見的訪問方式為向量描述字,因為向量描述字中的地址為字節地址,所以,在進行換算過程中,首先應進行基本地址的相加。對於換算工作來說,主要是由硬體自動實現,在這個過程中尤其要注意對齊,以免越出數組界限。

控制器

控制器是電腦的神經中樞,指揮全機中各個部件自動協調工作。在控制器的控制下,電腦能夠自動按照程式設定的步驟進行一系列操作,以完成特定任務。

控制器是指依照預定順序改變主電路或控制電路的接線和改變電路中電阻值來控制電動機的啟動、調速、煞車與反向的主令裝置。控制器由程式狀態暫存器PSR,系統狀態暫存器SSR, 程式計數器PC,指令暫存器等組成,其作為“決策機構”,主要任務就是發布命令,發揮著整個電腦系統操作的協調與指揮作用。控制的分類主要包括兩種,分別為組合邏輯控制器、微程式控制器,兩個部分都有各自的優點與不足。其中組合邏輯控制器結構相對較複雜,但優點是速度較快;微程式控制器設計的結構簡單,但在修改一條機器指令功能中,需對微程式的全部重編。

控制器內部的主要部件如下:

①指令暫存器:存放由記憶體取得的指令。

②譯碼器:將指令中的操作碼翻譯成控制訊號。

③時序節拍產生器:產生時序脈衝節拍訊號,使電腦有節奏、有次序地工作。

④操作控制部件:將控制訊號組合起來,控制各個部件完成對應的操作。

⑤指令計數器:計算並指出下一指令的位址。

擴展知識:CPU的工作原理

#馮諾依曼體系結構是現代電腦的基礎。在這個體系結構下,程式和資料統一存儲,指令和資料需要從相同儲存空間訪問,經由同一匯流排傳輸,無法重疊執行。根據馮諾依曼體系,CPU的工作分為以下 5 個階段:取指令階段、指令譯碼階段、執行指令階段、訪問次數和結果寫回。

取指令(IF,instruction fetch),即將一條指令從主記憶體取到指令暫存器的過程。程式計數器中的數值,用來指示目前指令在主記憶體中的位置。當 一條指令被取出後,程式計數器(PC)中的數值將根據指令字長度自動遞增。

指令譯碼階段(ID,instruction decode),取出指令後,指令譯碼器依照預定的指令格式,對取回的指令進行分割和解釋,識別區分出不同的指令類別以及各種取得操作數的方法。現代CISC處理器會將拆分已提高並行率和效率。

執行指令階段(EX,execute),具體實作指令的功能。 CPU的不同部分被連接起來,以執行所需的操作。

訪問訪問數階段(MEM,memory),根據指令需要存取主記憶體、讀取操作數,CPU得到操作數在主記憶體中的位址,並從主存中讀取該操作數用於運算。部分指令不需要存取主存,則可以跳過該階段。

結果寫回階段(WB,write back),作為最後一個階段,結果寫回階段把執行指令階段的運行結果資料「寫回」到某種儲存形式。結果資料一般會被寫到CPU的內部暫存器中,以便被後續的指令快速地存取;許多指令也會改變程式狀態字暫存器中標誌位的狀態,這些標誌位標識著不同的操作結果,可被用來影響程式的動作。

在指令執行完畢、結果資料寫回之後,若無意外事件(如結果溢位等)發生,電腦就從程式計數器中取得下一指令位址,開始新一輪的循環,下一個指令周期將順序取出下一指令。 許多複雜的CPU可以一次提取多個指令、解碼,並且同時執行。

更多相關知識,請造訪常見問題欄位!

以上是組成cpu的元件包括哪些的詳細內容。更多資訊請關注PHP中文網其他相關文章!

熱AI工具

Undresser.AI Undress

人工智慧驅動的應用程序,用於創建逼真的裸體照片

AI Clothes Remover

用於從照片中去除衣服的線上人工智慧工具。

Undress AI Tool

免費脫衣圖片

Clothoff.io

AI脫衣器

Video Face Swap

使用我們完全免費的人工智慧換臉工具,輕鬆在任何影片中換臉!

熱門文章

熱工具

記事本++7.3.1

好用且免費的程式碼編輯器

SublimeText3漢化版

中文版,非常好用

禪工作室 13.0.1

強大的PHP整合開發環境

Dreamweaver CS6

視覺化網頁開發工具

SublimeText3 Mac版

神級程式碼編輯軟體(SublimeText3)

在遊戲時,CPU利用率應該是多少?

Feb 19, 2024 am 11:21 AM

在遊戲時,CPU利用率應該是多少?

Feb 19, 2024 am 11:21 AM

遊戲因消耗大量資源而導致電腦運作速度變慢是常見現象。了解遊戲時CPU的使用率是至關重要的,這樣可以避免過度負荷。因此,掌握適當的CPU使用率是維持遊戲體驗流暢的關鍵。在本文中,我們將探討遊戲執行時間CPU應該達到的適當使用率。遊戲時的CPU使用率CPU使用率是指衡量處理器工作負載的重要指標,取決於CPU的效能規格。功率較大的CPU通常具有更高的使用率。擁有更多核心和執行緒的CPU可以提高系統的整體效能。多執行緒支援有助於充分發揮CPU的潛力。在遊戲中,CPU使用率取決於處理器的使用率,這會影響遊戲

Win11如何設定CPU效能全開

Feb 19, 2024 pm 07:42 PM

Win11如何設定CPU效能全開

Feb 19, 2024 pm 07:42 PM

許多使用者在使用Win11系統時發現電腦運作不夠流暢,想要提升CPU效能,但不清楚如何操作。以下將詳細介紹如何在Win11系統中設定CPU效能至最高,讓您的電腦更有效率。設定方法:1、右鍵點選桌面上的”此電腦”,選擇選項清單中的”屬性”。 2、進入到新的介面後,點選”相關連結”中的”高級系統設定”。 3、在開啟的視窗中,點選上方中的」進階」選項卡,接著點選」效能」下方中的&

遠端桌面無法驗證遠端電腦的身份

Feb 29, 2024 pm 12:30 PM

遠端桌面無法驗證遠端電腦的身份

Feb 29, 2024 pm 12:30 PM

Windows遠端桌面服務允許使用者遠端存取計算機,對於需要遠端工作的人來說非常方便。然而,當使用者無法連線到遠端電腦或遠端桌面無法驗證電腦身分時,會遇到問題。這可能是由網路連線問題或憑證驗證失敗引起的。在這種情況下,使用者可能需要檢查網路連線、確保遠端電腦是線上的,並嘗試重新連線。另外,確保遠端電腦的身份驗證選項已正確配置也是解決問題的關鍵。透過仔細檢查和調整設置,通常可以解決Windows遠端桌面服務中出現的這類問題。由於存在時間或日期差異,遠端桌面無法驗證遠端電腦的身份。請確保您的計算

2024 CSRankings全美電腦科學排名發布! CMU霸榜,MIT跌出前5

Mar 25, 2024 pm 06:01 PM

2024 CSRankings全美電腦科學排名發布! CMU霸榜,MIT跌出前5

Mar 25, 2024 pm 06:01 PM

2024CSRankings全美電腦科學專業排名,剛剛發布了!今年,全美全美CS最佳大學排名中,卡內基美隆大學(CMU)在全美和CS領域均名列前茅,而伊利諾大學香檳分校(UIUC)則連續六年穩定地位於第二。佐治亞理工學院則排名第三。然後,史丹佛大學、聖迭戈加州大學、密西根大學、華盛頓大學並列世界第四。值得注意的是,MIT排名下跌,跌出前五名。 CSRankings是由麻省州立大學阿姆赫斯特分校電腦與資訊科學學院教授EmeryBerger發起的全球院校電腦科學領域排名計畫。該排名是基於客觀的

如何增加電腦CPU的時脈頻率

Feb 20, 2024 am 09:54 AM

如何增加電腦CPU的時脈頻率

Feb 20, 2024 am 09:54 AM

電腦CPU如何超頻隨著科技的不斷進步,人們對於電腦效能的需求也越來越高。而一個有效的提升電腦效能的方法就是透過超頻(overclocking)來增加CPU的工作頻率。超頻可以使CPU更快地處理數據,從而提供更高的運算能力。那麼,電腦CPU如何超頻呢?以下將為大家介紹超頻的基本原理和具體操作方法。首先,讓我們來了解一下超頻的原理。 CPU的工作頻率是由主機板上的晶振

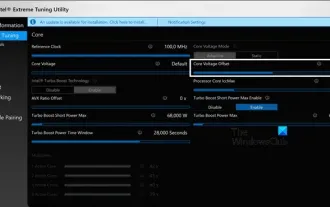

如何使用Intel XTU對CPU進行欠壓與超頻

Feb 19, 2024 am 11:06 AM

如何使用Intel XTU對CPU進行欠壓與超頻

Feb 19, 2024 am 11:06 AM

英特爾XTU是一款強大的應用程序,可讓您輕鬆管理電腦的效能。您可以透過調整CPU電壓來解決過熱問題,或透過超頻來提升效能。在這篇文章中,我們將探討如何利用英特爾XTU來最佳化電腦的效能,無論是調整電壓或進行超頻。欠壓和超頻對CPU有什麼作用?在我們繼續學習如何對CPU進行欠壓和超頻之前,首先必須了解它們是什麼。欠電壓指的是逐漸降低CPU所需的電壓。這個過程有助於減少熱量排放,因為高電壓會導致更高的溫度。透過減少CPU的電壓供應,可以有效降低溫度。如果筆記本在發熱後開始減速,應及時解決問題

WIN10服務主機太佔cpu的處理操作過程

Mar 27, 2024 pm 02:41 PM

WIN10服務主機太佔cpu的處理操作過程

Mar 27, 2024 pm 02:41 PM

1.首先我們右鍵點選任務列空白處,選擇【任務管理器】選項,或右鍵開始徽標,然後再選擇【任務管理器】選項。 2.在開啟的任務管理器介面,我們點選最右邊的【服務】選項卡。 3.在開啟的【服務】選項卡,點選下方的【開啟服務】選項。 4.在開啟的【服務】窗口,右鍵點選【InternetConnectionSharing(ICS)】服務,然後選擇【屬性】選項。 5.在開啟的屬性窗口,將【開啟方式】修改為【禁用】,點選【應用程式】後點選【確定】。 6.點選開始徽標,然後點選關機按鈕,選擇【重啟】,完成電腦重啟就行了。

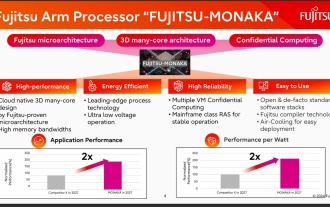

144 核心,3D 堆疊 SRAM:富士通詳細介紹下一代資料中心處理器 MONAKA

Jul 29, 2024 am 11:40 AM

144 核心,3D 堆疊 SRAM:富士通詳細介紹下一代資料中心處理器 MONAKA

Jul 29, 2024 am 11:40 AM

本站7月28日消息,根據外媒TechRader報道,富士通詳細介紹了計劃於2027年出貨的FUJITSU-MONAKA(以下簡稱MONAKA)處理器。 MONAKACPU基於「雲端原生3D眾核」架構,採用Arm指令集,面向資料中心、邊緣與電信領域,適用於AI運算,能實現大型主機層級的RAS1。富士通表示,MONAKA將在能源效率和性能方面實現飛躍:得益於超低電壓(ULV)製程等技術,該CPU可實現2027年競品2倍的能效,冷卻無需水冷;此外該處理器的應用性能也可達對手2倍。在指令方面,MONAKA配備的向量