cache是什麼記憶體?

cache叫做高速緩衝記憶體,是介於中央處理器和主記憶體之間的高速小容量記憶體,一般由高速SRAM構成;這種局部記憶體是面向CPU的,引進它是為減少或消除CPU與記憶體之間的速度差異對系統效能帶來的影響。 Cache容量小但速度快,記憶體速度較低但容量大,透過最佳化調度演算法,系統的效能會大幅提升。

本教學操作環境:windows7系統、Dell G3電腦。

cache是什麼記憶體

Cache記憶體:電腦中為高速緩衝記憶體,位於CPU和主記憶體DRAM(Dynamic Random Access Memory )之間,規模較小,但速度很高的記憶體,通常由SRAM(Static Random Access Memory靜態記憶體)組成。

如圖3.28所示,cache是介於CPU和主記憶體M2之間的小容量記憶體,但存取速度比主存快,容量遠小於主存。 cache 能高速地向CPU提供指令和數據,從而加快了程式的執行速度。從功能上看,它是主記憶體的緩衝記憶體,由高速的SRAM組成。為追求高速,包括管理在內的全部功能由硬體實現,因而對程式設計師是透明的。

目前,隨著半導體裝置整合度的進步提高,可以將小容量的cache與CPU 整合到同一晶片中,其工作速度接近CPU的速度,從而組成兩級以上的cache系統。

cache的功能

Cache的功能是提高CPU資料輸入輸出的速率。 Cache容量小但速度快,記憶體速度較低但容量大,透過最佳化調度演算法,系統的效能會大大改善,彷彿其儲存系統容量與記憶體相當且存取速度近似Cache。

CPU的速度遠高於內存,當CPU直接從內存中訪問數據時要等待一定時間週期,而Cache則可以保存CPU剛用過或循環使用的一部分數據,如果CPU需要再次使用該部分數據時可從Cache中直接調用,這樣就避免了重複訪問數據,減少了CPU的等待時間,從而提高了系統的效率。 Cache又分為L1Cache(一級快取)和L2Cache(二級快取),L1Cache主要是整合在CPU內部,而L2Cache整合在主機板上或是CPU上。

cache的基本原則

cache除包含SRAM外,還要有控制邏輯。若cache在CPU晶片外,它的控制邏輯一般與主記憶體控制邏輯合成在一起,稱為主記憶體/chace控制器;若cache在CPU內,則由CPU提供它的控制邏輯。

CPU與cache之間的資料交換是以字為單位,而cache與主記憶體之間的資料交換是以區塊為單位。一個塊由若干字組成,是定長的。當CPU讀取記憶體中一個字時,便發出此字的記憶體位址到cache和主記憶體。此時cache控制邏輯依據位址判斷此字目前是否在cache中:若是,則cache命中,此字立即傳送給CPU;若非,則cache缺失(未命中),用主存讀週期把此字從主存讀出送到CPU,同時,把含有這個字的整個資料塊從主記憶體讀出送到cache中。

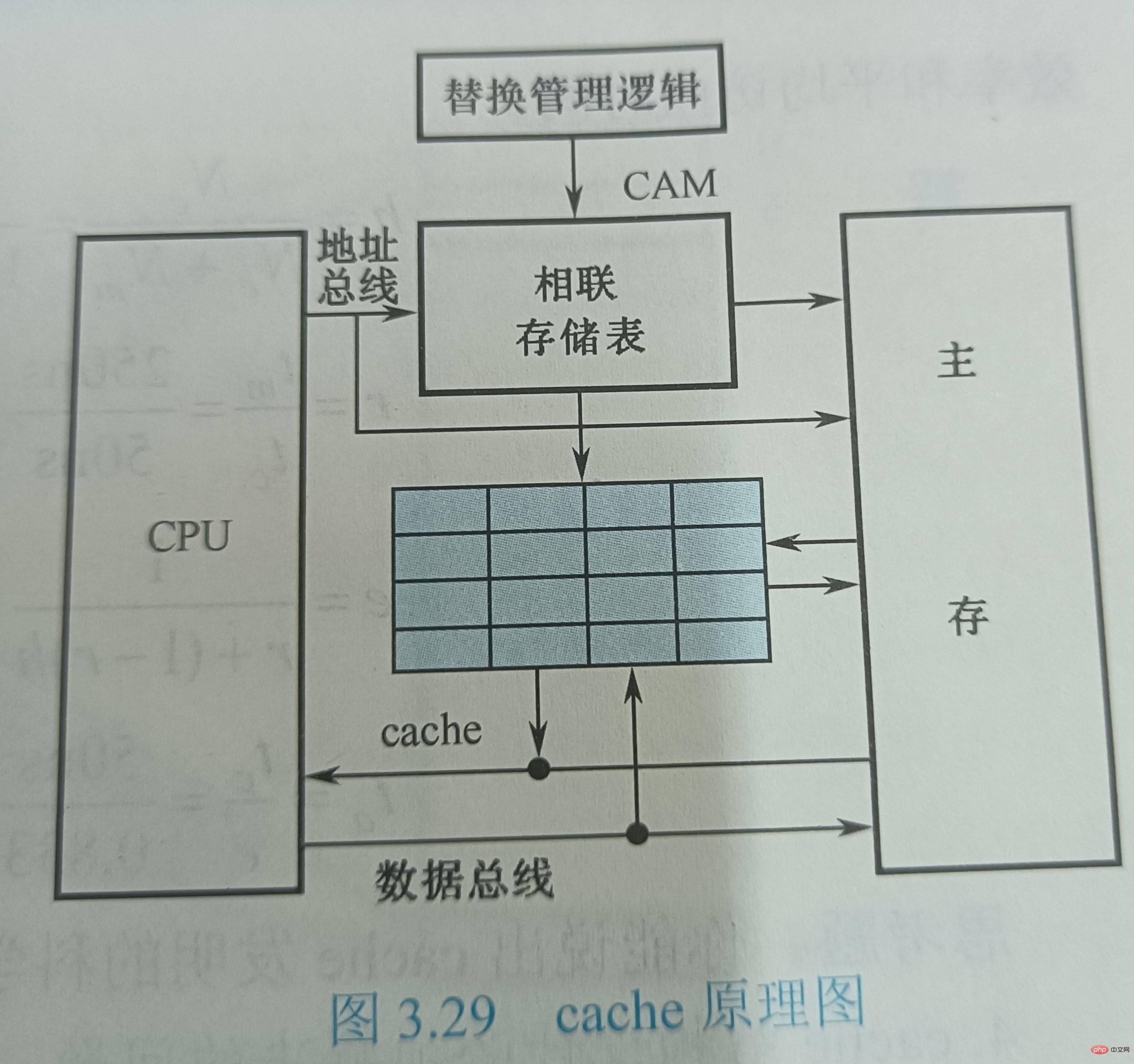

圖3.29顯示了cache的原理圖。假設cache讀出時間為50ns,主存讀出時間為250ns。儲存系統是模組化的,主記憶體中每個8K模組和容量16字的cache相聯繫。 cache分為4行,每行4個字(W)。分配給cache的位址存放在一個相聯記憶體CAM中,它是按內容尋址的記憶體。當CPU執行存取指令時,就把所要存取的字的位址送到CAM;如果W不在cache中,則將W從主記憶體傳送到CPU。同時,把包含W的由前後相繼的4個字所組成的一行資料送入cache,替換原來cache中的一行資料。在這裡,由始終管理cache使用情況的硬體邏輯電路來實現替換演算法。

cache的命中率

從CPU來看,增加cache的目的,就是在效能上讓主記憶體的平均讀出時間盡可能接近cache的讀出時間。為了達到這個目的,在所有的記憶體存取中由cache滿足CPU需求的部分應佔很高的比例,即cache的命中率應接近1。由於程式存取的局部性,實現這個目標是可能的。

在一個程式執行期間,設Nc表示cache完成存取的總次數,Nₘ表示主記憶體完成存取的總次數,h定義為命中率,則有h=Nc/(Nc+Nₘ)

若tc表示命中時的cache存取時間,tₘ表示未命中時的主記憶體存取時間,1-h表示未命中率(缺失率),則cache/主記憶體系統的平均存取時間tₐ為

tₐ=htc+(1−h)tₘ

我們追求的目標是,以較小的硬體代價使cache/主存系統的平均存取時間tₐ越接近 tc越好。設 r=tₘ/tc表示主記憶體與cache的訪問時間之比,e表示訪問效率,則有

e=tc/ta=tc/(htc+(1−h)tm)=1/(h+(1−h)r)=1/(r+(1−r)h)

由此式看出,為提高訪問效率,命中率h越接近1越好。 r值以5~10為宜,不宜太大。

命中率h與程式的行為、cache的容量、組織方式、區塊的大小有關。

cache結構設計必須解決的問題

#從cache的基本運作原理可以看出, cache的設計需要遵循兩個原則:一是希望cache的命中率盡可能高,實際應接近於1;二是希望cache對CPU而言是透明的,即不論是否有cache, CPU訪存的方法都是一樣的,軟體不需增加任何指令就可以存取cache。解決了命中率和透明性問題,就CPU存取的角度而言,記憶體將具有主記憶體的容量和接近cache的速度。為此,必須增加一定的硬體電路完成控制功能,也就是cache控制器。

在設計cache結構時,必須解決幾個問題:①主存的內容調入cache時如何存放?②訪存時如何找到cache中的信息?③當cache空間不足時如何替換cache中已有的內容?④需要寫入操作時如何改寫cache的內容?

其中,前兩個問題是相互關聯的,即如何將主存資訊定位在cache中,如何將主存位址變換為cache位址。與主記憶體相比, cache的容量很小,它保存的內容只是主記憶體內容的子集,且cache與主記憶體的資料交換是以區塊為單位。為了把主存塊放到cache中,必須應用某種方法把主記憶體位址定位到cache中,稱為位址對映。 「映射」一詞的物理意義是確定位置的對應關係,並用硬體來實現。這樣當CPU存取記憶體時,它所給的一個字的記憶體位址就會自動變換成cache的位址,也就是cache位址變換。

cache替換問題主要是選擇和執行替換演算法,以便在cache不命中時取代cache中的內容。最後一個問題涉及cache的寫入操作策略,重點是在更新時保持主記憶體與cache的一致性。

更多相關知識,請造訪常見問題欄位!

以上是cache是什麼記憶體?的詳細內容。更多資訊請關注PHP中文網其他相關文章!

熱AI工具

Undresser.AI Undress

人工智慧驅動的應用程序,用於創建逼真的裸體照片

AI Clothes Remover

用於從照片中去除衣服的線上人工智慧工具。

Undress AI Tool

免費脫衣圖片

Clothoff.io

AI脫衣器

AI Hentai Generator

免費產生 AI 無盡。

熱門文章

熱工具

記事本++7.3.1

好用且免費的程式碼編輯器

SublimeText3漢化版

中文版,非常好用

禪工作室 13.0.1

強大的PHP整合開發環境

Dreamweaver CS6

視覺化網頁開發工具

SublimeText3 Mac版

神級程式碼編輯軟體(SublimeText3)

熱門話題

記憶體中存取速度最快的是什麼

Jul 26, 2022 am 10:54 AM

記憶體中存取速度最快的是什麼

Jul 26, 2022 am 10:54 AM

記憶體中存取速度最快的是「內部記憶體」;電腦中的記憶體採用層次結構,依照速度快慢排列依序為內記憶體、高速緩衝記憶體、電腦的主記憶體、大容量磁碟,其中記憶體一般分為RAM隨機存取記憶體和ROM只讀記憶體。

入職後,我才明白什麼叫Cache

Jul 31, 2023 pm 04:03 PM

入職後,我才明白什麼叫Cache

Jul 31, 2023 pm 04:03 PM

事情其實是這樣的,當時領導者交給我一個perf硬體效能監視的任務,在使用perf的過程中,輸入指令perf list,我看到了以下資訊:我的任務就要讓這些cache事件能夠正常計數,但重點是,我根本不知道這些misses、loads是什麼意思。

cpu能直接存取內記憶體上的資料嗎

Nov 25, 2022 pm 02:02 PM

cpu能直接存取內記憶體上的資料嗎

Nov 25, 2022 pm 02:02 PM

能直接存取。內存儲器又稱內存,是外存與CPU溝通的橋樑,電腦中所有程式的運作都是在記憶體中進行。記憶體的作用是用於暫時存放CPU中的運算數據,以及與硬碟等外部記憶體交換的資料。只要電腦運行,作業系統就會把需要運算的資料從記憶體調到CPU中運算;當運算完成後,CPU再將結果傳送出來,記憶體的運作也決定了電腦的穩定運作。

計算機具有很強的記憶能力的基礎是什麼

Jul 09, 2021 pm 03:59 PM

計算機具有很強的記憶能力的基礎是什麼

Jul 09, 2021 pm 03:59 PM

電腦具有很強的記憶能力的基礎是:足夠容量的儲存裝置。記憶體可分為內存和外存,它們使得計算機具有強大的記憶功能,可以存儲大量的信息,這些信息,不僅包括各類數據信息,還包括加工這些數據的程序。

電腦系統中的記憶體系統是指什麼

Jul 22, 2022 pm 02:23 PM

電腦系統中的記憶體系統是指什麼

Jul 22, 2022 pm 02:23 PM

記憶體系統是指電腦中由存放程式及資料的各種儲存設備、控制部件及管理資訊調度的設備(硬體)及演算法(軟體)所組成的系統。儲存系統提供寫入和讀出電腦工作所需的資訊(程式和資料)的能力,實現電腦的資訊記憶功能。儲存系統的層次結構可分為5級:暫存器組、高速緩存Cache、主記憶體、虛擬記憶體、外部記憶體。

u盤是哪個國家發明的

Oct 09, 2022 pm 02:26 PM

u盤是哪個國家發明的

Oct 09, 2022 pm 02:26 PM

u盤是中國發明的,朗科公司是U盤的全球發明者。 2002年7月,朗科公司的「用於資料處理系統的快閃電子式外儲存方法及其裝置」獲得國家智慧財產權局正式授權,該專利填補了中國電腦儲存領域20年來發明專利的空白;2004年12月7日,朗科獲得美國國家專利局正式授權的隨身碟基礎發明專利。

使用cache可以提高計算機運行速度這是因為什麼

Dec 09, 2020 am 11:28 AM

使用cache可以提高計算機運行速度這是因為什麼

Dec 09, 2020 am 11:28 AM

使用cache可以提高電腦運行速度這是因為Cache縮短了CPU的等待時間。 Cache是位於CPU和主記憶體DRAM之間,規模較小,但速度很高的記憶體。 Cache的功能是提高CPU資料輸入輸出的速率;Cache容量小但速度快,記憶體速度較低但容量大,透過最佳化調度演算法,系統的效能會大幅提升。

cache是什麼記憶體?

Nov 25, 2022 am 11:48 AM

cache是什麼記憶體?

Nov 25, 2022 am 11:48 AM

cache叫做高速緩衝記憶體,是介於中央處理器與主記憶體之間的高速小容量記憶體,一般由高速SRAM構成;這種局部記憶體是面向CPU的,引進它是為減少或消除CPU與記憶體之間的速度差異對系統性能帶來的影響。 Cache容量小但速度快,記憶體速度較低但容量大,透過最佳化調度演算法,系統的效能會大幅提升。